卓顶精文最新组合逻辑电路课后答案doc文档格式.docx

卓顶精文最新组合逻辑电路课后答案doc文档格式.docx

- 文档编号:14399058

- 上传时间:2022-10-22

- 格式:DOCX

- 页数:27

- 大小:723.92KB

卓顶精文最新组合逻辑电路课后答案doc文档格式.docx

《卓顶精文最新组合逻辑电路课后答案doc文档格式.docx》由会员分享,可在线阅读,更多相关《卓顶精文最新组合逻辑电路课后答案doc文档格式.docx(27页珍藏版)》请在冰豆网上搜索。

P1P2

000

00

001

10

010

011

01

100

101

110

111

11

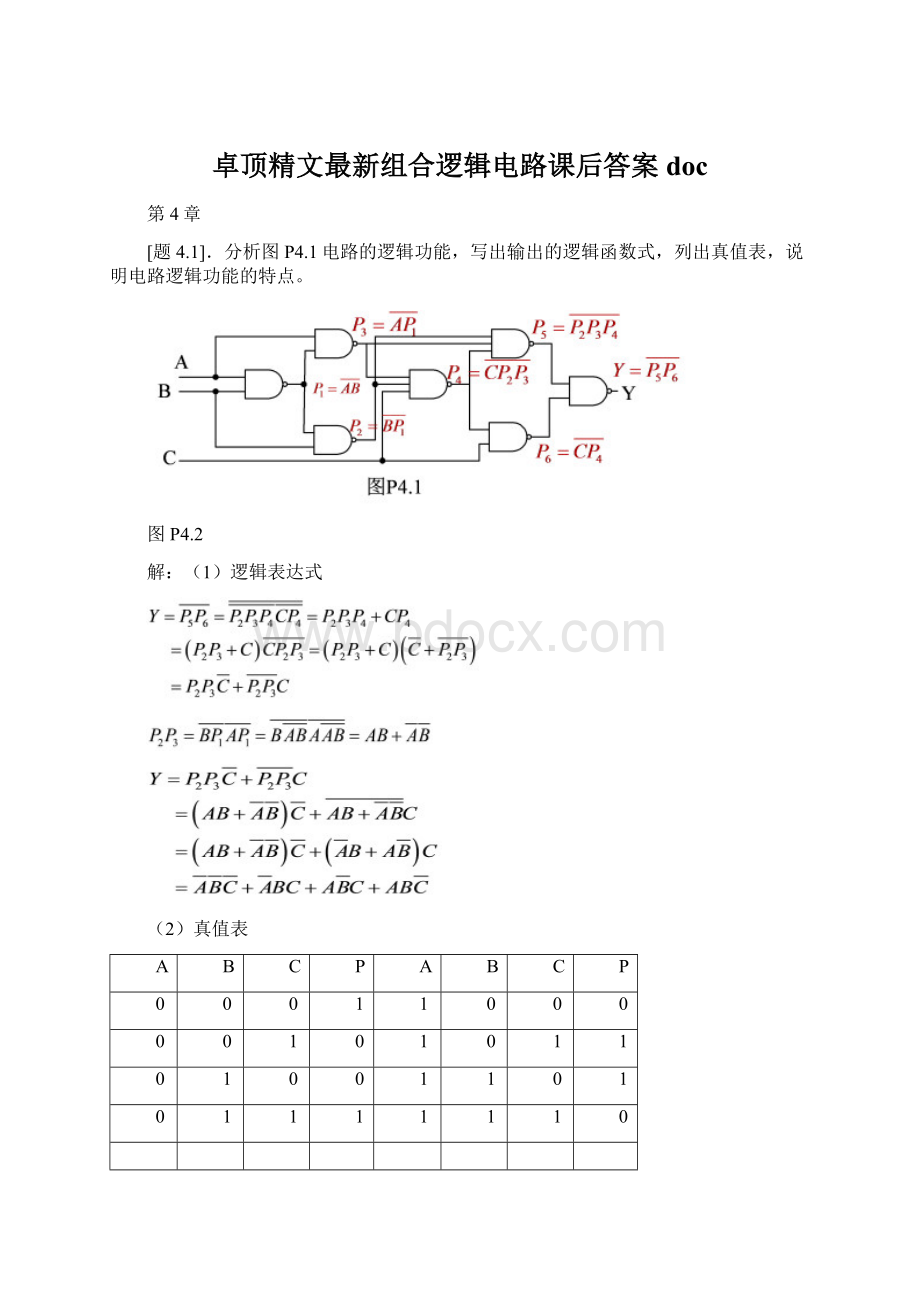

由真值表可知:

电路构成全加器,输入A、B、C为加数、被加数和低位的进位,P1为“和”,P2为“进位”。

[题4.4]图P4.4是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,P1~P4的逻辑式,列出真值表。

(1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,

(2)COMP=0、Z=0时,

P1=A1,P2=A2,P3=A3,P4=A4。

、COMP=1、Z=0时的真值表

十进制数

A4A3A2A1

P4P3P2P1

0000

1001

8

1000

0001

9

2

0010

0111

伪

码

1010

3

0011

0110

1011

4

0100

0101

1100

5

1101

6

1110

7

1111

COMP=0、Z=0的真值表从略。

[题4.5]用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解]题4.5的真值表如表A4.5所示,逻辑图如图A4.5(b)所示。

由表4.5可写输出逻辑函数式

填卡诺图,如图A4.5(a)所示合并最小项,得最简与—或式

[题4.6]有一水箱由大、小两台泵ML和MS供水,如图P4.6所示。

水箱中设置了3个水位检测元件A、B、C。

水面低于检测元件时,检测元件给出高电平;

水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C点时水泵停止工作;

水位低于C点而高于B点时MS单独工作;

水位低于B点而高于A点时ML单独工作;

水位低于A点时ML和MS同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解]题4.6的真值表如表A4.6所示。

表A4.6

MSML

×

真值表中的、、、为约束项,利用卡诺图图A4.4(a)化简后得到:

,(MS、ML的1状态表示工作,0状态表示停止)。

逻辑图如图A4.6(b)。

[题4.7]设计一个代码转换电路,输入为4位二进制代码,输出为4位循环码。

可以采用各种逻辑功能的门电路来实现。

[解]题4.7的真值表如表A4.7所示。

表A4.7

二进制代码

循环码

A3

A2

A1

A0

P3

P2

P1

P0

由真值表得到,,,

逻辑图如图A4.7所示。

[题4.8]试画出用4片8线-3线优先编码器74LS148组成32线-5线优先编码器的逻辑图。

74LS148的逻辑图见图4.3.3。

允许附加必要的门电路。

[解]以表示32个低电平有效的编码输入信号,以D4D3D2D1D0表示输出编码,可列出D4、D3与PEG4PEG3PEG2PEG1关系的真值表。

如表A4.8所示。

表A4.8

工作的芯片号

PEG4

PEG3

PEG2

PEG1

D4

D3

(4)

(3)

(2)

(1)

从真值表得到

逻辑电路图略。

[题4.9]某医院有一、二、三、四号病室4间,每室设有呼叫按钮,同时在护士值班室内对应地装有一号、二号、三号、四号4个指示灯。

现要求当一号病室的铵钮按下时,无论其他病室内的按钮是否按下,只有一号灯亮。

当一号病室的按钮没有按下,而二号病室的按钮按下时,无论三、四号病室的按钮是否按下,只有二号灯亮。

当一、二号病室的按钮都未按下而三号病室的按钮按下时,无论四号病室的铵钮是否按下,只有三号灯亮。

只有在一、二、三号病室的按钮均未按下,而四号病室的按钮按下时,四号灯才亮。

试分别用门电路和优先编码器74LS148及门电路设计满足上述控制要求的逻辑电路,给出控制四个指示灯状态的高、低电平信号。

74LS148的逻辑图如图P4.9所示,其功能表如表P4.9所示。

输入

输出

11111111

01111

011111

0111111

01111111

表P4.974LS148的功能表

设一、二、三、四号病室分别为输入变量,当其值为0时,表示呼叫按钮按下,为1时表示没有按呼叫铵钮,将它们接到74HC148的输入端后,便在74HC148的输出端得到对应的输出编码;

设一、二、三、四号病室呼叫指示灯分别为Z1、Z2、Z3、Z4,其值为1指示灯亮,否则灯不亮,列出真值表,如表A4.9示。

表A4.9

Z1Z2Z3Z4

0×

10×

110×

将该真值表与表P4.9对照可知,在74LS148中应接1,。

则

由上式可得出用74LS148和门电路实现题目要求的电路如图A4.9所示。

[题4.10]写出图P4.10中Z1、Z2、Z3的逻辑函数式,并化简为最简的与-或表达式。

74LS42为拒伪的二-十进制译码器。

当输入信号A3A2A1A0为0000~1001这10种状态时,输出端从依次给出低电平,当输入信号为伪码时,输出全为1。

利用伪码用卡诺图化简,得:

约束条件:

[题4.11]画出用两片4线-16线译码器74LS154组成5线-32线译码的接线图。

图P4.11是74LS154的逻辑框图,图中是两个控制端(亦称片选端)译码器工作时应使同时为低电平,输入信号A3、A2、A1、A0为0000~1111这16种状态时,输出端从依次给出低电平输出信号。

[解]电路如图A4.11所示。

当A4=0时,片

(1)工作,对应输出低电平;

当A4=1时,片

(2)工作,对应输出低电平。

[题4.12]试画出用3线-8线译码器74LS138和门电路产生多输出逻辑函数的逻辑图(74LS138逻辑图如图P4.12所示,功能表如表P4.12所示)。

表P4.1274LS138功能表

允许

选择

[解]令A=A2,B=A1,C=AO。

将P1P2P3写成最小项之和形式,并变换成与非-与非形式。

用外加与非门实现之,如图A4.12所示。

[题4.13]画出用4线-16线译码器74LS154(参见题4.11)和门电路产生如下多输出逻辑函数的逻辑图。

电路图如图A4.13所示。

[题4.14]用3线-8线译码器74LS138和门电路设计1位二进制全减器电路。

输入为被减数、减数和来自低位的借位;

输出为两数之差及向高位的借位信号。

[解]设ai为被减数,bi为减数,ci-1为来自低位的借位,

首先列出全减器真值表A4.14,然后将Di,Ci表达式写成非-与非形式。

最后外加与非门实现之。

由全减器真值表知:

全减器真值表

同理可知

令ai=A2,bi=A1,ci-1=A0。

电路如图A4.14所示。

[题4.15]试用两片双4选1数据选择器74LS153和3线-8线译码器74LS138接成16选1数据选择器。

74LS153的逻辑图见图4.4.24,74LS138的逻辑图见图4.4.22。

[解]见图A4.13。

[题4.16]分析图P4.16电路,写出输出Z的逻辑函数式,并化简。

CC4512为8选1数据选择器,它的逻辑功能表如表P4.16所示。

表P4.1

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 卓顶精文 最新 组合 逻辑电路 课后 答案 doc

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx