数电习题及答案Word文件下载.docx

数电习题及答案Word文件下载.docx

- 文档编号:14461588

- 上传时间:2022-10-23

- 格式:DOCX

- 页数:41

- 大小:805.58KB

数电习题及答案Word文件下载.docx

《数电习题及答案Word文件下载.docx》由会员分享,可在线阅读,更多相关《数电习题及答案Word文件下载.docx(41页珍藏版)》请在冰豆网上搜索。

进位输出

S0

S1

S2

S3

S4

000

001

010

011

100

1

(3)求状态方程

(4)驱动方程(5)逻辑图(略)

[题7.1]分析图P7.1所示的时序电路的逻辑功能,写出电路驱动方程、状态转移方程和输出方程,画出状态转换图,并说明时序电路是否具有自启动性。

触发器的驱动方程

触发器的状态方程

输出方程

状态转换图如图A7.1所示

所以该电路的功能是:

能自启动的五进制加法计数器。

[题7.3]试分析图P7.3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并检查电路能否自启动。

驱动方程

输出方程

状态方程

状态转换图如图A7.3所示

功能:

所以该电路是一个可控的3进制计数器。

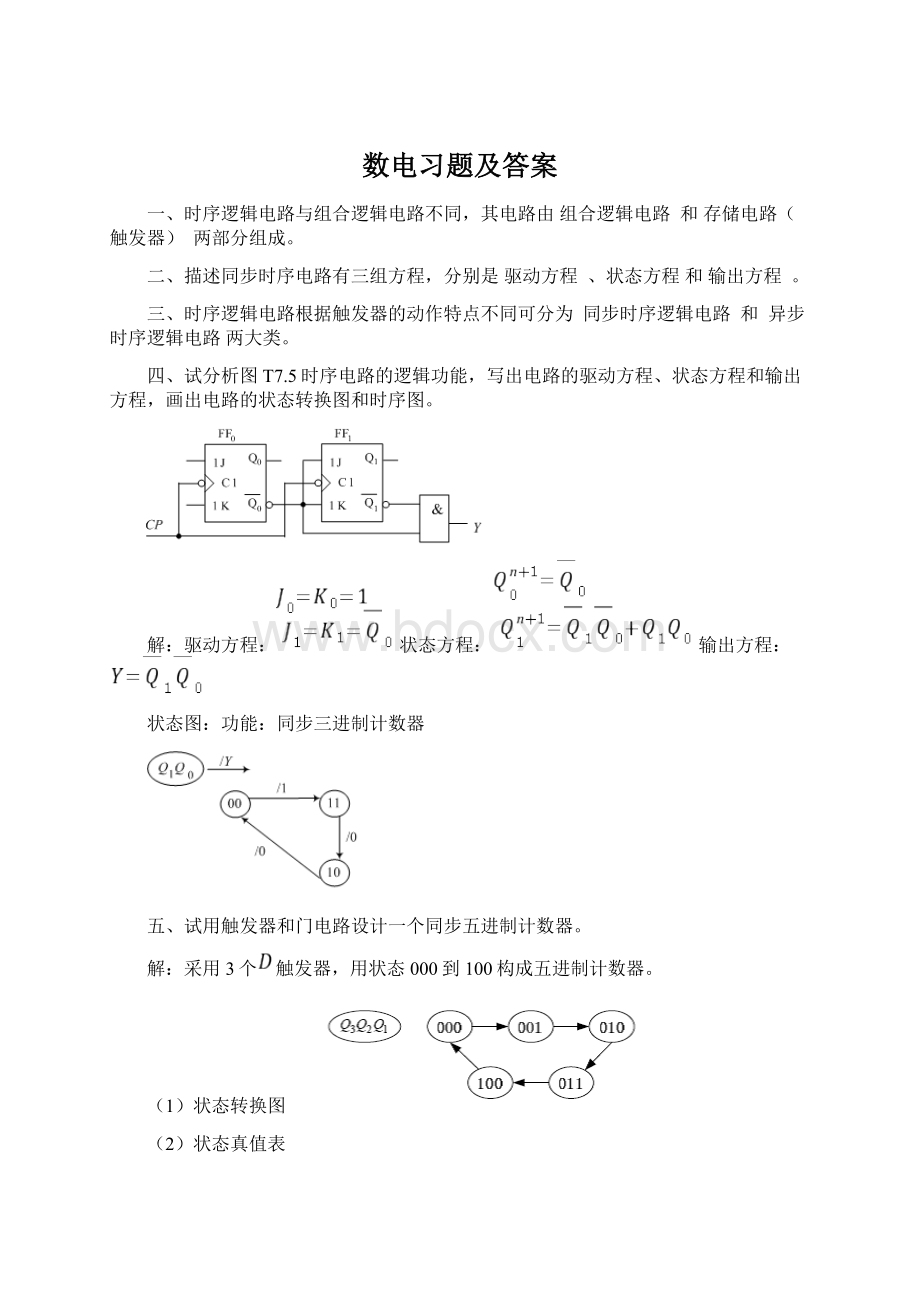

[题7.5]分析图P7.5时序电路的功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并检查电路能否自启动。

输出方程

求状态方程

得电路的状态转换表如表A7.5所示

表A7.5

输入

次态

输出

S

Y1Y2

101

110

111

00

01

11

画出电路的状态转换图如图A7.5所示

图A7.5

逻辑功能:

这是一个有两个循环的电路,时实现八进制计数、为进位输出,时实现六进制计数、为进位输出。

当时存在2个无效态110、111,但未形成循环,电路能自启动。

[题7.6]试用触发器和门电路设计一个同步六进制加法计数器。

采用3个触发器,用状态000到101构成六进制计数器,设电路的输出为。

根据题意可列电路状态转换表如表A7.6所示

S5

由状态表求得电路的次态和输出的卡诺图如图A7.6(a)所示,其中斜线下方是输出端的值,状态101、110、111作无效态处理,用×

表示。

由卡诺图得电路的状态方程和输出方程

由状态方程可得电路的驱动方程

最后设计电路逻辑图如图A7.6(b)

[题7.7]用触发器和门电路设计一个十一进制计数器,并检查设计的电路能否自启动。

用4个下降沿触发器设计,设电路的进位输出为,可列电路的状态转换表如表A7.7

表A7.7

的

顺序

触发器的状态

输出

2

3

4

5

6

7

8

9

10

11

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

电路图略

[题7.8]试用触发器设计一个可控型计数器,其状态转换图如图P7.8所示,,实现8421码六进制计数;

,实现循环码六进制计数,并检验电路能否自启动。

本例所设计的计数器有一控制变量存在,设计时将控制变量作为一个逻辑变量画入电路的次态卡诺图中。

设电路的进位输出为,根据题意可画出次态卡诺图如图A7.8所示

图中上面两行为时的状态与次态的内容,下面两行为的状态与次态的内容。

电路作8421码六进制加法计数器时,110和111为无效状态视为无关项,电路作循环码路进制计数器时,000和100为无效态视为无关项。

电路的驱动方程和输出方程(设计时需用3个触发器)

逻辑图略

[题7.12]四相八拍步进电机脉冲分配电路的状态转换图如图P7.12所示。

试用触发器和部分门电路实现之,画出相应的逻辑电路图。

用触发器、、、的状态来表示步进电机四相的状态,根据题意可求得四相八拍脉冲分配电路的驱动方程为

逻辑电路图略

1.半导体存储器从存、取功能上可以分为只读存储器和随机存取存储器两大类。

5.半导体存储器中,ROM属于组合逻辑电路,而RAM可归属于时序逻辑电路。

习题

[题11.1]假设存储器的容量为256ⅹ8位,则地址代码应取几位。

8。

一、可以用来暂时存放数据的器件叫寄存器。

二、移位寄存器除寄存数据功能外,还有移位功能。

三、某寄存器由触发器构成,有4位代码要存储,此寄存器必须由4个触发器构成。

四、一个四位二进制加法计数器,由0000状态开始,问经过18个输入脉冲后,此计数器的状态为0010。

五、级环形计数器的计数长度是,级扭环形计数器的计数长度是。

六、集成计数器的模值是固定的,但可以用清零法和置数法来改变它们的模值。

七、通过级联方式,把两片4位二进制计数器74161连接成为8位二进制计数器后,其最大模值是256;

将3片4位十进制计数器74160连接成12位十进制计数器后,其最大模值是4096。

八、设计模值为38的计数器至少需要6个触发器。

[题8.3]分析图P8.3的计数器电路,画出电路的状态转换图,说明这是多少进制计数器。

十六进制计数器74161的功能表如表8.2.2所示。

采用同步预置数法,。

计数器起始状态为0011,结束状态为1010,所以该计数器为八进制加法计数器。

状态转换图略。

[题8.4]分析图P8.4的计数器电路,说明这是多少进制的计数器,并画出电路的状态转换图。

十进制计数器74160的功能表如表8.2.6所示。

该计数器采用异步清零法,。

计数器起始状态为0000,结束状态为1000(状态1001只是维持瞬间),所以该计数器为九进制加法计数器。

[题8.5]试用十六进制计数器74161设计十三进制计数器,标出输入、输出端。

可以附加必要的门电路。

74161的功能表如表8.2.2所示。

[题8.6]分析图P8.6的计数器在和时各为几进制计数器,并画出相应的状态转换图。

解:

该计数器采用同步预置数法,。

所以

时:

起始状态为0010,结束状态为1100,所以该计数器为十一进制加法计数器。

起始状态为0100,结束状态为1100,所以该计数器为九进制加法计数器。

状态图略。

[题8.7]分析图P8.7的计数器在和时各为几进制,并画出相应的状态转换图。

该计数器采用同步预置数法。

时:

起始状态为0000,结束状态为1010,所以该计数器为十一进制加法计数器。

起始状态为0000,结束状态为0111,所以该计数器为八进制加法计数器。

[题8.8]设计一个可控进制的计数器,当输入控制变量时为13进制计数器,时为7进制计数器。

标出计数器的输入端和进位输出端。

电路采用同步预置数法。

电路逻辑图如图A8.8所示

[题8.11]试分析图P8.11计数器电路的分频比(即和的频率比)。

74LS1610的功能表如表8.2.2所示。

两片计数器接成并行进位方式,其中

第1片74160计数,起始状态为0000,结束状态为1001,为十进制计数器。

第2片74160计数,起始状态为0110,结束状态为1001,为四进制计数器。

所以该计数电路的分频比

[题8.12]试用同步4位二进制计数器74LS161芯片和必要的门电路来组成一个125进制加法计数器。

要求标出计数器的输入端和进位输出端;

画出逻辑连接图。

计数的起始状态为00000000,结束状态为01111101,电路逻辑图如图A8.12所示

[题8.13]设计一个序列信号发生器电路,使之在一系列信号作用下能周期性地输出“11010010111”的序列信号。

根据题意电路可由计数器+组合输出电路两部分组成。

第一步:

设计计数器

序列长度,设计一个模11计数器,选用74LS161,设定有效状态为=0101~1111。

第二步:

设计组合电路

设序列输出信号为,则计数器的输出和序列之间的关系如表A8.13所示。

表A8.13

Q3Q2Q1Q0

L

1011

1100

1101

1110

1111

×

化简得组合逻辑电路表达式为:

最后电路图如图A8.13所示(其中组合部分略)

[题8.14]图P8.14是由同步十进制计数器74160和3线-8线译码器74LS138组成的电路。

分析电路功能,画出74160的状态转换图和电路输出的波形图。

74160接成八进制计数器,计数状态从0000到0111,电路输出波形如图A8.14所示

[题8.15]试设计一个具有控制端的序列信号发生电路。

当分别为0和1时,在时钟作用下,电路输出端能分别周期性地输出10011010和00110101的序列信号。

用74LS161芯片和门电路实现。

序列长度,则只用74LS161的0从000到111状态即可。

根据题意,计数器的输出,控制端和序列之间的关系如表A8.15所示。

表A8.15

MQ2Q1

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 习题 答案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx