用verilogHDL多功能数字钟Word下载.docx

用verilogHDL多功能数字钟Word下载.docx

- 文档编号:14851381

- 上传时间:2022-10-25

- 格式:DOCX

- 页数:10

- 大小:529.74KB

用verilogHDL多功能数字钟Word下载.docx

《用verilogHDL多功能数字钟Word下载.docx》由会员分享,可在线阅读,更多相关《用verilogHDL多功能数字钟Word下载.docx(10页珍藏版)》请在冰豆网上搜索。

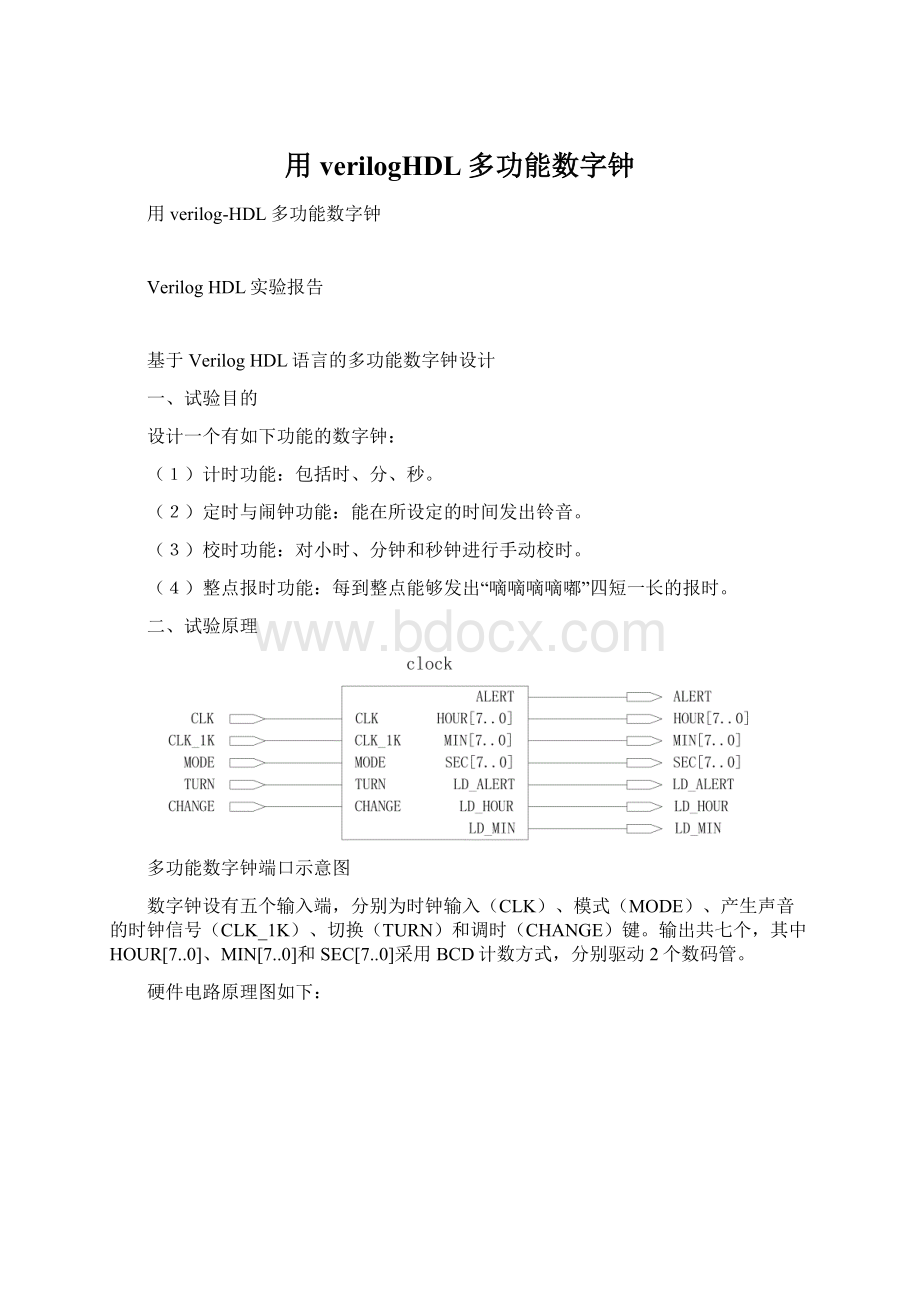

mode:

功能控制信号;

为0:

计时功能;

为1:

闹钟功能;

为2:

手动校时功能;

turn:

接按键,在手动校时功能时,选择是调整小时还是分钟;

若长时间按住改建,还可使秒信号清零,用于精确调时;

change:

接按键,手动调整时,每按一次,计数器加1;

如果长按,则连续快速加1,用于快速调时和定时;

hour,min,sec:

此三信号分别输出并显示时、分、秒信号,

皆采用BCD码计数,分别驱动6个数码管显示时间;

alert:

输出到扬声器的信号,用于产生闹铃音和报时音;

闹铃音为持续20秒的急促的“嘀嘀嘀”音,若按住“change”键,

则可屏蔽该音;

整点报时音为“嘀嘀嘀嘀嘟”四短一长音;

LD_alert:

接发光二极管,指示是否设置了闹钟功能;

LD_hour:

接发光二极管,指示当前调整的是小时信号;

LD_min:

接发光二极管,指示当前调整的是分钟信号

*/

moduleclock(clk,clk_1k,mode,change,turn,alert,hour,min,sec,LD_alert,LD_hour,LD_min);

inputclk,clk_1k,mode,change,turn;

outputalert,LD_alert,LD_hour,LD_min;

output[7:

0]hour,min,sec;

reg[7:

0]hour,min,sec,hour1,min1,sec1,ahour,amin;

reg[1:

0]m,fm,num1,num2,num3,num4;

0]loop1,loop2,loop3,loop4,sound;

regLD_hour,LD_min;

regclk_1Hz,clk_2Hz,minclk,hclk;

regalert1,alert2,ear;

regcount1,count2,counta,countb;

wirect1,ct2,cta,ctb,m_clk,h_clk;

always@(posedgeclk)

begin

clk_2Hz<

=~clk_2Hz;

if(sound==3)beginsound<

=0;

ear<

=1;

end//ear信号用于产生或屏蔽声音

elsebeginsound<

=sound+1;

end

end

always@(posedgeclk_2Hz)//由4Hz的输入时钟产生1Hz的时基信号

clk_1Hz<

=~clk_1Hz;

always@(posedgemode)//mode信号控制系统在三种功能间转换

beginif(m==2)m<

elsem<

=m+1;

always@(posedgeturn)

fm<

=~fm;

always//产生count1,count2,counta,countb四个信号

case(m)

2:

beginif(fm)

begincount1<

=change;

{LD_min,LD_hour}<

=2;

else

begincounta<

{count2,countb}<

1:

begincount2<

begincountb<

{count1,counta}<

=2'

b00;

default:

{count1,count2,counta,countb,LD_min,LD_hour}<

endcase

always@(negedgeclk)//如果长时间按下“change”键,则生成“num1”信号用于连续快速加1

if(count2)begin

if(loop2==3)num2<

else

beginloop2<

=loop2+1;

num2<

elsebeginloop2<

always@(negedgeclk)//产生num2信号

if(count1)begin

if(loop3==3)num3<

beginloop3<

=loop3+1;

num3<

elsebeginloop3<

always@(negedgeclk)

if(counta)begin

if(loop4==3)num4<

beginloop4<

=loop4+1;

num4<

elsebeginloop4<

assignct1=(num3&

clk)|(!

num3&

m_clk);

//ct1用于计时、校时中的分钟计数

assignct2=(num1&

num1&

count2);

//ct2用于在定时状态下调整分钟信号

assigncta=(num4&

num4&

h_clk);

//cta用于计时、校时中的小时计数

assignctb=(num2&

num2&

countb);

//ctb用于在定时状态下调整小时信号

always@(posedgeclk_1Hz)//秒计时和秒调整进程

if(!

(sec1^8'

h59)|turn&

(!

m))

sec1<

if(!

(turn&

m)))minclk<

//按住“turn”按键一段时间,秒信号可清零,该功能用于手动精确调时

elsebegin

if(sec1[3:

0]==4'

b1001)

beginsec1[3:

0]<

=4'

b0000;

sec1[7:

4]<

=sec1[7:

4]+1;

elsesec1[3:

=sec1[3:

0]+1;

minclk<

assignm_clk=minclk||count1;

always@(posedgect1)//分计时和分调整进程

if(min1==8'

h59)beginmin1<

hclk<

if(min1[3:

0]==9)

beginmin1[3:

min1[7:

=min1[7:

elsemin1[3:

=min1[3:

assignh_clk=hclk||counta;

always@(posedgecta)//小时计时和小时调整进程

if(hour1==8'

h23)hour1<

elseif(hour1[3:

beginhour1[7:

=hour1[7:

hour1[3:

elsehour1[3:

=hour1[3:

always@(posedgect2)//闹钟定时功能中的分钟调节进程

if(amin==8'

h59)amin<

elseif(amin[3:

beginamin[3:

amin[7:

=amin[7:

elseamin[3:

=amin[3:

always@(posedgectb)//闹钟定时功能中的小时调节进程

if(ahour==8'

h23)ahour<

elseif(ahour[3:

beginahour[3:

ahour[7:

=ahour[7:

elseahour[3:

=ahour[3:

always//闹铃功能

if((min1==amin)&

&

(hour1==ahour)&

(amin|ahour)&

change))

//若按住“change”键不放,可屏蔽闹铃音

if(sec1<

8'

h20)alert1<

//控制闹铃的时间长短

elsealert1<

always//时、分、秒的现实控制

3'

b00:

beginhour<

=hour1;

min<

=min1;

sec<

=sec1;

//计时状态下的时、分、秒显示

b01:

=ahour;

=amin;

=8'

hzz;

//定时状态下的时、分、秒显示

b10:

//校时状态下的时、分、秒显示

assignLD_alert=(ahour|amin)?

1:

0;

//指示是否进行了闹铃定时

assignalert=((alert1)?

clk_1k&

clk:

0)|alert2;

//产生闹铃音或整点报时音

always//产生整点报时信号alert2

if((min1==8'

h59)&

(sec1>

h54)||(!

(min1|sec1)))

if(sec1>

h54)alert2<

=ear&

clk_1k;

//产生短音

elsealert2<

=!

ear&

//产生长音

endmodule

2.仿真图

四、小结及体会

为了做多功能数字钟,我借了多本关于VerilogHDL的程序设计书。

在前几次试验中,因为课程还没有讲完,所以书上的好多代码还不能看懂,只是能猜到大概意思,再根据试验结果来判断代码的意思。

本次试验让我学到了如何分频、用一个键来进行模式选择、if/else的用法、case的用法、秒信号清零等知识。

并且对QuartersⅡ有了进一步的掌握,熟悉使用了VHDL、VerilogHDL、生成电路图、仿真波形、连接实验箱、下载程序等。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- verilogHDL 多功能 数字

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx