最新EDA实验报告Word文件下载.docx

最新EDA实验报告Word文件下载.docx

- 文档编号:15819676

- 上传时间:2022-11-16

- 格式:DOCX

- 页数:34

- 大小:257.11KB

最新EDA实验报告Word文件下载.docx

《最新EDA实验报告Word文件下载.docx》由会员分享,可在线阅读,更多相关《最新EDA实验报告Word文件下载.docx(34页珍藏版)》请在冰豆网上搜索。

S1

S0

Y

D0

D1

1

D2

D3

3、逻辑表达式

三、实验内容

1、为本项工程设计建立文件夹(文件名不能用中文)

2、输入设计项目和存盘

(1)打开原理图编辑窗口

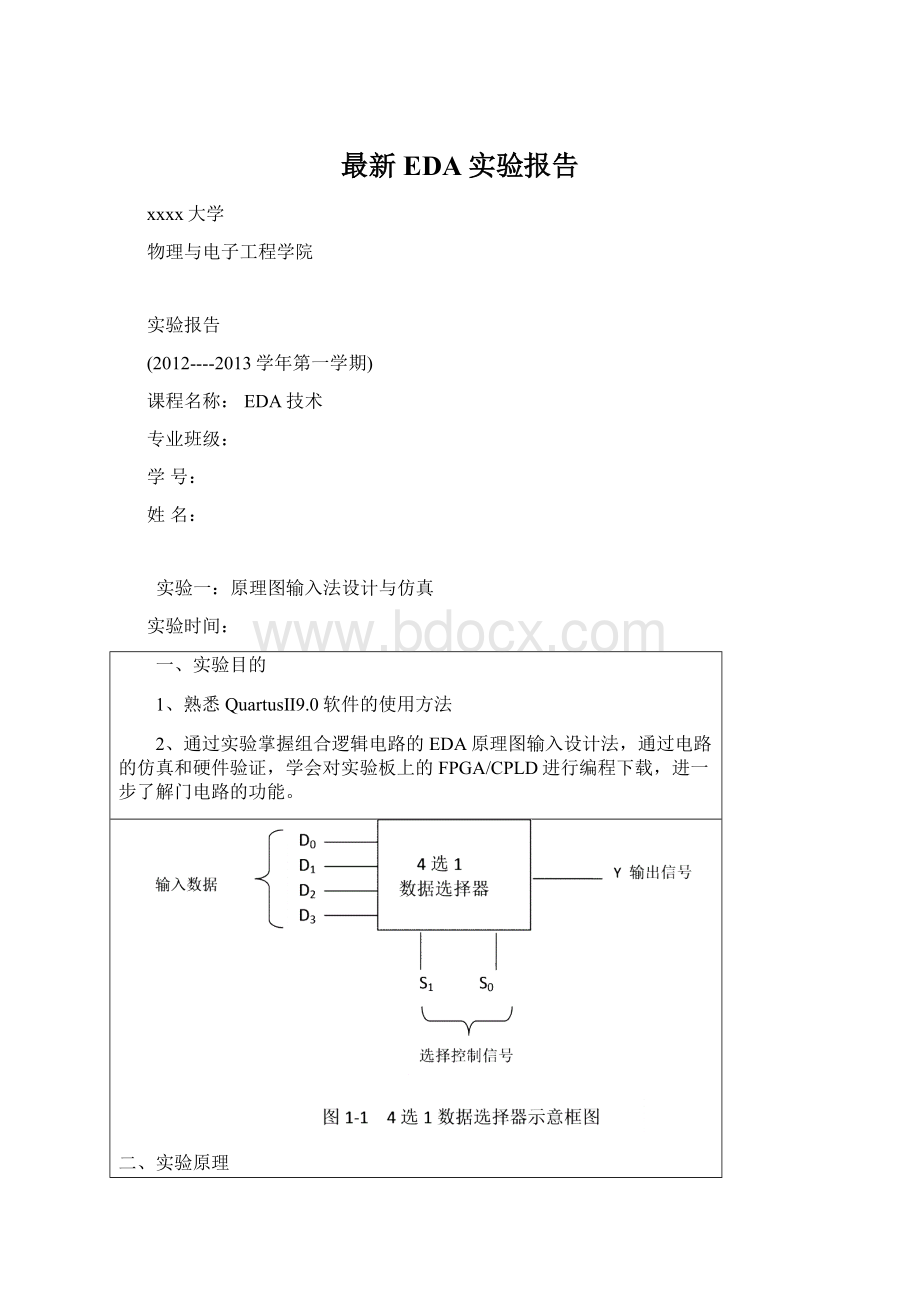

(2)编辑4选1数据选择器的原理图

(3)文件存盘:

以mux41.bdf为文件名保存在工程目录中。

(3)建立工程:

为mux41.bdf建立工程,工程名可以与文件夹相同。

(4)编译

3、仿真4、引脚锁定5、编程下载与硬件验证

四、实验设计

1、原理图

3、管脚锁定

五、实验结果及总结

1、系统时序仿真情况

六、实验心得

其实这个实验很简单,仅仅是让我们熟悉QuartusⅡ9.0软件的使用方法,在书本上的每个步骤都写的清清楚楚,我们组员按着书本上的步骤一步一步的做,实验做完后,我们那一大组很多小组依旧不停的请求老师指导,我们是最先做完实验的小组了。

之后我们被不同的小组询问。

其实只要看看书就可以很顺利做完实验,但是同学们做实验之前都没有好好做实验预习报告。

指导教师:

成绩

实验二七人表决器的设计

实验时间

1、初步了解VHDL语言;

2、学会用行为描述方式来设计电路。

1、用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;

输入变量为“0”时,表示表决者“不赞同”。

输出逻辑“1”时,表示表决“通过”;

输出逻辑“0”时,表示表决“不通过”。

当表决器的七个输入变量中有4个以上(含4个)为“1”时,则表决器输出为“1”;

否则为“0”。

2、采用行为描述时,可用一变量来表示选举通过的总人数。

当选举人大于或等于4时为通过,输出灯亮,反之不通过时,灯不亮。

描述时,只须检查每一个输入的状态(通过为“1”不通过为“0”)并将这些状态值相加,判断状态值和即可选择输出。

1.编写上述电路的VHDL源程序,并进行编译。

2.锁定引脚,建议选择实验电路模式5。

3.编程下载与硬件验证。

1、VHDL程序

libraryieee;

useieee.std_logic_1164.all;

entitybiaoqueis

port(x0,x1,x2,x3,x4,x5,x6:

inbit;

y1:

outbit);

endentitybiaoque;

architectureoneofbiaoqueis

begin

process(x0,x1,x2,x3,x4,x5,x6)

variablea,b,c,d,e:

integer;

begin

a:

=0;

b:

c:

e:

if((x0orx1)='

0'

)thena:

elsif((x0andx1)='

1'

=2;

elsea:

=1;

endif;

if((x2orx3)='

)thenb:

elsif((x2andx3)='

elseb:

if((x4orx5)='

)thenc:

elsif((x4andx5)='

elsec:

ifx6='

thend:

elsed:

e:

=a+b+c+d;

ife>

=4theny1<

='

;

elsey1<

endprocess;

endarchitectureone;

2、系统时序仿真情况

3、引脚匹配

做这个实验之前做了预习报告,但是上实验室进行调试和老师的指导,才发现自己的之前的程序是行不通的,看到其他小组不同的程序,最后经过努力重新编写,最后成功完成实验。

条条道路通罗马,在学习的道路上不能去复制他人的东西,而要自己去思考,去创新!

努力让自己多学点东西。

经过努力完成的事情才会有成就感。

实验三显示电路设计

1、学习7段数码显示译码器设计;

2、学习VHDL的多层设计方法。

二、实验仪器设备

1、PC机一台2、GW48-PK2系列SOPC/EDA实验开发系统

三、实验原理

1、七段数码显示工作原理(共阴极接法)

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

作为7段译码器,输出信号LED7S的7位分别接数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段:

g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;

接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h。

2、显示代码概念显示代码

字型

abcdefg

1111110

0110000

2

1101101

3

1111001

4

0110011

5

1011011

6

1011111

7

1110000

8

1111111

9

1111011

四、实验内容

1、编写7段译码器VHDL源程序。

2、在QuartusⅡ软件上编译和仿真。

3、锁定管脚,建议选择实验电路模式6,显示译码输出用数码8显示译码输出(PIO46-PIO40),键8、键7、键6和键5四位控制输入。

4编程下载与硬件验证。

5、记录系统仿真和硬件验证结果。

五、实验结果:

1、VHDL源程序

port(x:

instd_logic_vector(3downto0);

led:

outstd_logic_vector(6downto0));

endentityxianshi;

architectureoneofxianshiis

signalled7:

std_logic_vector(6downto0);

process(x)

casexis

when"

0000"

=>

led<

="

1111110"

0001"

0110000"

0010"

1101101"

0011"

1111001"

0100"

0110011"

0101"

1011011"

0110"

1011111"

0111"

1110000"

1000"

1111111"

1001"

1111011"

whenothers=>

null;

endcase;

2、波形仿真图:

4、引脚锁定:

六、实验心得:

其实本实验的显示我们在模电里面就学习过了,也用集成块进行过实验,本实验用程序加硬件完成。

真所谓条条道路通罗马!

实验四四位全加器

通过实验让学生熟悉QuartusⅡ的VHDL文本设计流程全过程,掌握组合逻辑电路的文本输入设计法,通过对设计电路的仿真和硬件验证,让学生进一步了解加法器的功能。

1、PC机一台

2、GW48-PK2系列SOPC/EDA实验开发系统

C0C0

C2C0

C1C0

4位全加器可看作4个1位全加器串行构成,具体连接方法如下图所示:

图3-1由1位全加器构成4位全加器连接示意图

采用VHDL语言设计时调用其附带的程序包,其系统内部会自行生成此结构

4.编写1位全加器full_add1的VHDL源程序,并进行编译。

5.利用元件例化语句编写4位全加器full_adder4的VHDL源程序,并进行编译和仿真。

6.锁定引脚,建议选择实验电路模式1:

键1输入4位加数,键2输入4位被加数,键8输入Cin,数码管5显示相加和,D8显示进位CO。

7.编程下载与硬件验证。

五、设计提示

调用STD_LOGIC_UNSIGNED包。

先设计一个一位的全加器包括三个输入端:

a,b,cin(进位输入),两个输出端:

s(和),cout(进位输出)。

四位串行进位的全加器可以利用四个一位的全加器搭建而成,其结构如上图所示,其输入端口分别为a0,a1,a2,a3,b0,b1,b2,b3,cin输出端口分别为s0,s1,s2,s3,cout。

在实验中只需要先描述一位全加器,然后用component语句进行元件说明,再利用元件例化语句就可以实现四位的全加器。

六、实验验证:

1、实验程序:

一位全加器

entityfull_add1is

port(a,b,cin:

instd_logic;

s,count:

outstd_logic);

endentityfull_add1;

architectureoneoffull_add1is

begin

s<

=axorbxorcin;

count<

=(aandb)or(aandcin)or(bandcin);

四位全加器

entityfull_adder4is

port(A,B:

Cin:

S:

outstd_logic_vector(3downto0);

Co:

endentityfull_adder4;

architecturetwooffull_adder4is

componentfull_add1is

port(a,b,cin:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 最新 EDA 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx