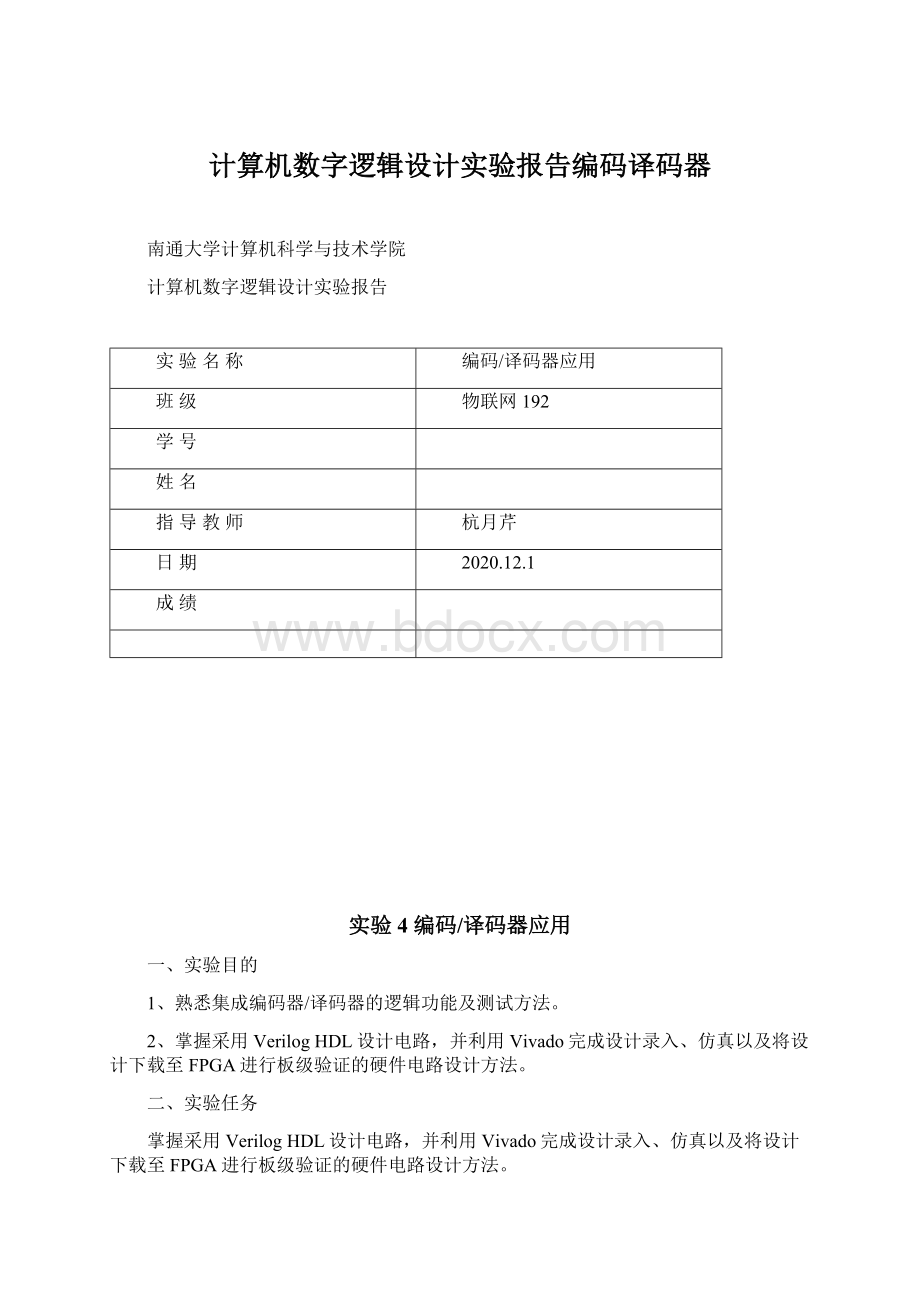

计算机数字逻辑设计实验报告编码译码器Word格式.docx

计算机数字逻辑设计实验报告编码译码器Word格式.docx

- 文档编号:18047432

- 上传时间:2022-12-13

- 格式:DOCX

- 页数:16

- 大小:7.91MB

计算机数字逻辑设计实验报告编码译码器Word格式.docx

《计算机数字逻辑设计实验报告编码译码器Word格式.docx》由会员分享,可在线阅读,更多相关《计算机数字逻辑设计实验报告编码译码器Word格式.docx(16页珍藏版)》请在冰豆网上搜索。

利用Verilog设计源文件和仿真文件;

设计实验验证方法和数据分析等。

2、利用Verilog设计3-8译码器74LS138和优先编码器74LS148的相关电路,在Vivado中完成设计、仿真与硬件下载,记录并分析讨论实验结果的正确性,最后给出测试结论。

3、实验完毕,写出实验报告。

五、实验预习内容

1、3-8译码器74LS138的工作原理

利用Vivado提供的IP包,也可直接用代码搭建74LS138功能验证电路。

(1)当选通端e1为高电平,另两个选通端e2和e3为低电平时,芯片使能。

将地址端(a2、a1、a0)的二进制编码在y0至y7对应的输出端以低电平译出。

(2)利用e1、e2和e3可方便的级联扩展成16线译码器、32线译码器。

(3)若将选通端中的一个作为数据输入端时,74LS138还可用作数据分配器。

测试74LS138逻辑关系接线图

如果用verilog编程实现译码功能,参考代码如下。

moduleconverter(DB,SEG);

input[2:

0]DB;

output[7:

0]SEG;

reg[7:

always@(DB)

begin

case(DB)

4'

b0000:

SEG<

=8'

b11111110;

b0001:

=8’b11111101;

b0010:

=8’b11111011;

b0011:

=8’b11110111;

b0100:

=8’b11101111;

b0101:

=8’b11011111;

b0110:

=8’b10111111;

b0111:

=8’b01111111;

default:

b11111111;

endcase

end

endmodule

2、优先编码器74148的工作原理

在优先编码器电路中,允许同时输入两个以上编码信号。

不过在设计优先编码器时,已经将所有的输入信号按优先顺序排了队。

在同时存在两个或两个以上输入信号时,优先编码器只按优先级高的输入信号编码,优先级低的信号则不起作用。

74LS148是一个8-3线优先级编码器。

74148优先编码器为16脚的集成芯片,除电源脚VCC(16)和GND(8)外,其余输入、输出脚的作用和脚号如图中所标。

其中i0~i7为输入信号(i7优先权最高),qc、qb、qa为三位二进制编码输出信号,ei是使能输入端,eo使能输出端,gs为片优先编码输出端。

电路接线如图所示。

编码器接线

如果用verilog编程实现优先编码功能,则代码如下。

moduleencoder_83(din,EI,GS,EO,dout);

input[7:

0]din;

//编码输入端data_in,低电平有效

inputEI;

//使能输入端EI(选通输入端),EI为0时芯片工作,即允许编码

output[2:

0]dout;

//编码输出端data_out

outputGS;

//片优先编码输出端,优先编码器工作工作状态标志GS,低电平有效

outputEO;

//使能输出端EO(选通输出端)

reg[2:

regGS,EO;

always@(dinorEI)

if(EI)begindout<

=3'

b111;

GS<

=1;

EO<

end//所有输出端被锁存在高电平

elseif(din[7]==0)begindout<

b000;

=0;

end

elseif(din[6]==0)begindout<

b001;

elseif(din[5]==0)begindout<

b010;

elseif(din[4]==0)begindout<

b011;

elseif(din[3]==0)begindout<

b100;

elseif(din[2]==0)begindout<

b101;

elseif(din[1]==0)begindout<

b110;

elseif(din[0]==0)begindout<

elseif(din==8'

b11111111)begindout<

end//芯片工作,但无编码输入

elsebegindout<

end//消除锁存器(latch)

endmodule

//EI=0表示允许编码,否则所有输出端被封锁在高电平(控制芯片工作)

//EO=0表示电路工作,但无编码输入(用于级联)

//GS=0表示电路工作,且有编码输入(判断输入端是否有输入)

六、实验内容与操作步骤

1、设计3-8译码器74LS138的功能电路和仿真测试。

利用EGO1实验板上的3个开关作为输入、8个LED作为输出。

本实验采用XUPIP包,再加3个开关作为芯片使能。

实验电路原理图如下:

.

设计仿真激励程序代码如下:

modulerun();

rega1,a2,a0,e1,e2,e3;

wirey0,y1,y2,y3,y4,y5,y6,y7;

design_1test(.a0(a0),.a1(a1),.a2(a2),.e1(e1),.e2(e2),.e3(e3),.y0(y0),.y1(y1),.y2(y2),.y3(y3),.y4(y4),.y5(y5),.y6(y6),.y7(y7));

alwaysbegin

e1=0;

#100;

e1=1;

e3=1;

e2=1;

a0=0;

a1=0;

a2=0;

e1=1;

e2=0;

e3=0;

a0=1;

a1=1;

a2=1;

仿真测试结果如下:

根据仿真结果,完成如下表格:

输入

输出

使能

选择

e1(G1)

e2(G2B)

e3(G2A)

a2(C)

a1(B)

a0(A)

y7

y6

y5

y4

y3

y2

y1

y0

×

1

结合逻辑电路原理图,分析表中的实验结果。

经对比,表中记录的仿真测试数据与设计要求的值一致。

对照电路功能的要求,可知,本次实验设计的电路实现了译码器的功能。

2、采用Verilog设计优先编码器74LS148的功能电路和仿真测试。

利用EGO1实验板上的8个开关作为输入、3个LED作为编码结果输出、2个LED作为其他输出信号。

本实验利用XUPIP包,再加1个开关作为芯片使能。

regei;

wireeo;

wiregs;

regi0;

regi1;

regi2;

regi3;

regi4;

regi5;

regi6;

regi7;

wireqa;

wireqb;

wireqc;

design_1test(.ei(ei),.eo(eo),.gs(gs),.i0(i0),.i1(i1),.i2(i2),.i3(i3),.i4(i4),.i5(i5),.i6(i6),.i7(i7),.qa(qa),.qb(qb),.qc(qc));

ei=1;

ei=0;

i7=1;

i6=0;

i6=1;

i5=0;

i5=1;

i4=0;

i4=1;

i3=0;

i3=1;

i2=0;

i2=1;

i1=0;

i1=1;

i0=0;

i0=1;

ei

i7

i6

i5

i4

i3

i2

i1

i0

qc

qb

qa

eo

gs

对照电路功能的要求,可知,本次实验设计的电路实现了编码器的功能。

七、硬件下载过程说明、实验板运行照片和实验板运行测试结论

点击“IMPLEMENTATION->

OpenImplementedDesign”,进入ImplementedDesign模式,按照EG01硬件手册提供的资料,选择输入和输出设备,设置管脚约束,设置完毕,保存管脚约束文件。

译码器管脚约束如下:

set_propertyPACKAGE_PINP5[get_portsa0]

set_propertyPACKAGE_PINP4[get_portsa1]

set_propertyPACKAGE_PINP3[get_portsa2]

set_propertyPACKAGE_PINM4[get_portse1]

set_propertyPACKAGE_PINN4[get_portse2]

set_propertyPACKAGE_PINR1[get_portse3]

set_propertyIOSTANDARDLVCMOS33[get_portsa0]

set_propertyIOSTANDARDLVCMOS33[get_portsa1]

set_propertyIOSTANDARDLVCMOS33[get_portsa2]

set_propertyIOSTANDARDLVCMOS33[get_portse1]

set_propertyIOSTANDARDLVCMOS33[get_portse2]

set_propertyIOSTANDARDLVCMOS33[get_portse3]

set_propertyPACKAGE_PINF6[get_portsy0]

set_propertyPACKAGE_PING4[get_portsy1]

set_propertyPACKAGE_PING3[get_portsy2]

set_propertyPACKAGE_PINJ4[get_portsy3]

set_propertyPACKAGE_PINH4[get_portsy4]

set_propertyPACKAGE_PINJ3[get_portsy5]

set_propertyPACKAGE_PINJ2[get_portsy6]

set_propertyPACKAGE_PINK2[get_portsy7]

set_propertyIOSTANDARDLVCMOS33[get_portsy0]

set_propertyIOSTANDARDLVCMOS33[get_portsy1]

set_propertyIOSTANDARDLVCMOS33[get_portsy2]

set_propertyIOSTANDARDLVCMOS33[get_portsy3]

set_propertyIOSTANDARDLVCMOS33[get_portsy4]

set_propertyIOSTANDARDLVCMOS33[get_portsy5]

set_propertyIOSTANDARDLVCMOS33[get_portsy6]

set_propertyIOSTANDARDLVCMOS33[get_portsy7]

程序中管脚名

实际管脚

说明

a0

P5

数值输入

a1

P4

a2

P3

e1

M4

使能输入

e2

N4

e3

R1

F6

LED输出

G4

G3

J4

H4

J3

J2

K2

实验板运行如图所示:

a=0,b=0,c=0全亮a=1,b=0,c=0全亮

a=0,b=1,c=0全亮a=1,b=1,c=0d灭

a=0,b=0,c=1e灭a=1,b=0,c=1f灭

a=0,b=1,c=1g灭a=1,b=1,c=1h灭

编码器管脚约束如下:

set_propertyPACKAGE_PINF6[get_portseo]

set_propertyPACKAGE_PING4[get_portsgs]

set_propertyPACKAGE_PINJ3[get_portsqa]

set_propertyPACKAGE_PINJ2[get_portsqb]

set_propertyPACKAGE_PINK2[get_portsqc]

set_propertyPACKAGE_PINR1[get_portsi7]

set_propertyPACKAGE_PINN4[get_portsi6]

set_propertyPACKAGE_PINM4[get_portsi5]

set_propertyPACKAGE_PINR2[get_portsi4]

set_propertyPACKAGE_PINP2[get_portsi3]

set_propertyPACKAGE_PINP3[get_portsi2]

set_propertyPACKAGE_PINP4[get_portsi1]

set_propertyPACKAGE_PINP5[get_portsi0]

set_propertyPACKAGE_PINT5[get_portsei]

set_propertyIOSTANDARDLVCMOS33[get_portsei]

set_propertyIOSTANDARDLVCMOS33[get_portseo]

set_propertyIOSTANDARDLVCMOS33[get_portsgs]

set_propertyIOSTANDARDLVCMOS33[get_portsi0]

set_propertyIOSTANDARDLVCMOS33[get_portsi1]

set_propertyIOSTANDARDLVCMOS33[get_portsi2]

set_propertyIOSTANDARDLVCMOS33[get_portsi3]

set_propertyIOSTANDARDLVCMOS33[get_portsi4]

set_propertyIOSTANDARDLVCMOS33[get_portsi5]

set_propertyIOSTANDARDLVCMOS33[get_portsi7]

set_propertyIOSTANDARDLVCMOS33[get_portsi6]

set_propertyIOSTANDARDLVCMOS33[get_portsqa]

set_propertyIOSTANDARDLVCMOS33[get_portsqb]

set_propertyIOSTANDARDLVCMOS33[get_portsqc]

T5

P2

R2

eo

使能输出端

优先编码输出

数值输出

a~g=0,h=1a、f亮a~f=0g,h=1a,g亮

a~e=0,f,g,h=1a,f,g亮a~d=0,e~h=1a,h亮

a~c=0,d~h=1a,f,h亮a~b=0,c~h=1,a,g,h亮

a=0,b~h=1,a,f,g,h亮a~h=1b,f,g,h亮

八、实验体会与小结

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 计算机 数字 逻辑设计 实验 报告 编码 译码器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx