双积分型AD转换器Word下载.docx

双积分型AD转换器Word下载.docx

- 文档编号:18790087

- 上传时间:2023-01-01

- 格式:DOCX

- 页数:15

- 大小:218.85KB

双积分型AD转换器Word下载.docx

《双积分型AD转换器Word下载.docx》由会员分享,可在线阅读,更多相关《双积分型AD转换器Word下载.docx(15页珍藏版)》请在冰豆网上搜索。

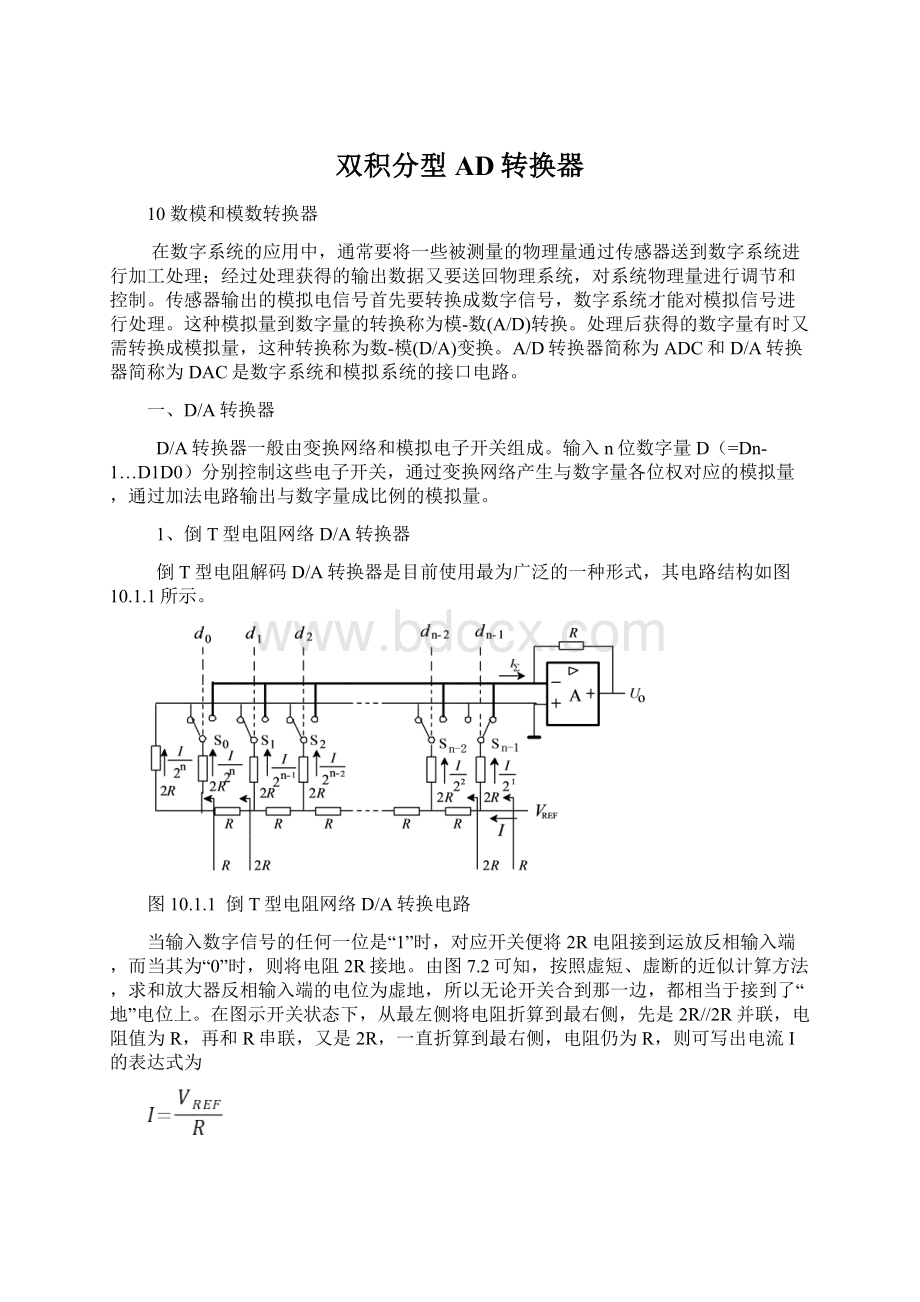

D/A转换器大部份是数字电流转换器,实用中通常需增加输出电路,实现电流电压变换。

在变换网络中,电流是单方向的,即在0和正满度值或负满度值之间变化,是单极性的。

为了能使输出在正负满度值之间变化,也即双极性输出方式,也需要增加输出电路。

在单极性输出方式时,数字量采用自然二进制码表示大小,输出电路只要完成电流→电压的变换即可。

双极性输出方式时,数字量是双极性数。

二进制双极性数字的负数可采用:

2的补码、偏移二进制码或符号数值码(符号位加数值码)。

表10.1.1列出了部分四位双极性二进制码。

表10.1.1部分四位双极性二进制码

由表10.1.1可见,偏移二进制码是在自然二进制码的基础上偏移而成的,四位偏移二进制码的偏移量为1000(8H)。

因此,按自然二进制码进行D/A变换后,只要将输出模拟量也进行相应偏移(减去1000对应的模拟值)即可获双极性输出。

数字量以2的补码表示时,需先将2的补码转换成偏移二进制码(2的补码加1000),然后送D/A转换器,可得双极性输出。

4、D/A转换器的主要技术指标

(1)转换精度

D/A转换器转换精度用分辨率和转换误差描述。

※分辨率

分辨率是用以说明D/A转换器在理论上可达到的精度。

用于表征D/A转换器对输入微小量变化的敏感程度,显然输入数字量位数越多,输出电压可分离的等级越多,即分辨率越高。

所以实际应用中,往往用输入数字量的位数表示DA转换器的分辨率。

此外,D/A转换器的分辨率也定义为电路所能分辨的最小输出电压ULSB与最大输出电压Um之比来表示,即

分辨率

上式说明,输入数字代码的位数n越多,分辨率越小,分辨能力越高,例如,5G7520十位DA转换器的分辨率为

※转换误差

是用以说明D/A转换器实际上能达到的转换精度。

转换误差可用输出电压满度值的百分数表示,也可用LSB的倍数表示。

例如,转换误差为

LSB,用以表示输出模拟电压的绝对误差等于当输入数字量的LSB为1,其余各位均为0时输出模拟电压的二分之一。

转换误差又分静态误差和动态误差。

产生静态误差的原因有,基准电源VREF的不稳定,运放的零点漂移,模拟开关导通时的内阻和压降以及电阻网络中阻值的偏差等。

动态误差则是在转换的动态过程中产生的附加误差,它是由于电路中的分布参数的影响,使各位的电压信号到达解码网络输出端的时间不同所致。

(2)转换速度

※建立时间tset

它是在输入数字量各位由全0变为全1,或由全1变为全0,输出电压达到某一规定值(例如最小值取

LSB或满度值的0.01%)所需要的时间。

目前,在内部只含有解码网络和模拟开关的单片集成DA转换器中,tset≤0.1s;

在内部还包含有基准电源和求和运算放大器的集成DA转换器中,最短的建立时间在1.5s左右。

※转换速率SR

它是在大信号工作时,即输入数字量的各位由全0变为全1,或由全1变为0时,输出电压uo的变化率。

这个参数与运算放大器的压摆率类似。

(3)温度系数

5、集成D/A转换器及其应用

单片集成D/A转换器产品种类繁多,按其内部电路结构一般可分为两类:

一类集成芯片内部只集成了转换网络和模拟电子开关;

另一类则集成了组成D/A转换器的所有电路。

AD7520十位D/A转换器属于前一类集成D/A转换器。

AD7520芯片内部只含R-2R电阻网络、CMOS电子开关和反馈电阻(Rf=10kΩ)。

应用AD7520时必须外接参考电源和运算放大器。

由AD7520内部反馈电阻组成的D/A转换器如图10.1.3所示,虚框中是AD7520內部电路。

图10.1.3AD7520内部电路及组成的D/A转换器

应用:

数字式可编程增益控制电路

图10.1.4数字式可控增益运算放大器

二、A/D转换器

将时间连续和幅值连续的模拟量转换为时间离散、幅值也离散的数字量,A/D转换一般要经过采样、保持、量化及编码4个过程。

在实际电路中,有些过程是合并进行的,如采样和保持,量化和编码在转换过程中是同时实现的。

1、采样和保持

采样是将时间连续的模拟量转换为时间上离散的模拟量,即获得某此时间点(离散时间)的模拟量值。

因为,进行A/D转换需要一定的时间,在这段时间内输入值需要保持稳定,因此,必须有保持电路维持采样所得的模拟值。

采样和保持通常是通过采样-保持电路同时完成的。

为使采样后的信号能够还原模拟信号,根据取样定理,采样频率fS必须大于或等于2倍输入模拟信号的最高频率fImax,

fS≥2fImax

即两次采样时间间隔不能大于1/fS,否则将失去模拟输入的某些特征。

图10.1.5给出了采样-保持电路的原理图和经采样、保持后的输出波形。

图中采样电子开关S受采样信号S(t)控制,定时地合上S,对保持电容CH充放电。

因A1、A2接成电压跟随器,此时vO=vI。

S打开时,保持电容CH因无放电回路保持釆样所获得的输入电压,输出电压亦保持不变。

图10.1.5采样-保持电路及输入输出波形

2、量化与编码

数字信号不仅在时间上是离散的,而且在幅值上也是不连续的。

任何一个数字量只能是某个最小数量单位的整数倍。

为将模拟信号转换为数字量,在转换过程中还必须把采样-保持电路的输出电压,按某种近似方式归化到与之相应的离散电平上。

这一过程称为数值量化,简称量化。

量化过程中的最小数值单位称为量化单位,用△表示。

它是数字信号最低位为1,其它位为0时所对应的模拟量,即1LSB。

量化过程中,采样电压不一定能被△整除,因此量化后必然存在误差。

这种量化前后的不等(误差)称之为量化误差,用ε表示。

量化误差是原理性误差,只能用较多的二进制位缩小量化误差。

量化的近似方式有:

只舍不入和四舍五入两种。

只舍不入量化方式量化后的电平总是小于或等乎量化前的电平,即量化误差ε始终大于0,最大量化误差为△,即εmax=1LSB。

采用四舍五入量化方式时,量化误差有正有负,最大量化误差为△/2,即∣εmax︱=LSB/2。

显然,后者量化误差小,故为大多数A/D转换器所采用。

量化后的电平值为量化单位△的整数倍,这个整数用二进制数表示即为编码。

量化和编码也是同时进行的。

3、A/D转换器的种类

按工作原理不同,A/D转换器可以分为:

直接型A/D转换器和间接型A/D转换器。

直接型A/D转换器可直接将模拟信号转换成数字信号,这类转换器工作速度快。

并行比较型和逐次比较型A/D转换器属于这一类。

而间接型A/D转换器先将模拟信号转换成中间量(如时间、频率等),然后再将中间量转换成数字信号,转换速度比较慢。

双积分型A/D转换器则属于间接型A/D转换器。

(1)并行比较型A/D转换器

图7.7三位并行A/D转换器

3位并行比较型A/D转换器原理电路如图10.1.5所示。

它由电阻分压器、电压比较器、寄存器及编码器组成。

图中的八个电阻将参考电压VREF分成八个等级,其中七个等级的电压分别作为七个比较器C1~C7的参考电压,其数值分别为VREF/15、3VREF/15、…13VREF/15。

输入电压为uI,它的大小决定各比较器的输出状态,例如,当0≤uI<(VREF/15)时,C1~C7的输出状态都为0;

当(3VREF/15)<uI<(5VREF/15)时,比较器C1和C2的输出C01=C02=1,其余各比较器输出状态都为0。

根据各比较器的参考电压值,可以确定输入模拟电压值与各比较器输出状态的关系。

比较器的输出状态由D触发器存储,CP作用后,触发器的输出状态Q7~Q1与对应的比较器的输出状态C07~C01相同。

经代码转换网络(优先编码器)输出数字量D2D1D0。

优先编码器优先级别最高是Q7,最低是Q1。

设uI变化范围是0~VREF,输出3位数字量为D2、D1、D0,3位并行比较型A/D转换器的输入、输出关系如表10.1.2所示。

通过观察此表,可确定代码转换网络输出、输入之间的逻辑关系

D2=Q4

D1=Q6

在并行AD转换器中,输入电压uI同时加到所有比较器的输出端,从uI加入经比较器、D触发器和编码器的延迟后,可得到稳定的输出。

如不考虑上述器件的延迟,可认为输出的数字量是与uI输入时刻同时获得的。

并行A/D转换器的优点是转换时间短,可小到几十纳秒,但所用的元器件较多,如一个n位转换器,所用的比较器的个数为

个。

表10.1.2并行比较型AD转换器的输入输出关系

模拟量输出

比较器输出状态

数字输出

C07C06CO5CO4CO3CO2CO1

D2D1D0

0≤uI<

VREF/15

0000000

000

VREF/15≤uI<

3VREF/15

0000001

001

3VREF/15≤uI<

5VREF/15

0000011

010

5VREF/15≤uI<

7VREF/15

0000111

011

7VREF/15≤uI<

9VREF/15

0001111

100

9VREF/15≤uI<

11VREF/15

0011111

101

11VREF/15≤uI<

13VREF/15

0111111

110

13VREF/15≤uI<

VREF

1111111

111

单片集成并行比较型AD转换器产品很多,如AD公司的AD9012(8位)、AD9002(8位)和AD9020(10位)等。

(2)逐次比较型A/D转换器

逐次逼近型A/D转换器属于直接型A/D转换器,它能把输入的模拟电压直接转换为输出的数字代码,而不需要经过中间变量。

转换过程相当于一架天平秤量物体的过程,不过这里不是加减砝码,而是通过D/A转换器及寄存器加减标准电压,使标准电压值与被转换电压平衡。

这些标准电压通常称为电压砝码。

逐次逼近型A/D转换器由比较器、环形分配器、控制门、寄存器与D/A转换器构成。

比较的过程首先是取最大的电压砝码,即寄存器最高位为1时的二进制数所对应的D/A转换器输出的模拟电压,将此模拟电压uA与uI进行比较,当uA大于uI时,最高位置0;

反之,当uA小于uI时,最高位1保留,再将次高位置1,转换为模拟量与uI进行比较,确定次高位1保留还是去掉。

依次类推,直到最后一位比较完毕,寄存器中所存的二进制数即为uI对应的数字量。

以上过程可以用图10.1.6加以说明,图中表示将模拟电压uI转换为四位二进制数的过程。

图中的电压砝码依次为800mV、400mV、200mV和100mV,转换开始前先将寄存器清零,所以加给DA转换器的数字量全为0。

当转换开始时,通过DA转换器送出一个800mV的电压砝码与输入电压比较,由于uI<800mV,将800mV的电压砝码去掉,再加400mV的电压砝码,uI>400mV,于是保留400mV的电压砝码,再加200mV的砝码,uI>400mV+200mV,200mV的电压砝码也保留;

再加100mV的电压砝码,因uI<400mV+200mV+100mV,故去掉100mV的电压砝码。

最后寄存器中获得的二进制码0110,即为uI对应的二进制数。

图10.1.6逐次逼近型A/D转换器的逼近过程示意图

逐次逼近A/D转换器的工作原理

下面结合图10.1.7的逻辑图具体说明逐次比较的过程。

这是一个输出3位二进制数码的逐次逼近型A/D转换器。

图中的C为电压比较器,当

时,比较器的输出

;

当

时

。

FA、FB和FC三个触发器组成了3位数码寄存器,触发器F1~F5构成环形分配器和门G1~G9一起组成控制逻辑电路。

转换开始前先将FA、FB、FC置零,同时将F1~F5组成的环型移位寄存器置成[Q1Q2Q3Q4Q5]=10000状态。

转换控制信号UL变成高电平以后,转换开始。

第一个CP脉冲到达后,FA被置成“1”,而FB、FC被置成“0”。

这时寄存器的状态[QAQBQC]=100加到DA转换器的输入端上,并在DA转换器的输出端得到相应的模拟电压UA(800mV)。

UA和

比较,其结果不外乎两种:

若

,则

同时,移位寄存器右移一位,使[Q1Q2Q3Q4Q5]=01000。

第二个CP脉冲到达时FB被置成1。

若原来的

(

),则FA被置成“0”,此时电压砝码为400mV;

),则FA的“1”状态保留,此时的电压砝码为400mV加上原来的电压砝码值。

同时移位寄存器右移一位,变为00100状态。

第三个CP脉冲到达时FC被置成1。

,则FB被置成“0”;

,则FB的“1”状态保留,此时的电压砝码为200mV加上原来保留的电压砝码值。

同时移位寄存器右移一位,变成00010状态。

图10.1.7三位逐次逼近型AD转换器逻辑图

第四个CP脉冲到达时,同时根据这时

的状态决定FC的“1”是否应当保留。

这时FA、FB、FC的状态就是所要的转换结果。

同时,移位寄存器右移一位,变为00001状态。

由于Q5=1,于是FA、FB、FC的状态便通过门G6、G7、G8送到了输出端。

第五个CP脉冲到达后,移位寄存器右移一位,使得[Q1Q2Q3Q4Q5]=10000,返回初始状态。

同时,由于Q5=0,门G6、G7、G8被封锁,转换输出信号随之消失。

所以对于图示的AD转换器完成一次转换的时间为(n+2)TCP。

同时为了减小量化误差,令DA转换器的输出产生-

的偏移量。

另外,图7.9中量化单位

的大小依uI的变化范围和AD转换器的位数而定,一般取

显然,在一定的限度内,位数越多,量化误差越小,精度越高。

图10.1.9双积分型A/D转换器原理图

(3)双积分型A/D转换器

双积分型A/D转换器属于间接型A/D转换器,它是把待转换的输入模拟电压先转换为一个中间变量,例如时间T;

然后再对中间变量量化编码,得出转换结果,这种AD转换器多称为电压-时间变换型(简称VT型)。

图10.1.10给出的是VT型双积分式AD转换器的原理图。

图10.1.10双积分型AD转换器的框图

转换开始前,先将计数器清零,并接通S0使电容C完全放电。

转换开始,断开S0。

整个转换过程分两阶段进行。

第一阶段,令开关S1置于输入信号Ui一侧。

积分器对Ui进行固定时间T1的积分。

积分结束时积分器的输出电压为:

(7.4)

可见积分器的输出UO1与UI成正比。

这一过程称为转换电路对输入模拟电压的采样过程。

在采样开始时,逻辑控制电路将计数门打开,计数器计数。

当计数器达到满量程N时,计数器由全“1”复“0”,这个时间正好等于固定的积分时间T1。

计数器复“0”时,同时给出一个溢出脉冲(即进位脉冲)使控制逻辑电路发出信号,令开关S1转换至参考电压-VREF一侧,采样阶段结束。

第二阶段称为定速率积分过程,将UO1转换为成比例的时间间隔。

采样阶段结束时,一方面因参考电压-VREF的极性与UI相反,积分器向相反方向积分。

计数器由0开始计数,经过T2时间,积分器输出电压回升为零,过零比较器输出低电平,关闭计数门,计数器停止计数,同时通过逻辑控制电路使开关S1与uI相接,重复第一步。

如图10.1.11所示。

因此得到:

即

式表明,反向积分时间T2与输入模拟电压成正比。

在T2期间计数门G2打开,标准频率为fCP的时钟通过G2,计数器对UG计数,计数结果为D,由于

T1=N1TCP

T2=DTCP

则计数的脉冲数为

计数器中的数值就是AD转换器转换后数字量,至此即完成了VT转换。

若输入电压UI1<

UI,UO1<

UO1,则

,它们之间也都满足固定的比例关系,如图10.1.11所示。

图10.1.11双积分AD转换器波形图

双积分型A/D转换器若与逐次逼近型A/D转换器相比较,因有积分器的存在,积分器的输出只对输入信号的平均值有所响应,所以,它突出优点是工作性能比较稳定且抗干扰能力强;

由式以上分析可以看出,只要两次积分过程中积分器的时间常数相等,计数器的计数结果与RC无关,所以,该电路对RC精度的要求不高,而且电路的结构也比较简单。

双积分型A/D转换器属于低速型AD转换器,一次转换时间在1~2ms,而逐次比较型A/D转换器可达到1s。

不过在工业控制系统中的许多场合,毫秒级的转换时间已经足足有余,双积分型A/D转换器的优点正好有了用武之地。

(4)主要技术指标

◇转换精度

A/D转换器也采用分辨率和转换误差来描述转换精度。

分辨率是指引起输出数字量变动一个二进制码最低有效位(LSB)时,输入模拟量的最小变化量。

他反映了A/D转换器对输入模拟量微小变化的分辨能力。

在最大输入电压一定时,位数越多,量化单位越小,分辨率越高。

转换误差通常用输出误差的最大值形式给出,常用最低有效位的倍数表示,反映A/D转换器实际输出数字量和理论输出数字量之间的差异。

◇转换时间

转换时间是指转换控制信号(vL)到来,到A/D转换器输出端得到稳定的数字量所需要的时间。

转换时间与A/D转换器类型有关,並行比较型一般在几十个纳秒,逐次比较型在几十个微秒,双积分型在几十个毫秒数量级。

实际应用中,应根据数据位数、输入信号极性与范围、精度要求和采样频率等几个方面综合考虑A/D转换器的选用。

(5)集成A/D转换器及应用

集成A/D转换器品种繁多,选用时应综合各种因素选取集成芯片。

一般逐次比较型A/D转换器用得较多,ADC0804就是这类单片集成A/D转换器。

ADC0804釆用CMOS工艺20引脚集成芯片,分辨率为8位,转换时间为100μS,输入电压范围为0~5V。

芯片内具有三态输出数据锁存器,可直接接在数据总线上。

图10.1.12为ADC0804双排直立式封装引脚分布图。

各引脚名称及作用如下:

VIN+,VIN–:

模拟信号输入端。

D7~D0:

具有三态特性数字信号输出。

AGND:

模拟信号地。

DGND:

数字信号地。

CKLIN:

时钟信号输入端。

CLKR:

内部时钟发生器的外接电阻端。

CS:

低电平有效的片选端。

WR:

写信号输入,低电平启动A/D转换。

RD:

读信号输入,低电平输出端有效。

INTR:

A/D转换结束信号,低电平表示本次转换已完成。

VREF/2:

参考电平输入,决定量化单位

图10.1.12ADC0804管脚分布图

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 积分 AD 转换器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx