EDA技术实用教程课潘松后答案解答.docx

EDA技术实用教程课潘松后答案解答.docx

- 文档编号:26209136

- 上传时间:2023-06-17

- 格式:DOCX

- 页数:47

- 大小:395.03KB

EDA技术实用教程课潘松后答案解答.docx

《EDA技术实用教程课潘松后答案解答.docx》由会员分享,可在线阅读,更多相关《EDA技术实用教程课潘松后答案解答.docx(47页珍藏版)》请在冰豆网上搜索。

EDA技术实用教程课潘松后答案解答

《EDA技术实用教程》部分习题解答

习题四

习题4-5列表详细说明MAX+plusII中prim.mf和mega_lpm库中的内容和用法。

答:

prim:

基本的元件

mf:

主要是74系列芯片的逻辑元件

mega_lpm:

参数可定制的复杂逻辑元件

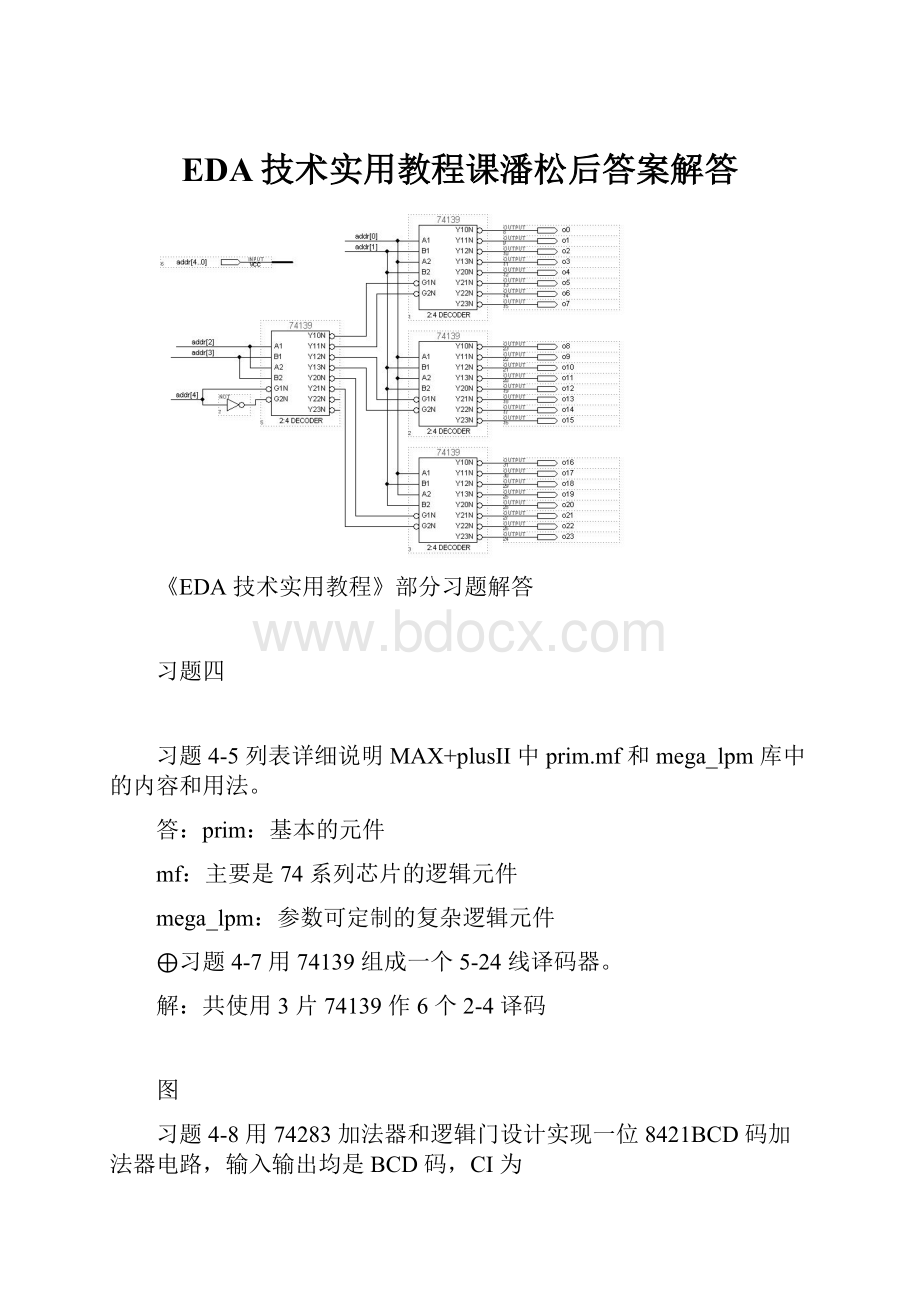

⊕习题4-7用74139组成一个5-24线译码器。

解:

共使用3片74139作6个2-4译码

图

习题4-8用74283加法器和逻辑门设计实现一位8421BCD码加法器电路,输入输出均是BCD码,CI为

低位的进位信号,CO为高位的进位信号,输入为两个1位十进制数A,输出用S表示。

解:

如果二进制的和大于9,需要再加上6来补成BCD码

2

第1章概述

图

习题4-9设计一个7人表决电路,参加表决者7人,同意为1,不同意为0,同意者过半则表决通过,绿

指示灯亮;表决不通过则红指示灯亮。

解:

方法有多种,仅举一例。

有多个1位全加器构成。

图

其中1位全加器的原理图如下:

图1位全加器

第1章概述

3

习题4-10使用prim和mf库中的元件设计一个周期性产生二进制序列01001011001的序列发生器,用移

位寄存器或用同步时序电路实现,并用时序仿真器验证其功能。

解:

给出一种解法

习题4-11用D触发器设计3位二进制加法计数器。

解:

注意D触发器级联时应取非端,否则只能作分频器

下图是异步计数器方式,同步计数器方式请读者自行考虑

习题4-12用D触发器构成按循环码(000->001->011->111->101->100->000)规律工作的六进制同步计数

器。

解:

用同步计数器来实现。

(事实上要求设计的是一个袼雷码计数器)

考虑不同状态时,对应的DFF输入端的值:

Q2Q1Q0

D2

D1

000

0

0

001

0

1

011

1

1

111

1

0

101

1

0

100

0

0

4

D0

D0=

1

Q

1

第1章概述

1

1

0

0

Q2+Q21

Q

D1=Q20

=

D2QQ

2Q0+Q21

4-13应用4位全加器和74374构成4位二进制加法计数器。

习题4-14用74194、74273、D触发器等器件组成8位串入并出的转换电路,要求在转换过程中数据不

变,只有当8位一组数据全部转换结束后,输出才变化一次。

第1章概述

×如果使用74299、74373、D触发器和非门来完成上述功能,应该有怎样的电路?

5

习题4-15用一片74163和2片74138构成一个具有12路脉冲输出的数据分配器。

要求在原理图上标明

第1路到第12路输出的位置。

74195代替以上的74163,完成同样的设计。

习题4-16用同步时序电路对串行二进制输入进行奇偶校验,每检测5位输入,输出一个结果:

当5位输

入中1的数目为奇数时,在最后一位的时刻输出1。

4-17用7490设计模为872的计数器,且输出的个位、十位、百位都应符合8421码权重。

习题4-18用74161设计一个97分频电路,用置0和置数两种方法实现。

6

第1章概述

图1

4-19某通信接收机的同步信号为巴克码1110010。

设计一个检测器,其输入为串行码x,输出为

检测结果y,当检测到巴克码时,输出1。

第1章概述

习题五

习题5-1画出与下例实体描述对应的原理图符号:

ENTITYbuf3sIS--实体1:

三态缓冲器

PORT(input:

INSTD_LOGIC;--输入端

enable:

INSTD_LOGIC;--使能端

output:

OUTSTD_LOGIC);--输出端

ENDbuf3x;

ENTITYmux21IS--实体2:

2选1多路选择器

PORT(in0,in1,sel:

INSTD_LOGIC;

output:

OUTSTD_LOGIC);

解:

7

习题5-2图5-19所示的是4选1多路选择器,试分别用IF_THEN语句和CASE语句的表达方式写出此

电路的VHDL程序,选择控制的信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=‘0’,s0=‘0’;

s1=‘0’,s0=‘1’;s1=‘1’,s0=‘0’和s1=‘1’,s0=‘1’分别执行y<=a、y<=b、y<=c、y<=d。

解:

使用IF…THEN语句:

process(s0,s1,a,b,c,d)begin

ifs0='0'ands1='0'then

y<=a;

elsifs0='1'ands1='0'then

y<=b;

elsifs0='0'ands1='1'then

y<=c;

else

y<=d;

endif;

endprocess;

使用CASE语句:

architecturehdlarchofmux41is

signalstmp:

std_logic_vector(1downto0);

begin

stmp<=s1&s0;

process(s0,s1,a,b,c,d)begin

8

casestmpis

when"00"=>y<=a;

when"01"=>y<=b;

when"10"=>y<=c;

whenothers=>y<=d;

endcase;

endprocess;

endhdlarch;

第1章概述

⊕习题5-3图5-20所示的是双2选1多路选择器构成的电路MUXK,对于其中MUX21A,当s=‘0’

和‘1’时,分别有y<=‘a’和y<=‘b’。

试在一个结构体中用两个进程来表达此电路,每个进程中用IF

语句描述一个2选1多路选择器MUX21A。

解:

图5-194选1多路选择器

图5-20双2选1多路选择器

architecturehdlarchofMUXKis

signaltmp:

std_logic;

begin

process(s0,a2,a3)begin

ifs0='0'then

tmp<=a2;

else

tmp<=a3;

endif;

endprocess;

process(s1,a1,tmp)begin

ifs1='0'then

outy<=a1;

else

outy<=tmp;

endif;

endprocess;

endhdlarch;

习题5-4图5-21是一个含有上升沿触发的D触发器的时序电路,试写出此电路的VHDL设计文件。

解:

VHDL设计文件内容如下:

libraryieee;

第1章概述

图5-21习题5-4图

9

useieee.std_logic_1164.all;

entityexenis

port(

cl

:

instd_logic;

clk0:

instd_logic;

out1:

outstd_logic

);

endentity;

architecturehdlarchofexenis

signaltmp:

std_logic;

begin

process(clk0)begin

ifrising_edge(clk0)then

tmp<=not(tmporcl);

endif;

endprocess;

out1<=nottmp;

endhdlarch;

⊕习题5-5给出1位全减器的VHDL描述。

要求:

(1)首先设计1位半减器,然后用例化语句将它们连接起来,图5-22中h_suber是半减器,diffr是输出差,

s_out是借位输出,sub_in是借位输入。

图5-22习题5-5图

(2)以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句和生成语句来完成此项设计(减

法运算是x–y–sub_in=diffr)。

10

解:

(1)

先设计一个半减器:

xy00

diff0

s_out0

libraryieee;

01

1

1

第1章概述

10

1

0

11

0

0

useieee.std_logic_1164.all;

entityh_suberis

port(

x,y:

instd_logic;

diff,s_out:

outstd_logic

);

endentity;

architecturehdlarchofh_suberis

begin

process(x,y)begin

diff<=xxory;

s_out<=(notx)andy;

endprocess;

endhdlarch;

1位全减器的VHDL设计文件:

suber.vhd

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYsuberIS

port(

x,y:

INSTD_LOGIC;

sub_in:

INSTD_LOGIC;

diffr:

OUTSTD_LOGIC;

sub_out:

OUTSTD_LOGIC

);

ENDsuber;

ARCHITECTUREscharchOFsuberIS

componenth_suber

PORT(x:

INSTD_LOGIC;

y:

INSTD_LOGIC;

);

第1章概述

diff:

OUTSTD_LOGIC;

s_out:

OUTSTD_LOGIC

11

endcomponent;

signalt0,t1,t2:

STD_LOGIC;

BEGIN

u1:

h_suber

PORTMAP(x=>x,

y=>y,

diff=>t0,

s_out=>t1);

u2:

h_suber

PORTMAP(x=>t0,

y=>sub_in,

diff=>diffr,

s_out=>t2);

sub_out<=t1ORt2;

END;

(2)8位减法器,关于生成语句可以参见第9章

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYsub8IS

port(

a:

INstd_logic_vector(7downto0);

b:

INstd_logic_vector(7downto0);

sin:

INSTD_LOGIC;

sout:

OUTSTD_LOGIC;

c:

OUTstd_logic_vector(7downto0)

);

ENDsub8;

ARCHITECTUREhdlarchOFsub8IS

componentsuber

PORT(x:

INSTD_LOGIC;

y:

INSTD_LOGIC;

sub_in:

INSTD_LOGIC;

diffr:

OUTSTD_LOGIC;

sub_out:

OUTSTD_LOGIC);

endcomponent;

12

第1章概述

signalstmp:

std_logic_vector(8downto0);

BEGIN

stmp(0)<=sin;

sout<=stmp(8);

gensub:

foriin0to7generate

u1:

suber

PORTMAP(x=>a(i),

y=>b(i),

sub_in=>stmp(i),

diffr=>c(i),

sub_out=>stmp(i+1));

endgenerate;

end;

习题5-6根据图5-23,写出顶层文件MX3256.VHD的VHDL设计文件。

图5-23习题5-6图

解:

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYMX3256IS

port(

INA:

INSTD_LOGIC;

INB:

INSTD_LOGIC;

INCK:

INSTD_LOGIC;

INC:

INSTD_LOGIC;

E:

OUTSTD_LOGIC;

OUT1:

OUTSTD_LOGIC

);

ENDMX3256;

第1章概述

ARCHITECTUREschtypeOFMX3256IS

componentLK35

PORT(A1:

INSTD_LOGIC;

A2:

INSTD_LOGIC;

CLK:

INSTD_LOGIC;

Q1:

OUTSTD_LOGIC;

Q2:

OUTSTD_LOGIC

);

endcomponent;

signalt1:

STD_LOGIC;

signalt2:

STD_LOGIC;

signalt3:

STD_LOGIC;

signalt4:

STD_LOGIC;

BEGIN

inst1:

lk35

PORTMAP(A1=>INA,

A2=>INB,

CLK=>INCK,

Q1=>t3,

Q2=>t2);

inst2:

lk35

PORTMAP(A1=>t2,

A2=>t1,

CLK=>INCK,

Q1=>t4,

Q2=>OUT1);

process(INCK,INC)

begin

if(INC='0')then

t1<='0';

elsif(rising_edge(INCK))then

t1<=t2;

endif;

endprocess;

e<=t4whent2='0'else

t3;

END;

13

14

第1章概述

习题六

习题6-5在VHDL设计中,给时序电路清0(复位)有两种方法,它们是什么?

答:

异步复位与同步清零

习题6-6在描述时序电路的进程中,哪一种复位方法必须将复位信号放在敏感信号表中?

给出这两种电路

的VHDL描述。

解:

异步复位:

process(clk,rst)begin

ifrst=‘1’then

cnt<=(others=>‘0’);

elsifrising_edge(clk)then

cnt<=cnt+1;

endif;

endprocess;

同步复位:

process(clk)begin

ifrising_edge(clk)then

ifrst=‘1’then

cnt<=(others=>‘0’);

else

cnt<=cnt+1;

endif;

endif;

endprocess;

习题6-8判断下面三个程序中是否有错误,若有则指出错误所在,并给出完整程序。

程序1:

SignalA,EN:

std_logic;

Process(A,EN)

VariableB:

std_logic;

Begin

ifEN=1thenB<=A;

endif;

endprocess;

程序2:

Architectureoneofsampleis

variablea,b,c:

integer;

begin

c<=a+b;

end;

程序3:

libraryieee;

useieee.std_logic_1164.all;

entitymux21is

第1章概述

15

port(a,b:

instd_logic;sel:

instd_logic;c:

outstd_logic;);

endsam2;

architectureoneofmux21is

begin

ifsel='0'thenc:

=a;

elsec:

=b;

endif;

endtwo;

解:

程序1:

变量B赋值错误,不能使用“<=”,应使用“:

=”

程序2:

变量声明错误,变量只能在process中声明,应改为signal

程序3:

if语句应该处于process中

习题6-9设计含有异步清零和计数使能的16位二进制减法计数器。

解:

设clr为异步清零端,en为计数使能端

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

USEieee.std_logic_arith.all;

ENTITYex6_9IS

port(

clk:

INSTD_LOGIC;

clr,en:

instd_logic;

cnt:

OUTstd_logic_vector(15downto0)

);

END;

ARCHITECTUREhdlarchOFex6_9IS

signalcnttmp:

std_logic_vector(15downto0);

BEGIN

process(clk,clr)begin

ifclr='1'then

cnttmp<=(others=>'0');

elsif(rising_edge(clk))then

ifen='1'then

cnttmp<=cnttmp+1;

endif;

endif;

16

endprocess;

cnt<=cnttmp;

END;

第1章概述

习题6-10设计8位左移移位寄存器,给出时序仿真波形。

解:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

USEieee.std_logic_arith.all;

ENTITYex6_10IS

port(

sck:

instd_logic;

sda:

instd_logic;

q:

outstd_logic_vector(7downto0)

);

END;

ARCHITECTUREhdlarchOFex6_10IS

signalshift:

std_logic_vector(7downto0);

BEGIN

process(sck)begin

if(rising_edge(sck))then

shift<=sda&shift(7downto1);

endif;

endprocess;

q<=shift;

END;

×\u20064X题6-11将例6-15中的4个IF语句分别用4个并列进程语句表达出来。

习题6-12参考例6-2、图6-1、例6-3和例6-22,用VHDL描述一个具有如图6-20功能的含计数使能、

异步复位和计数值并行预置功能的8位加法计数器。

解:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

USEieee.std_logic_arith.all;

ENTITYex6_12IS

port(

clk:

INSTD_LOGIC;

rst,load:

instd_logic;

d:

instd_logic_vector(3downto0);

);

END;

第1章概述

q:

OUTstd_logic_vector(3downto0);

cout:

outstd_logic

17

ARCHITECTUREhdlarchOFex6_12IS

signalcnt:

std_logic_vector(3downto0);

BEGIN

process(clk,rst)begin

ifrst='1'then

cnt<=(others=>'0');

elsif(rising_edge(clk))then

ifload='1'then

cnt<=d;

else

cnt<=cnt+1;

endif;

endif;

endprocess;

q<=cnt;

cout<=cnt(0)andcnt

(1)andcnt

(2)andcnt(3);

END;

习题七

习题7-1仿照例7-1,将例7-4用两个进程,即一个时序进程,一个组合进程表达出来。

习题7-2为确保例7-5的状态机输出信号没有毛刺,试用例7-4的方式构成一个单进程状态,使输

出信号得到可靠锁存,在相同输入信号条件下,给出两程序的仿真波形。

习题7-3序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收

到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出1,否则输出0。

由于这种检

测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在

连续的检测中所收到的每一位码都与预置数的对应码相同。

在检测过程中,任何一位不相等都将回到初始

状态重新开始检测。

例7-11描述的电路完成对序列数“11100101

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 技术 实用教程 课潘松后 答案 解答

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《初级会计实务》试题题库大全及答案详解.docx

《初级会计实务》试题题库大全及答案详解.docx