K60时钟分配中文.docx

K60时钟分配中文.docx

- 文档编号:26535847

- 上传时间:2023-06-20

- 格式:DOCX

- 页数:16

- 大小:133.80KB

K60时钟分配中文.docx

《K60时钟分配中文.docx》由会员分享,可在线阅读,更多相关《K60时钟分配中文.docx(16页珍藏版)》请在冰豆网上搜索。

K60时钟分配中文

第5章时钟分配

5.1概要

MCG模块主要控制用于产生系统时间的时钟源,时钟发生器将选择好的时钟源分成各种时钟域,包括系统主机时钟、系统从机时钟以及flash存储器时钟。

另外,时钟发生器可以为各个模块产生特定的时钟门,允许单独开关各个模块。

系统主时钟由MCGOUTCLK时钟产生。

时钟发生器电路提供多种分频因子,使设备的不同部分产生不同频率的时钟,这样以便做到功耗与性能之间的权衡。

各种模块(例如USBOTG控制器),都有其特定的模块时钟,这些时钟由MCGPLLCLK或MCGFLLCLK时钟产生。

除此之外,有些模块特定时钟的时钟源是可以更换的。

SIM模块的SOPT寄存器可以控制大多数模块的时钟。

5.2编程模型

时钟源的选择和混合是通过MCG模块来控制和编程的,而系统的时钟分频因子和模块时钟门是通过SIM模块来编程设置的。

详细信息参见具体的寄存器和位描述。

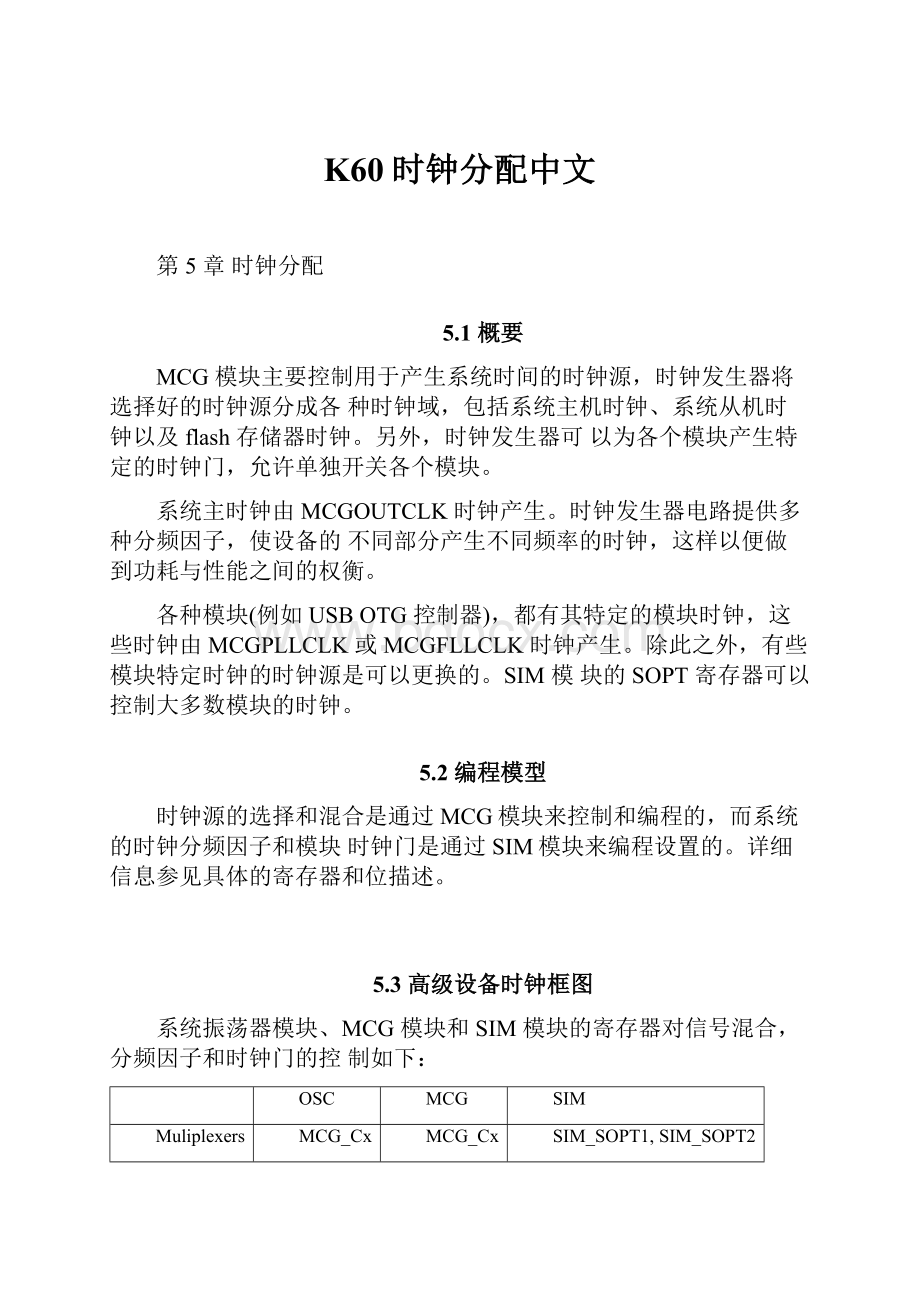

5.3高级设备时钟框图

系统振荡器模块、MCG模块和SIM模块的寄存器对信号混合,分频因子和时钟门的控制如下:

OSC

MCG

SIM

Muliplexers

MCG_Cx

MCG_Cx

SIM_SOPT1,SIM_SOPT2

Dividers

—

MCG_Cx

SIM_CLKDIVx

Clockgates

OSC_CR

MCG_C1

SIM_SCGCx

图5-1时钟框图

5.4时钟定义

下表描述了上面框图的时钟。

时钟名称

说明

核心时钟

MCGOUTCLK除以OUTDIV1为ARMCortexM4内核时钟

系统时钟

MCGOUTCLK除以OUTDIV1为交叉开关时钟和主设备总线直接连接到交叉处。

另外,这时钟用于串口UART0和UART1。

总线时钟

MCGOUTCLK除以OUTDIV2为从机总线和外围设备时钟(不含内存)。

FlexBus时钟

MCGOUTCLK除以OUTDIV3为外部FlexBus接口时钟。

Flash时钟

MCGOUTCLK除以OUTDIV4为闪存时钟

MCGIRCLK

内部参考时钟决定MCG输出的缓慢或快速

MCGFFCLK

慢内部参考时钟的MCG输出或者分频的MCG外部参考时钟

MCGOUTCLK

IRC、MCGFLLCLK、MCGPLLCLK或者MCG外部参考时钟控制MCG的输出。

外部参考时钟有内核、系统、总线、FlexBus、flash时钟。

它同时是调试追踪时钟。

MCGFLLCLK

FLL的MCG的输出。

MCGFLLCLK或者MCGPLLCLK为某些模块产生时钟。

MCGPLLCLK

PLL的MCG的输出。

MCGFLLCLK或者MCGPLLCLK为某些模块产生时钟。

MCG外部参考时钟

MCG的输入时钟由系统振荡器和RTC振荡器决定

OSCCLK

内部振荡器由系统振荡器输出,或者有EXTAL直接决定。

OSCERCLK

系统振荡器输出源于OSCCLK,OSCCLK可以是某些芯片模块的时钟。

OSC32KCLK

系统振荡器32kHz输出

ERCLK32K

可以选择OSC32KCLK时钟或者RTC时钟的某些模块的时钟源,

RTCclock

为RTC模块输出的RTC震荡输出

LPO

PMC1kHz输出

5.4.1设备时钟汇总

表5-1是芯片时钟的详细信息。

表5-1时钟汇总

时钟名

运行模式时钟频率

VLPR模式时钟频率

时钟源

何时时钟无效

MCGOUTCLK

达100MHz

达2MHz

MCG

在所有停止模式

内内核时钟

达100MHz

达2MHz

MCGOUTCLK时钟

在所有等待和停止模

分频

式

系统时钟

达100MHz

达2MHz

MCGOUTCLK时钟

分频

在所有停止模式

总线时钟

达50MHz

达2MHz

MCGOUTCLK时钟

分频

在所有停止模式

FlexBus时钟

(FB_CLK)

达50MHz

达2MHz

MCGOUTCLK时钟

分频

在所有停止模式或者FlexBus不使用

Flash时钟

达25MHz

达1MHz

MCGOUTCLK时钟

分频

在所有停止模式

内部参考

30-40kHz或者2MHz

2MHz

MCG_C1的

(MCGIRCLK)

[IRCLKEN]位清除,停

止模式和

MCG

MCG_C1[IREFSTEN]

位清除,或者

VLPS/LLS/VLLS模

式

外部参考

达50MHz,30-40kHz,

达4MHz,30-40

系统的OSC中

(OSCERCLK)

或者4-32MHz(晶振)

kHz(低范围晶振)

OSC_CR的

或者

达4MHz(高范围

系统OSC

[ERCLKEN]位清除,

或者停止模式和

晶振)

OSC_CR的

[EREFSTEN]位清零

外部参考32kHz(ERCLK32K)

30-40kHz

30-40kHz

系统OSC或者RTCOSC依赖于SIM_SOPT1的

系统OSC中

OSC_CR的

[ERCLKEN]位清除

[OSC32KSEL]位

或者RTC中

RTC_CR的[OSCE]清

除

RTC_CLKOUT

1Hz

1Hz

RTC时钟

LLSandVLLSx模式的时钟无效

LPO

1kHz

1kHz

PMC

在所有的电源模式都可用

USBFS时钟

48MHz

N/A

MCGPLLCLK或者

MCGFLLCLK的分

数分频器,或者

USB_CLKIN

USBFSOTG禁止

I2Smaster时钟

达50MHz

N/A

系统时钟,MCGPLLCLK,或者MCGFLLCLK的

分数分频器,OSCERCLK,或者I2S_CLKIN

I2S禁止

SDHC时钟

达50MHz

N/A

系统时钟,MCGPLLCLK/MCGFLLCLK,或者OSCERCLK

SDHC禁止

以太网RMII时钟

50MHz

N/A

OSCERCLK

以太网禁止

以太网IEEE1588

时钟

达100MHz

N/A

系统时钟,OSCERCLK,MCGPLLCLK/MCGFLLCLK,或者ENET_1588_CLKIN

以太网禁止

TRACE时钟

达100MHz

达2MHz

系统时钟或者

MCGOUTCLK

Trace禁止

5.5内部时钟需求

时钟分频器可以通过SIM模块的CLKDIV寄存器设置。

每个分频器的分频因子可编程设置,能选择一到十六。

配置此设备的时钟必须满足下列要求:

1.内核和系统时钟频率必须在100MHz以内。

2.总线时钟频率必须编程设置不大于50MHz,且是内核时钟的整数分频。

3.flash模块时钟频率必须编程设置不大于25MHz,且是总线时钟的整数分频。

4.FlexBus时钟频率必须编程设置成不大于总线时钟。

此设备的若干常用时钟配置如下:

选择1:

时钟

频率

内核时钟

50MHz

系统时钟

50MHz

总线时钟

50MHz

FlexBus时钟

50MHz

Flash时钟

25MHz

选择2:

时钟

频率

内核时钟

100MHz

系统时钟

100MHz

总线时钟

50MHz

FlexBus时钟

25MHz

Flash时钟

25MHz

选择3:

时钟

频率

内核时钟

96MHz

系统时钟

96MHz

总线时钟

48MHz

FlexBus时钟

48MHz

Flash时钟

24MHz

5.5.1复位后的时钟分频值

每个时钟分频器都可以通过SIM模块的CLKDIVn寄存器来设置分频因子。

Flash存储器的FTFL_OPT[LPBOOT]位可以控制内核时钟的复位值、系统时钟、总线时钟和flash时钟分频器。

如下表所示:

FTFL_OPT[LPBOOT]

内核/系统时钟

总线时钟

FlexBus时钟

Flash设置

描述

0

0x7(除以8)

0x7(除以8)

0xF(除以16)

0xF(除以16)

低功耗

1

0x0(除以1)

0x0(除以1)

0x1(除以2)

0x1(除以2)

快速时钟

这就可以使用户灵活选择地低频率和低功耗。

只要flash的FTFL_OPT[LPBOOT]位为逻辑1擦除查处默认状态,Flash擦除默认状态进入快速时钟模式。

可以通过向FTFL_OPT[LPBOOT]位写0来使能低功耗模式。

当复位时,如果LPBOOT位被清零,则系统就处于低时钟配置。

任何系统复位时,时钟分频因子都会返回到这个复位配置状态。

5.5.2VLPR模式时钟

在VLPR模式时,时钟分频因子不可改变,因此在进入VLPR模式前必须确保:

·内核/系统、FlexBus和总线时钟不大于2MHz

·flash存储时钟不大于1MHz。

5.6时钟门

通过SIM模块的SCGCx寄存器可以对每个模块的时钟进行单独的开和关,该寄存器会在复位时被清零,从而使得相应模块的时钟被禁止。

另外需要注意,在初始化相应的模块之前,需要先开启模块的时钟;在关闭模块的时钟之前,需确保模块已经被关闭了;对任何一个没有开启时钟的外设模块进行访问都会产生错误。

5.7模块时钟

表5-2为每个模块相关的时钟。

表5-2模块时钟

模块

总线接口时钟

内部时钟

I/O接口时钟

内核模块

ARMCortex-M4内核

系统时钟

内核时钟

—

NVIC

系统时钟

—

—

DAP

系统时钟

—

—

ITM

系统时钟

—

—

ETM

系统时钟

TRACE时钟

TRACE_CLKOUT

ETB

系统时钟

—

—

cJTAG,JTAGC

—

—

JTAG_CLK

系统模块

DMA

系统时钟

—

—

DMAMux

总线时钟

—

—

端口控制

总线时钟

LPO

—

交叉开关

系统时钟

—

—

外桥

系统时钟

总线时钟

—

MPU

系统时钟

—

—

LLWU,PMC,SIM

总线时钟

LPO

—

模式控制器

总线时钟

—

—

MCM

系统时钟

—

—

EWM

总线时钟

LPO

—

开门狗定时器

总线时钟

LPO

—

时钟

MCG

总线时钟

MCGOUTCLK,MCGPLLCLK,MCGFLLCLK,MCGIRCLK,OSCERCLK

—

OSC

总线时钟

OSCERCLK

—

存储器和存储器接口

Flash控制器

系统时钟

Flash时钟

—

Flash存储器

Flash时钟

—

—

FlexBus

系统时钟

—

FB_CLKOUT

EzPort

系统时钟

—

EZP_CLK

安全

CRC

总线时钟

—

—

MMCAU

系统时钟

—

—

RNGB

总线时钟

—

—

模拟信号

ADC

总线时钟

OSCERCLK

—

CMP

总线时钟

—

—

DAC

总线时钟

—

—

VREF

总线时钟

—

—

定时器

PDB

总线时钟

—

—

FlexTimers

总线时钟

MCGFFCLK

FTM_CLKINx

PIT

总线时钟

—

—

LPTimer

总线时钟

LPO,OSCERCLK,MCGIRCLK,ERCLK32K

—

CMT

总线时钟

—

—

RTC

总线时钟

EXTAL32K

—

通信接口

以太网

系统时钟,总线时钟

RMII时钟,IEEE1588时钟

MII_RXCLK,MII_TXCLK

USBOTG

系统时钟

USB时钟

—

USBDCD

总线时钟

—

—

FlexCAN

总线时钟

OSCERCLK

—

DSPI

总线时钟

—

DSPI_SCK

I2C

总线时钟

—

I2C_SCL

UART0,UART1

系统时钟

—

—

UART2-5

总线时钟

—

—

SDHC

系统时钟

SDHC时钟

SDHC_DCLK

I2S

总线时钟

I2S主设备时钟

I2S_TX_BCLK,I2S_RX_BCLK

人机接口

GPIO

系统时钟

—

—

TSI

总线时钟

LPO,ERCLK32K,MCGIRCLK

—

5.7.1PMC1-KHzLPO时钟

电源管理控制器(PMC)可以产生一个1KHz的时钟使能所有模式(包括低功耗模式)的操作。

该时钟通常被称作LPO时钟或者1-kHzLPO时钟。

5.7.2WDOG时钟

WDOG时钟如图5-2。

图5-2WDOG时钟发生器

5.7.3调试时钟

调试时钟如图5-3。

图5-3调试时钟发生器

5.7.4PORT数字过滤器时钟

数字过滤器时钟如图5-4:

图5-4端口时钟发生器

5.7.5LPTMR时钟

LPTMR可选时钟如图5-5:

图5-5LPTMR时钟发生器

5.7.6以太网时钟

·RMII时钟源须符合OSCERCLK,必须是50MHz。

·MII时钟是由外部引脚提供,必须是25MHz。

·IEEE1588时间戳产生于内部时钟最高达100MHz。

它的时段必须是纳秒的整数倍(例如:

10ns=100MHz,15ns=66.67MHz,20ns=50MHz)。

它的时钟如图5-6:

图5-6以太网IEEE1588时间戳模块时钟发生器

5.7.7USBOTG控制器时钟

USBFSOTG控制器是一个总线主机并连接到交叉开关,它的时钟连接到系统时钟。

USBOTG控制器的时钟需要48MHz,模块的时钟如图5-7:

图5-7USBOTG48MHz时钟源

5.7.8FlexCAN时钟

FlexCAN时钟如图5-8:

图5-8FlexCAN时钟

5.7.9UART时钟

UART0和UART1在内核/系统时钟的模式操作;这使UART0和UART1有很高的性能。

其他的UART模块时钟都来自于总线时钟。

5.7.10SDHC时钟

SDHC模块有四个可能外部时钟源,如图5-9:

图5-9SDHC时钟

5.7.11I²S时钟

除了总线时钟,I²S还有一个主时钟产生时钟源,这个时钟源的最大频率为50MHz。

这个主机时钟可以分频得到多个时钟,如图5-10:

图5-10I²S时钟

5.7.12TSI时钟

在激活模式下,TSI时钟如图5-11:

图5-11TSI时钟

在低功耗模式下,TSI时钟如图5-12:

图5-12TSI低功耗时钟

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- K60 时钟 分配 中文

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《C12343098汽轮机操作规程》要点.docx

《C12343098汽轮机操作规程》要点.docx