EDA课程设计数字秒表的设计.docx

EDA课程设计数字秒表的设计.docx

- 文档编号:438417

- 上传时间:2022-10-10

- 格式:DOCX

- 页数:17

- 大小:90.29KB

EDA课程设计数字秒表的设计.docx

《EDA课程设计数字秒表的设计.docx》由会员分享,可在线阅读,更多相关《EDA课程设计数字秒表的设计.docx(17页珍藏版)》请在冰豆网上搜索。

EDA课程设计数字秒表的设计

EDA课程设计报告

——数字秒表的设计

指导老师:

时间:

组员:

一、设计流程

1.文本编辑:

用Active-HDL的编译环境进行编写源代码,编译通过后,保存为.hdl文件

格式。

2.功能仿真:

将文件调入Active-HDL仿真环境里进行功能仿真,检查逻辑功能是否正确。

3.逻辑综合与物理实现:

将源代码调入ISE软件中,逻辑综合,管脚分配,下载到FPGA板上调试物理实现。

二、设计规划

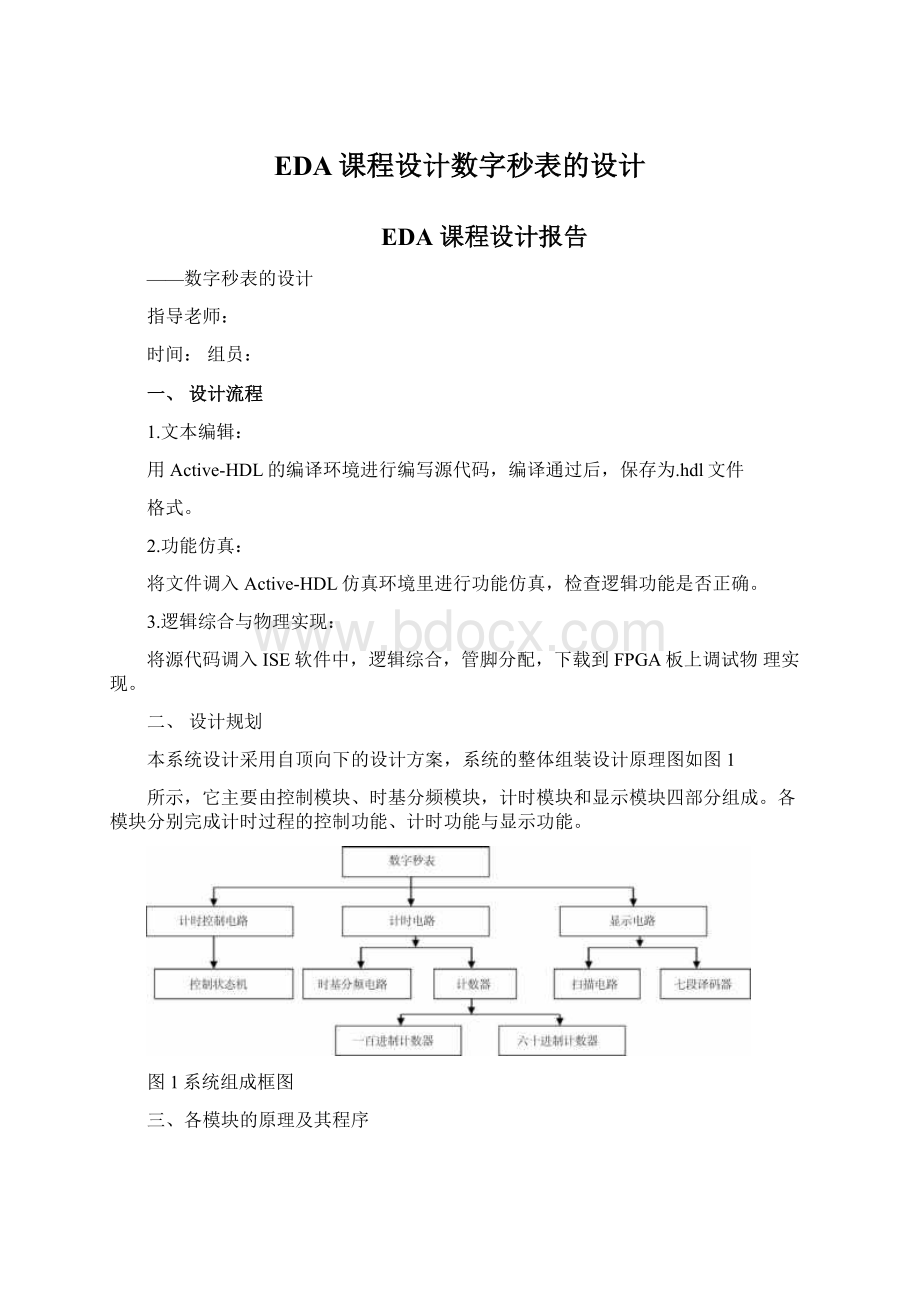

本系统设计采用自顶向下的设计方案,系统的整体组装设计原理图如图1

所示,它主要由控制模块、时基分频模块,计时模块和显示模块四部分组成。

各模块分别完成计时过程的控制功能、计时功能与显示功能。

图1系统组成框图

三、各模块的原理及其程序

本系统设计由控制模块、时基分频模块,计时模块和显示模块四部分组成。

各模块实现秒表不同的功能。

1、控制模块

计时模块的作用是针对计时过程进行控制。

计时控制模块可用俩个按钮来完

成秒表的启动、停止和复位。

部分源程序:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCTRLIS

PORT(CLR,CLK,SP:

INSTD_LOGIC;

EN:

OUTSTD_LOGIC);

COM:

PROCESS(SP,CURRENT_STATE)

BEGIN

ENDIF;

ENDPROCESS;

ENDBEHAVE;

2、时基分频模块

时基分频模块的作用把输入时钟信号变为分频输出信号。

部分源程序:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCB10IS

PORT(CLK:

INSTD_LOGIC;

CO:

OUTSTD_LOGIC);

ENDCB10;

ARCHITECTUREARTOFCB10IS

SIGNALCOUNT:

STD_LOGIC_VECTOR(3DOWNTO0);BEGIN

PROCESS(CLK)

BEGIN

IFRISING_EDGE(CLK)THEN

IFCOUNT="1001"THEN

COUNT<="0000";

CO<='1';

ELSE

COUNT<=COUNT+1;

CO<='0';

ENDIF;

ENDIF;

ENDPROCESS;

ENDART;

3、计时模块计时模块执行计时功能,计时方法和计算机一样是对标准时钟脉冲计数。

他是由四个十进制计数器和俩个六进制计数器构成,其中毫秒位、十毫秒位、秒位和分位采用十进制计数器,十秒位和十分位采用六进制计数器。

部分源程序:

十进制计数器:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCDU10IS

PORT(CLK:

INSTD_LOGIC;

CLR,EN:

INSTD_LOGIC;

CN:

OUTSTD_LOGIC;

COUNT10:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCDU10;

ENDIF;

ENDIF;

ENDPROCESS;

ENDART;

六进制计数器:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCDU6IS

ENDIF;

ENDIF;

ENDPROCESS;

ENDART;

计数器:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCOUNTIS

ENDART;

4、显示模块

计时显示电路的作用是将计时值在LED数码管上显示出来。

计时电路产生的

值经过BCDt段译码后,驱动LED数码管。

计时显示电路的实现方案采用扫描显示。

部分源程序:

数据选择器:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYMULXIS

PORT(CLK,CLR,EN:

INSTD_LOGIC;

S_1MS:

INSTD_LOGIC_VECTOR(3DOWNTO0);S_10MS:

INSTD_LOGIC_VECTOR(3DOWNTO0);S_100MS:

INSTD_LOGIC_VECTOR(3DOWNTO0);S_1S:

INSTD_LOGIC_VECTOR(3DOWNTO0);S_10S:

INSTD_LOGIC_VECTOR(3DOWNTO0);M_1MIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);M_10MIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);HOUR:

INSTD_LOGIC_VECTOR(3DOWNTO0);OUTBCD:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);SEG:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDMULX;

ARCHITECTUREARTOFMULXISSIGNALCOUNT:

STD_LOGIC_VECTOR(3DOWNTO0);

ENDCASE;

ENDIF;

ENDPROCESS;

ENDART;

BCD七段译码器:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYBCD7IS

PORT(

BCD:

INSTD_LOGIC_VECTOR(3DOWNTO0);

LED:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDBCD7;

ARCHITECTUREARTOFBCD7IS

BEGIN

LED<="1111110"WHENBCD="0000"ELSE

"0110000"WHENBCD="0001"ELSE

"1101101"WHENBCD="0010"ELSE

"1111001"WHENBCD="0011"ELSE"0110011"WHENBCD="0100"ELSE"1011011"WHENBCD="0101"ELSE"1011111"WHENBCD="0110"ELSE"1110000"WHENBCD="0111"ELSE"1111111"WHENBCD="1000"ELSE"1111011"WHENBCD="1001"ELSE"0000000";

ENDART;

四、系统仿真

1、时基分频模块的仿真

期com

^UJLN'HI

分析:

CLK为时钟信号的输入,CO为分频输出信号。

2、控制模块的仿真

YalueStmulaUr

i■T■■1u?

)■7■ik«■1w~T■砌二,抑•"T即q;哪

0

0Qxk

巧P

;

0iChk

TT^^rr^LrLm^n

i

0[

JL

J_LJL」L111

分析:

CLKCLR和SP为输入信号,EN为输出信号

3、计时电路模块的仿真(如图4-3〜图4-5所示)十进制计数器的仿真

六进制计数器的仿真

I-EM

Stiinflatare(o■riali■22Mi聊■ssoo»±Bp(«•】电xisodiiijsoid■vooi

Ferula

"■EH

jo

二X

]

inririrn1

-£OOUNIB

諳

一愎施醜葩懑©報®羽

2

L朋無阳趣宓懣陋密®说®SS®僦

计数器的仿真

分析:

elk为时钟脉冲脉冲,s_1ms是毫秒计数值,s_10ms是十毫秒计数器,s_100ms是百毫秒计数器,s_1s是秒计数器,s_10s是十秒计数器,m_1min是分计数器,s_10min是十分计数器,hour是小时计数器。

它们均为输入信号。

每来两个时钟脉冲,s_1ms加1,当s_1ms满十时,s_10ms加1,依次类推,s_10ms满十的时候,s_100ms加1等等作为输出。

4、显示电路模块的仿真(如图4-6〜图4-7所示)数据选择器的仿真

BCD七段译码器驱动器的仿真

分析:

bed为时钟脉冲输入信号,led是输出信号,如图所示:

当输出为“1111110”时候,输入为“0000”;当输出为“0110000”时输入“0001”,当输入为“0010”时输出为“1101101”,当输入为“0011”时输出为“1111001”等等来实现七段译码功能。

5、数字秒表整个系统的仿真

faie

„tLid.ilD(r

1.IM.1..1■期,1.^00.1.SOO.1.GOO.1.mo.1.EflD.1,肌,■.KOI.■.

叭F

0

F>ua

►CLR

h

Frnnh

1

j

Oock

*C0

L__

-flL£0

L

■兀

-*OUFO

no

色:

:

数字秒表起始工作的仿真图状态仿真图

分析:

秒表开始从零开始计数,每次增加10ms工作正常。

五、ISE软件物理实现

打开ISE软件,创建项目工程,将源程序带入综合,然后定义输入输出管脚约束,设计实现。

下载到FPGA板子上,可以观察到设计的数字秒表可以按照设计要求正常工作。

至此,整个课程设计完成。

六、结束语

开始做设计时总是会犯一些错误,只有经过不停的改错不停的编译得到正确的程序说明了作为软件编程人员是不能粗心大意的,一个程序的质量的高低与你细心与否有着一定的联系。

在编程时,应充分使用了结构化的思想,这样程序检查起来也比较方便,调试时也给了我很大方便,只要一个模块一个模块的进行调就可以了,充分体现了结构化编程的优势。

在设计中要求我要有耐心和毅力,还要细心,稍有不慎,一个小小的错误就会导致结果的不正确,而对错误的检查要求我要有足够的耐心,通过这次设计和设计中遇到的问题,也积累了一定的经验,对以后从事集成电路设计工作会有一定的帮助。

在应用VHDL的过程中让我真正领会到了其并行运行与其他软件顺序执行的差别及其在电路设计上的优越性。

用Active-HDL硬件描述语言的形式来进行数字系统的设计方便灵活,利用EDA软件进行编译优化仿真极大地减少了电路设计时间和可能发生的错误,降低了开发成本,这种设计方法在数字系统设计中发挥越来越重要的作用。

附录源程序如下:

1.时基分频模块的源程序(CB10.VHD)

LIBRARYIEEE

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 课程设计 数字 秒表 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《稻草人》精彩读书笔记精选多篇.docx

《稻草人》精彩读书笔记精选多篇.docx