集成电路课程设计报告B09212张波4021232.docx

集成电路课程设计报告B09212张波4021232.docx

- 文档编号:5200121

- 上传时间:2022-12-13

- 格式:DOCX

- 页数:8

- 大小:810.29KB

集成电路课程设计报告B09212张波4021232.docx

《集成电路课程设计报告B09212张波4021232.docx》由会员分享,可在线阅读,更多相关《集成电路课程设计报告B09212张波4021232.docx(8页珍藏版)》请在冰豆网上搜索。

集成电路课程设计报告B09212张波4021232

北华航天工业学院

课程设计报告(论文)

设计课题:

D触发器版图设计与

Hspice仿真

专业班级:

电子信息工程B09212

学生姓名:

张波

指导教师:

姚晓琼王玉峰

设计时间:

2012年6月

北华航天工业学院电子工程系

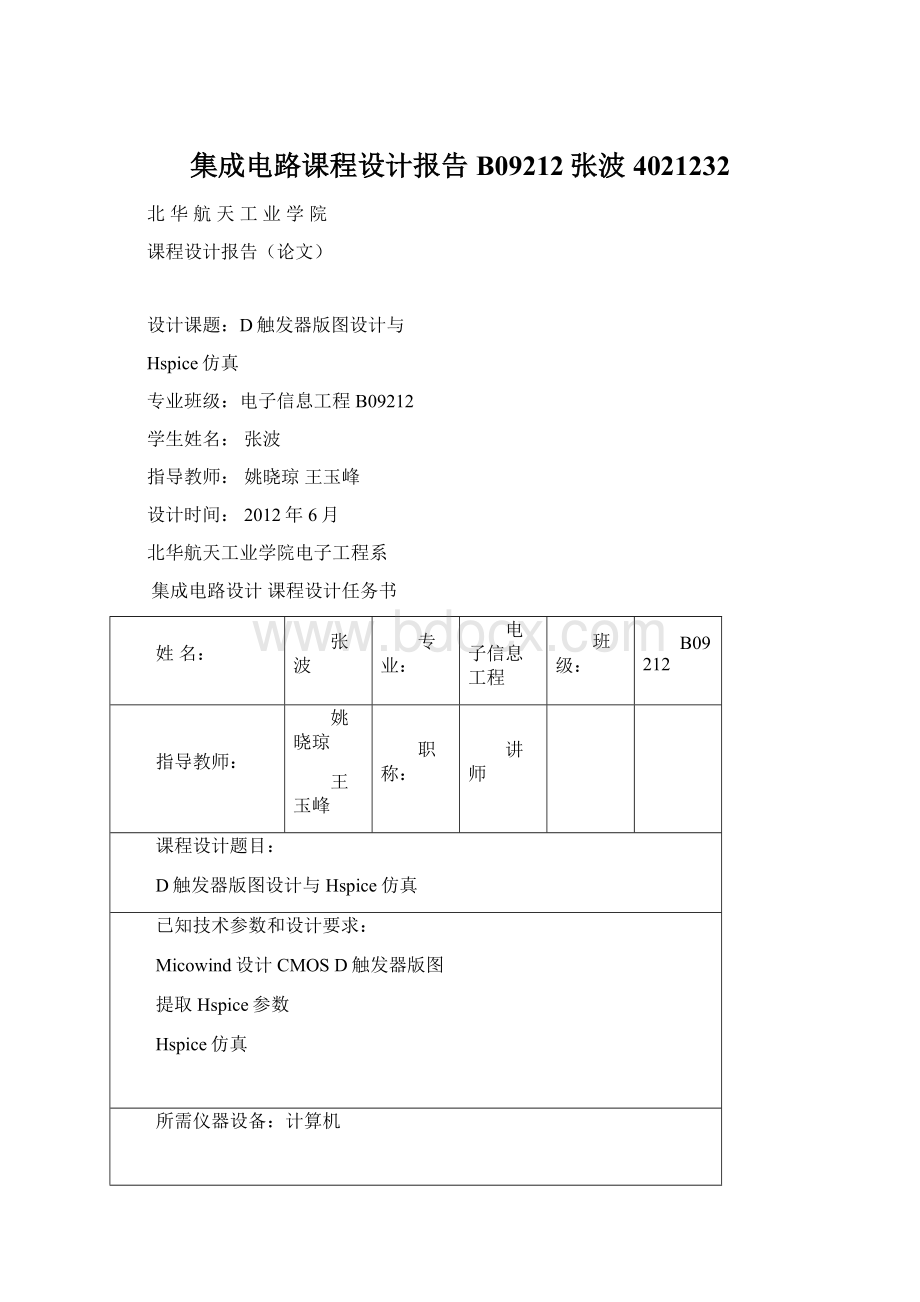

集成电路设计课程设计任务书

姓名:

张波

专业:

电子信息工程

班级:

B09212

指导教师:

姚晓琼

王玉峰

职称:

讲师

课程设计题目:

D触发器版图设计与Hspice仿真

已知技术参数和设计要求:

Micowind设计CMOSD触发器版图

提取Hspice参数

Hspice仿真

所需仪器设备:

计算机

成果验收形式:

版图,HSPICE仿真

参考文献:

《半导体集成电路》朱正涌清华大学出版社

《Hspice说明文档》

时间

安排

十七周版图设计

十八周Hspice仿真

指导教师:

教研室主任:

年月日

注:

本表下发学生一份,指导教师一份,栏目不够时请另附页。

课程设计任务书装订于设计计算说明书(或论文)封面之后,目录页之前。

内容摘要

越来越多的电子电路都在使用MOS管,特别是在音响领域更是如此。

MOS管与普通晶体管相比具有输入阻抗高、噪声系数小、热稳定性好、动态范围大等优点,且它是一种压控器件,有与电子管相似的传输特性,因而在集成电路中也得到了广泛的应用。

索引关键词:

MOS管晶体管集成电路传输特性

目录

一概述………………………………………………………………1

二方案设计与论证……………………………………………………………2

三单元电路设计与参数计算…………………………………………………3

3.1.从机部分电源设计……………………………………………………13

3.1.1开关电源介绍………………………………………………………14

3.1.2TOPSwitch系列芯片工作原理……………………………………15

3.1.3开关电源的电路设计……………………………………………16

四总原理图及元器件清单

五安装与调试

(一般分静态调试与动态调试两大内容)

六性能测试与分析

(要围绕设计要求中的各项指标进行)

七结论

八心得体会

九参考文献

1、概述

MOS场效应晶体管的核心结构是由导体、绝缘体与构成管子衬底的掺杂半导体这三层材料叠在一起组成的。

利用这一结构的作用是在半导体的表面感应出与原掺杂类型相反的载流子,形成一条导电沟道。

根据载流子的不同,利用电子作为载流子来导电的为N型MOS管,即NMOS;利用空穴作为载流子来导电的为P型MOS管,即PMOS。

利用NMOS和PMOS等不同组合可以组成反相器、与非门等各种CMOS传输门电路。

D触发器主要由CMOS传输门组成的反相器和与非门组成,具有置低电平和置高电平的功能。

当CLK为高电平时,传输门TG1导通、TG2截止,此时输出与D输入状态相同。

而且,在CLK为高电平的全部时间里Q端的状态始终跟随D端的状态而改变。

在CLK回到低电平状态以后,TG2导通、TG1截止。

由于反相器G1输入电容的存储效应,短时间内G1输入端仍然保持为TG1截止以前瞬间的状态,而且这时反相器G1、G2和传输门TG2形成了状态自锁的闭合回路,所以Q和Q’的状态被保存下来。

若D为高电平,则CLK变为高电平以后触发器被置成Q为高电平,CLK回到低电平以后触发器保持高电平状态不变。

若D为低电平,则CLK变为高电平以后触发器被置成Q为低电平,CLK回到低电平状态以后触发器保持低电平状态不变。

因其工作在电平触发方式下,所以同样具有电平触发的动作特点。

本次课程设计是设计CMOS传输门D触发器,主要要求如下:

1、利用Micowind设计CMOSD触发器版图;

2、提取Hspice参数

3、利用Hspice对电路进行仿真

二、方案设计与论证

由MOS管的特性可以看出,可用CMOS传输门构成D触发器,其逻辑图、电路图如下图(a)、图(b)。

当@=1时,传输门TG1导通,TG2截止,因而Q=D。

@=0时,TG1截止,TG2导通,这时两个反相器通过传输门TG2构成反馈环,保存了在@=1时输入的信息。

此电路最简单的电气设计是选取kN=kP和VTH=VDD/2,最简单的版图布局结构则选取所有器件有相同的宽长比W/L。

3、单元电路设计与参数计算

用CMOS传输门构成的D触发器由CMOS传输门和CMOS反相器构组成。

CMOS传输门是由一个PMOS和一个NMOS并联组成,CMOS反相器是由一个PMOS和一个NMOS共栅极级联而成。

注意其中PMOS和NMOS的衬底是分开的,PMOS的衬底接Vdd,NMOS的衬底接地。

其对应的电路图和版图分别如图(c)(d)和(e)(f)。

(c)(d)

(e)(f)

在观察波形时,反复适当的调节输入脉冲源的各时间值使观察到的输出波形尽可能地达到理想的理论波形图。

4、总原理图及元器件清单

1、CMOSD触发器总原理图版图如图(g)

(g)

2、元件清单

元件序号

型号

主要参数

数量

备注

TG1

TG2

G1

G2

5、仿真与调试

这次课设采用的Hspice仿真,其仿真对应输入输出波形如下:

六、性能测试与分析

7、结论

通过用Hspice对Microwind设计的CMOSD触发器的版图进行高解析度仿真后,由输出与输入波形对比可以看出,当传输门TG1导通、TG2截止时,输出Q的状态与输入D的状态一致,即Q=D;当传输门TG1截止、TG2导通时,输出Q保持上一时刻状态不变。

实现了D触发器的传输功能。

8、心得体会

通过本次集成电路课程设计,我收获良多。

感觉课程设计不仅体现了一个人的独立学习能力,同时也体现了一个集体团结协作的能力。

在平时的实验课上,我们只是学着如何根据电路图设计对应的版图,并没有要求仿真。

对于版图的设计来说只要平时实验课上自己动手做了,这次课设难度适宜,而难点在于仿真软件的学习,通过自行学习Hspice仿真软件,对所设计的版图进行仿真。

并对其进行了深入的了解,通过本次课设我学会了集成电路Hspice仿真软件。

学会了如何应用,,自己的动手绘图能力也得到了提升,感觉这次课设使我们的知道得到了很大的提高。

感谢姚晓琼老师的悉心指导和帮助!

!

!

九、参考文献

[1]胡宴如.高频电子线路[M].高教出版社.2001.9:

12-19

[2]卢屹数字锁相环的参数设计及其应用[J]通信技术2001,(9):

12-15

电子工程系集成电路课程设计成绩评定表

专业:

电子信息工程班级:

B09212学号:

20094021232姓名:

张波

课题名称

设计任务与要求

指导教师评语

建议成绩:

指导教师:

课程小组评定

评定成绩:

课程负责人:

年月日

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 集成电路 课程设计 报告 B09212 4021232

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx

心脏超声检查PPT幻灯片.ppt

心脏超声检查PPT幻灯片.ppt