dm6467中文.docx

dm6467中文.docx

- 文档编号:5800617

- 上传时间:2023-01-01

- 格式:DOCX

- 页数:8

- 大小:83.16KB

dm6467中文.docx

《dm6467中文.docx》由会员分享,可在线阅读,更多相关《dm6467中文.docx(8页珍藏版)》请在冰豆网上搜索。

dm6467中文

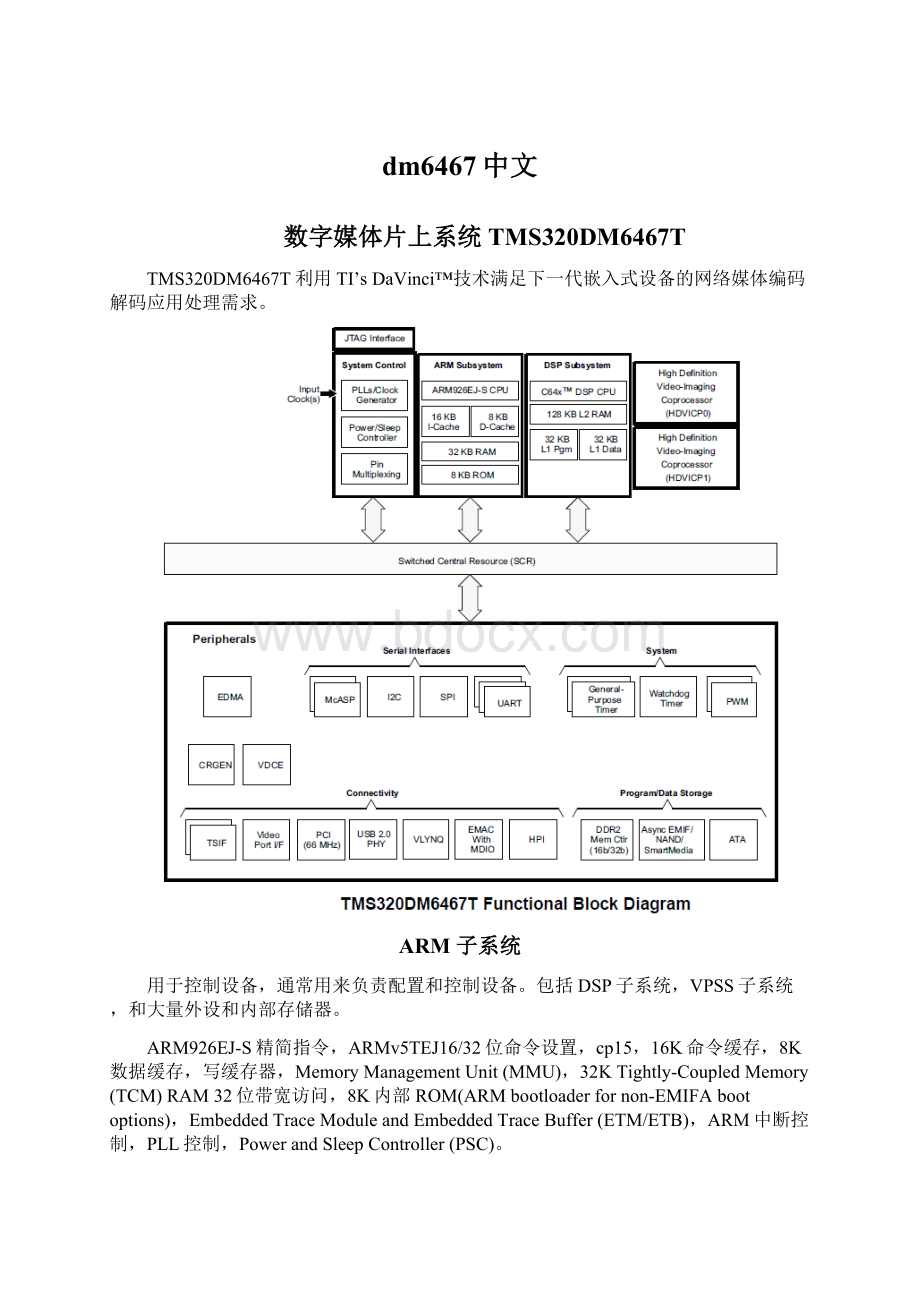

数字媒体片上系统TMS320DM6467T

TMS320DM6467T利用TI’sDaVinci™技术满足下一代嵌入式设备的网络媒体编码解码应用处理需求。

ARM子系统

用于控制设备,通常用来负责配置和控制设备。

包括DSP子系统,VPSS子系统,和大量外设和内部存储器。

ARM926EJ-S精简指令,ARMv5TEJ16/32位命令设置,cp15,16K命令缓存,8K数据缓存,写缓存器,MemoryManagementUnit(MMU),32KTightly-CoupledMemory(TCM)RAM32位带宽访问,8K内部ROM(ARMbootloaderfornon-EMIFAbootoptions),EmbeddedTraceModuleandEmbeddedTraceBuffer(ETM/ETB),ARM中断控制,PLL控制,PowerandSleepController(PSC)。

DSP子系统

C64x+CPU8个功能单元,两个寄存器文件,两个数据路径,两个通用寄存器文件(A,B)每个包含32个32bit寄存器。

通用寄存器可以用于数据或数据地址指针。

数据类型支持包括8,16,32,40,64位数据包.值大于32位,比如40位或64位长数值存储于寄存器对,伴随32LSB的数据空间在偶寄存器,包含8或32MSB的再下个较高的寄存器(奇数寄存器)。

八个功能单元(.M1,.L1,.D1,.S1,.M2,.L2,.D2,and.S2)每个时钟周期执行一个命令,.M用于执行乘积运算,.S和.L用于算术运算,逻辑运算和分支功能。

.D单元主要用于从储存器向寄存器装载数据和将寄存器得结果存入储存器。

设备的配置

电源供应

DM6467T包含一个内核提供(CVDD),两个I/O提供(DVDD33和DVDDR2),为确保设备正确的操作,特定的上电顺序如下。

CVDD在DVDDR2之前,DVDDR2在DVDD33之前上电,DVSSR2电压值不得超过CVDD,同样,DVDD33不能超过DVDDR2.

电源上电开始,所有的电源提供必需在200ms内达稳定。

稳定指的是达到操作情况要求。

复位

Power-onReset(POR)POR\pin芯片复位POR\必须置低

WarmResetRESETpin复位除仿真逻辑外的所有芯片

MaxReset类似于WarmReset,Emulator,WDTimer(Timer2)除去DM6467T设备启动和管脚设置不重新锁定

SystemResetEmulator保持存储器内容复位测试和仿真电路,DM6467T设备启动和管脚设置不重新锁定

C64x+LocalReset(DSPReset)Software(registerbit)MMR控制C64x+输入复位。

用于ARM控制C64x+复位。

复位时C64x+从DMA端口仍然有效

中断

SRMCPU中断

ARM926CPU核支持2个直接的中断:

FIQ和IRQ。

ARM中断控制优先处理超过64个中断请求来自不同的外围设备和子系统,和ARMCPU的中断。

每个中断可以编程为超过8个优先级,6个IRQ和2个FIQ。

DSP中断

C64x+DSP中断控制12个优先处理中断。

中断控制器控制普通CPU中断,NMI,和仿真中断。

外部存储器接口(EMIF)

●异步EMIFA用于NORFlash,SRAM等

●NANDFLASH

●ATA

异步EMIFA

提供8位和16位的数据总线,地址总线宽度大于24位,4芯片选择,通过存储器控制信号。

这些信号被以下外围设备多路复用

•EMIFAandNANDinterfaces

•ATAinterface

•Host-PortInterface(HPI)

•PCI

•GPIO

DDR2存储器控制器

DDR2存储器控制器接口专用于DDR2SDRAM,可用于16位或32位DDR2SDRAM设备

VIDEO端接口(VPIF)

允许捕捉或显示视频流

●150-MHZVPIF

●超过2个视频捕捉通道

-两个8位Standard-DefinitionSD视频BT.656

-单个16位High-Definition(HD)视频BT.1120

-单个RAW视频(8-/10-/12-bit)

●超过两个视频显示通道

-两个8位Standard-DefinitionSD视频显示BT.656

-单个16位High-Definition(HD)视频显示BT.1120

传送数据流接口(TSIF)

两个独立的接口(TSIF0和TSIF1)和相应的时钟发生器(CRGEN)为系统提供时钟。

●1位串行和8位并行独立接收和发送接口同步或异步模式(TSIF1只支持串行模式)。

●数据流I/O速率通过I/O时钟速度设置

●ATS(absolutetimestamp)发现,纠正,增加模式

视频数据变换引擎(VDCE)

4:

2:

2到4:

2:

0变换和4:

2:

0到4:

2:

2变换

PeripheralComponentInterconnect(PCI)

外围部件互联

ManagementDataInput/Output(MDIO)

HPI

32-or16-bit并行端口主处理器可以直接访问CPU存储空间。

可以和CPU交换数据,也可以访问外围设备的存储空间。

USB2.0

●速度high-speed(HS:

480Mb/s)和full-speed(FS:

12Mb/s)

●USB2.0host在HS,FS,和lowspeed(LS:

1.5Mb/s)

●4Transmit(TX)and4Receive(RX)

●FIFORAM

4KendpointProgrammablesize

–连接UTMI+PHY60-MHz,8-bit接口

–外部5v电源提供VBUS,在主操作模式直接利用USB控制器经过专用信号使能

串行外围接口SPI

Spi是一个高速同步串行I/O口允许串行数据流编程长度为2到16位输出或输入设备在一个编好的传输频率下。

用于芯片和外围设备的通信。

UART通用异步收发器

串转并用于数据接收从外围器件,并转串数据从CPU接收。

Inter-IntegratedCircuit(I2C)

●兼容PhilipsI2C规格修订版本2.1

●标准和快速模式从10-400kbps

●噪声滤波器消除噪声低于50ns

●7和10位的设备地址模式

●主从收发功能

●DMA,中断,或轮流检测

●Slew-RateLimitedOpen-DrainOutputBuffers

脉宽调节器(PWM)

提供一种方法为产生周期脉冲波形自动控制或作为数模转换器和一些外围器件。

定时器

4种模式操作:

64位通用定时器(GP),两部分非链状32位GP定时器,两部分链状定时器,或者一个看门狗定时器。

GP可用于产生周期中断或EDMA同步事件,看门狗定时器用于提供一个恢复机制为设备在错误的情况下,例如死循环。

三个64位通用定时器:

164位向上计数

2定时模式:

●64位通用定时模式(TIMER0TIMER1)

●二重32位通用定时器模式

●看门狗定时器模式(TIMER2)(主要通过ARM控制)

3两个可用时钟资源

●内部时钟

●外部时钟输入经过定时器输入脚TINP0U,TINP0L,和TINP1L(Timer0and1only)

4两个操作模式

●定时器运行一个时期然后停止

●持续操作(定时器自动复位在每个时期)

5产生中断给DSP和ARMCPU

6产生同步事件给EDMA

7在看门狗定时溢出时自动复位所有设备(仅TIMER2)

通用I/O(GPIO)

GPIO可配置为输入或输出,当设置为输出时,写入一个内部寄存器可以控制输出脚的状态。

当设置为输入,读内部寄存器可以发现输入的状态。

另外,GPIO外围设备可以产生CPU中断和EDMA事件在不同的中断时间产生模式。

IEEE1149.1JTAG

JTAG用于BSDL测试和DM6467T设备仿真。

TRST\仅需释放当需要用JTAG控制器仿真设备或边界扫描功能。

RESET\须释放边界扫描JTAG正确读取IDCODE各个区域。

其余边界扫描命令正确的独立工作在当前的RESET\状态。

DM6467T有一个内部下拉(PID)在TRST\脚以确保TRST\以致有效在上电时,这样设备内部仿真逻辑将被正确的初始化。

TI的JTAG控制器驱动TRST\为高。

但是,一些第三方JTAG控制器可能没有将TRST\驱动为高除非用上拉电阻在TRST\.当用这种JTAG控制器时,使能TRST\初始化设备后上电和外部驱动TRST\高在仿真或边界扫描操作。

DEVICECONFIGURATION

系统模块寄存器

电源因素

提供了多种手段来节约能量消耗,DM6467T有一个单电源domain-“AlwaysOn”powerdomain。

Dm6467t利用本地时钟门控经由PowerandSleepController(PSC)来获得电源的节约。

Note:

为了节能,所有的3.3vI/O缓冲器都默认关电。

在使用这些管脚之前,用户必须编码VDD3P3V_PWDNregister位的I/O缓冲器上电。

Note:

VDD3P3V_PWDNregister只用来控制I/O缓冲器的电源,PowerandSleepController(PSC)决定外围设备clock/power状态。

时钟因素

全部内部设备和外围设备时钟由PLL控制器PLLC1andPLLC2和PowerandSleepController(PSC)控制。

另外,SystemModuleVideoClockControl(VIDCLKCTL),

TSIFControl(TSIFCTL)和ClockandOscillatorControl(CLKCTL)registers配置时钟资源VPIF,TSIF,CRGEN设备和辅助振荡器。

选择Video,TSIF,和CRGEN模块输入时钟用SystemModuleVideoSourceClock设置失效。

Note:

为确保glitch-free操作,时钟必须在改变时钟资源频率或涉及VIDCLKCTL和TSIFCTL单元前失效。

设备复位后,用户要配置PLLControllers(PLLC1andPLLC2)andthePowerandSleepController(PSC)来给设备合适的时钟频率和合适的外围设备时钟状态(时钟是否门控)每个模块时钟和复位的状态通过PowerandSleepController(PSC)寄存器控制。

DM6467T有四个模块状态-Enable,Disable,SyncReset,orSwRstDisable。

时钟控制

通过以下寄存器VPIF(Video)/TSIFclockcontrolandclockdisableegistersandtheClockandOscillatorcontrolregister。

启动顺序

启动顺序是一个进程,哪个设备存储器装载了程序和数据,且一些设备内部寄存器配置合适的预设值。

启动时钟频率自动开始在每个设备全部复位之后。

启动模式

LatchingBootandConfigurationins.

•BTMODE[3:

0]

•PCIEN

•CS2BW

•DSPBOOT

TMS320DM646xDMSoCARM可以启动从EMIF/NORFlash或从ARMROM,作为定义设备启动和配置管脚复位时(BTMODE[3:

0]andPCIEN),PCIENpin配置用于选择EMIFA/PCI/HPIpin默认配置在复位时,这允许DM646xTDMSoC作为PCI元件在复位时,当PCIEN=1,PCI模块控制复用脚通过合适的上拉或下拉配置。

作为其他的启动模式(非PCI),PCIEN必须清零。

DSPBOOTADDR(包含了dsp复位向量高22位),BOOTCMPLT,BOOTCMD,andBOOTCFG(只读)用于控制启动和配置设备。

复位配置

一些设备配置定义在复位时。

EMIFACS2BusWidth(CS2BW)第一个EMIFA芯片选择空间(CS2)被CS2BW的值所决定。

如果CS2BW=0,这个空间默认为8位宽,CS2BW=1,默认为16位宽。

允许ARM全部使用位宽在设备从EMIFA启动时。

PCI使能(PCIEN)

如果PCI外设被此设备利用,PCIEN管脚配置确定。

如果PCIEN=1指示PCI被用,此时PCI复用脚为PCI功能。

同时该脚相应的内部上拉或下拉电阻被失效。

PCIEN=0指示PCI没使用,PCI单元管脚默认为非PCI功能(可能是EMIFAorHPI功能)并且该脚内的上下拉电阻使能。

PCIEN设置采集和存储在BOOTCFG.PCIEN位也在PINMUX0.PCIEN位。

DSP启动DSPBOOT

DSPBOOT输入决定DSP操作在复位时。

在很多应用中,ARM作为主设备控制复位和启动DSP。

在这种方案下(DSPBOOT=0),DSP保持失效(保持复位)在复位后,ARM负责释放DSP从复位中。

在将DSP从复位状态释放之前,ARM必须发送一个有效地DSPboot概念到编程的DSP或存储器(DSPmemory,EMIFAorDDR2),并且配置DSP启动地址在DSPBOOTADDR寄存器((inSYSTEMmodule)决定哪个DSP要执行。

DSPBOOT=1,DSP将自己启动。

该方案下,DSP将从复位中释放不用ARM参与。

DSP启动地址设置到EMIFA地址0x42200000h。

DSP将开始执行命令缓冲使能。

复位后的配置

复用管脚配置既在复位中也在复位后

SwitchCentralResource(SCR)Bus优先级作为主模式,它的优先值设置通过配置MSTPRI0,MSTPRI1,andMSTPRI2寄存器。

默认为MSTPRI0/1/2。

外设选择在设备复位之后

HPICTL寄存器

PWMCTL(TriggerSource)控制寄存器

EDMATCCFG寄存器

复用管脚的配置

管脚复用寄存器PINMUX0和PINMUX1负责控制所有的复用管脚功能设置。

在复位下设置。

复位以后可以通过软件编程PINMUX0和PINMUX1寄存器来改变管脚的功能。

以下外设有复用脚:

VPIF,TSIF0,TSIF1,CRGEN0,CRGEN1,EMIFA,PCI,HPI,ATA,PWM0,PWM1,UART0,UART1,UART2,AudioClockSelector,theUSBUSB_DRVVBUSpin,

andGPIO。

调试

上下拉电阻

适当的板子设计应该确保输入管脚到TMS320DM646xDMSoC设备能够保证有效地逻辑电平并且不浮动。

这个结果就需要通过上下拉电阻获得。

外部上下拉电阻用于以下几种情况:

●启动和配置管脚:

如果管脚同时做输出路径又有三态功能(不驱动),上下拉电阻推荐使用。

IPU/IPD符合理想的值。

●其他输入管脚:

IPU/IPD不匹配理想的值或状态。

用外部上下拉电阻是信号将信号拉向相反方向。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- dm6467 中文

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx