ddr2测试规范.docx

ddr2测试规范.docx

- 文档编号:6617745

- 上传时间:2023-01-08

- 格式:DOCX

- 页数:70

- 大小:3.01MB

ddr2测试规范.docx

《ddr2测试规范.docx》由会员分享,可在线阅读,更多相关《ddr2测试规范.docx(70页珍藏版)》请在冰豆网上搜索。

ddr2测试规范

DDR2SDRAM接口硬件测试规范

1范围

本标准规定了DDR2SDRAM接口的硬件测试方法和相关测试注意事项,并结合测试示例给以说明。

2术语和定义

SDRAMSynchronousDynamicRandomAccessMemory同步动态随机存取内存

DDR2DoubleDataRateSDRAM双倍速数据速率SDRAM

DDR2DDR-Ⅱ第二代DDR

SSTLStubSeriesTerminatedLogic短线串联终止逻辑电路

CPUCentralProcessUnit中央处理器

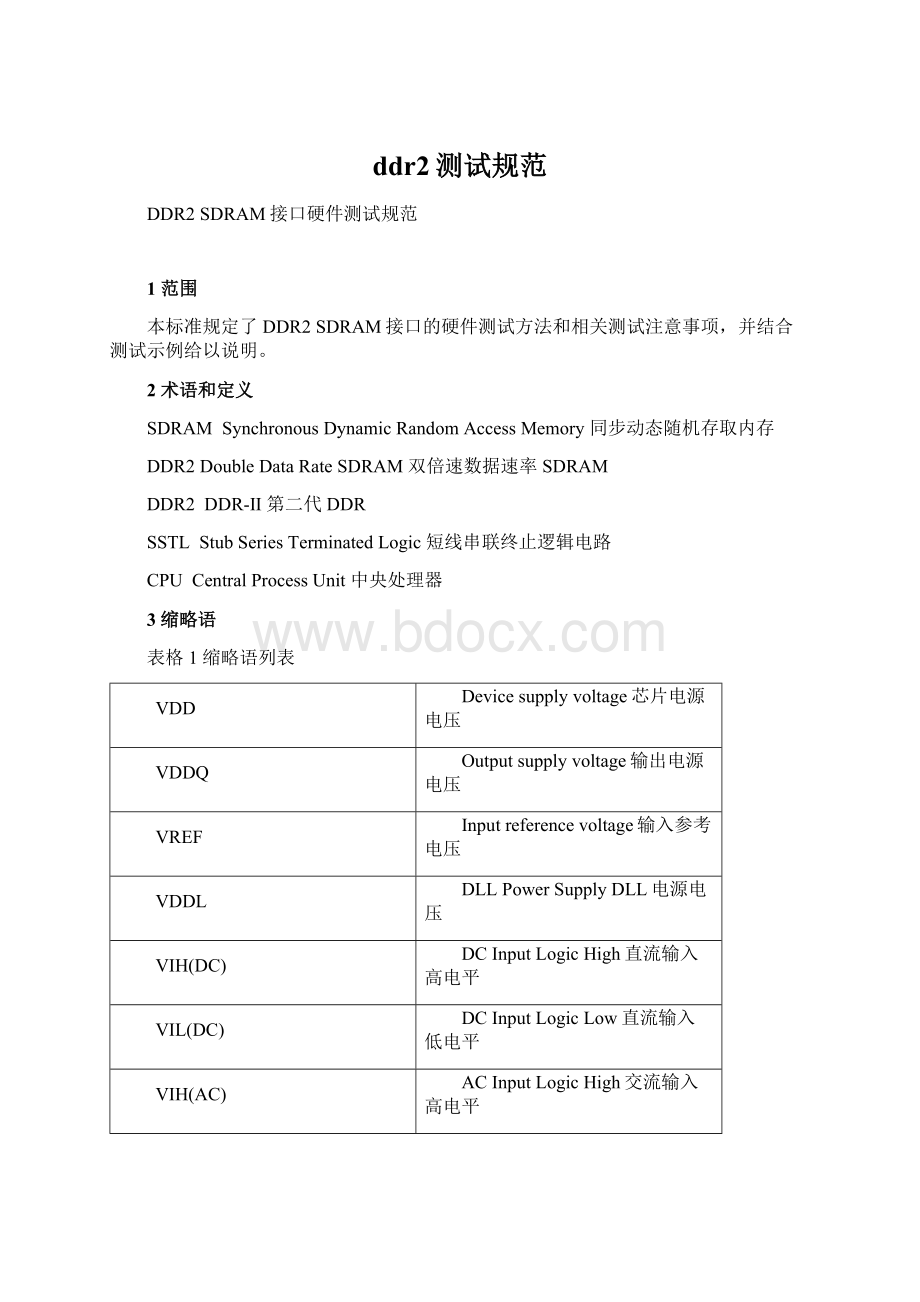

3缩略语

表格1缩略语列表

VDD

Devicesupplyvoltage芯片电源电压

VDDQ

Outputsupplyvoltage输出电源电压

VREF

Inputreferencevoltage输入参考电压

VDDL

DLLPowerSupplyDLL电源电压

VIH(DC)

DCInputLogicHigh直流输入高电平

VIL(DC)

DCInputLogicLow直流输入低电平

VIH(AC)

ACInputLogicHigh交流输入高电平

VIL(AC)

ACInputLogicLow交流输入低电平

VOH

HIGH-stateoutputvoltage,correspondingtologic1atoutput

高电平输出电压,输出端对应逻辑为1。

VOL

LOW-stateoutputvoltage,correspondingtologic0atoutput

低电平输出电压,输出端对应逻辑为0。

ODT

On-DieTermination内置匹配电阻

OCD

Off-ChipDriver离线驱动调整

AL

AdditiveLatency附加延迟

SSTL_18

StubSeriesTerminatedLinefor1.8Volts1.8V的SSTL电平

4测试仪器仪表清单

表格2测试仪器仪表清单

序号

设备名称

精度及级别

备注

1

高端实时示波器

双通道带宽≥4Ghz

采样速率:

≥40Ghz

如LeCroySDA6000,TEKCSA8000,Agilent80000B

2

数字频率计

测频分辨率:

11-12位/秒

测时分辨率:

≤200ps

如agilent53131A测频率

有10Mhz外部基准输入口

3

相位噪声测试仪

频偏分析范围:

0.01Hz~40MHz

测量精度:

频偏≤1MHz,±2dB;频偏>1MHz,±3dB

如PN9000

4

通用实时示波器

双通道带宽≥200Ghz

采样速率:

≥1Ghz

LecroyWaveSurfer64XS

5

数字万用表

直流电压量程:

200mv~10V

精度:

±(0.5%+3)

VICTOR88B数字万用表

5接口说明以及方法

5.1SDRAM接口信号说明

表格3DDR2SDRAM接口管脚说明如下

信号组

信号名称

信号说明

地址信号

A

地址信号输入

BA

Bank地址信号输入

时钟信号

CK_P/CK_N

时钟信号输入

数据信号

DQ

数据信号输入输出

DQS_P/DQS_N

数据锁存信号输入输出

DM

数据掩码信号输入

控制信号

RAS_N

行地址锁存信号输入

ODT

内置匹配电阻控制输入信号

CAS_N

列地址锁存信号输入

WE_N

写使能信号输入

CS_N

片选信号输入

CKE

时钟使能信号输入

电源

VDD

芯片供电管脚

VDDQ

DQ供电管脚

VREF

端接电源电压

VDDL

DLL电源电压

VREF

SSTL_18接口参考电源

5.2DDR2SDRAM接口功能指标

DDR2SDRAM全称为DoubleDataRate2SDRAM,中文名为“第二代双倍数据速率同步动态随机读取存储器”。

DDR2SDRAM属于SDRAM家族。

DDR2SDRAM是在DDRSDRAM基础上的升级,是目前最通用的SDRAM规格。

目前的DDR2SDRAM有几个标准速率:

●DDR2-400

●DDR2-533

●DDR2-667

●DDR2-800

●DDR2-1000

●DDR2-1066

●DDR2-1200

DDR2SDRAM在系统时钟的上升沿和下降沿进行数据操作。

DDR2接口原理框图如图1所示.

图表1DDR2SDRAM接口原理框图

下表为DDR2SDRAM的技术规格:

表格4DDR2SDRAM的技术规格表

参数

DDR2SDRAM

VDD

1.8V

VDDL

1.8V

VDDQ

1.8V

VREF

0.5*VDDQ

VREF

VREF

I/O接口

SSTL_18

数据传输率(Mbps)

400-1200

容量标准

256M~2G

CL值

3/4/5

预取设计(Bit)

4

逻辑Bank数量

4/8

突发长度

4/8

封装

FBGA

DDR2接口的DQS是源同步时钟,在接收端使用DQS来读出相应的数据DQ,上升沿和下降沿都有效。

对于DDR2,DQS是差分信号。

DDR2SDRAM虽然同是采用了在时钟的上升/下降延同时进行数据传输的基本方式,但DDR2内存却拥有两倍于上一代DDR内存预读取能力。

换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

与DDR相比,DDR2增加了几个特性:

ODT(OnDieTermination),DDR匹配放在单板上,DDR2把匹配直接设计到DRAM芯片内部,用来改善信号质量和节省空间。

OCD(OffChipDriver)技术是加强上下拉驱动的控制功能,通过减小DQS与DQS#的时滞(Skew)来增加信号的时序容限(TimingMargin)。

PostedCAS是提高总线利用率的一种方法。

AL(AdditiveLatency)技术是相对于外部CAS,内部CAS执行一定的延时。

DDR2SDRAM接口使用的是SSTL_18接口,该接口的输入信号电平有AC和DC之分。

其中AC电平的使用是为了保证,接收端在该电平处必须满足其时序参数的要求;或者说AC电平的主要目的是保证器件能够识别出逻辑翻转。

DC电平则主要是为了逻辑状态稳定的需要,就是说,如果接收端输入信号的电平大于该值,逻辑状态就会稳定在该状态,并隐含着信号过冲和振铃幅度的限制。

DDR2SDRAM接口的硬件测试分为:

电源完整性测试,信号完整性测试(不包括时钟),时钟测试和时序测试。

下边给出每个测试需要进行的测试项。

5.2.1电源完整性需要测试以下指标

1、电源精度测试:

需要测试电源VDD、VDDQ、VDDL、VREF和VREF的电压精度

2、电源纹波测试:

需要测试电源VDD、VDDQ、VDDL、VREF和VREF的电源纹波

3、上电波形测试:

需要测试电源VDD、VDDQ、VDDL、VREF和VREF的上电波形

4、上电时序测试:

需要测试VDD和VDDQ、VDDQ、VDDL、VREF和VREF之间的上电时序

5.2.2信号完整性需要测试以下指标

表格5信号完整性测试项目列表

测量参数

参数的含义

哪些信号需要测试

VSWING(MAX)

Inputsignalmaximumpeaktopeakswing

控制,地址、数据,时钟

SLEWr

Inputsignalminimumrisingslewrate

控制,地址、数据,时钟

SLEWf

Inputsignalminimumfallingslewrate

控制,地址、数据,时钟

Vih(ac)

MaximumACInputLogicHigh

控制,地址,数据、时钟

Vih(dc)

MinimumDCInputLogicHigh

控制,地址,数据、时钟

Vil(ac)

MinimumACInputLogicLow

控制,地址,数据、时钟

Vil(dc)

MaximumDCInputLogicLow

控制,地址,数据、时钟

Voh

OutputHighVoltage

控制,地址,数据、时钟

Vol

OutputLowVoltage

控制,地址,数据、时钟

Overshoot

Overshootamplitude

控制,地址,数据、时钟

Overshootarea

控制,地址,数据、时钟

Undershoot

Undershootamplitude

控制,地址,数据、时钟

Undershootarea

控制,地址,数据、时钟

Vmax

MaximumInputVoltage

控制,地址,数据、时钟

Vmin

MinimumInputVoltage

控制,地址,数据、时钟

tIPW

Control&Addressinputpulsewidth

控制、地址

tCKE

CKEminimumpulsewidth

(HIGHandLOWpulsewidth)

CKE

tDIPW

DQandDMinputpulsewidth

DQ和DM

tDQSH

DQSinputhighpulsewidth

DQS

tDQSL

DQSinputlowpulsewidth

DQS

5.2.3时序需要测试以下指标

表格6时序测试项目列表

测量参数

参数的含义

地址信号时序测试

tIS(base)

ADDR2essInputSetupTime

tIH(base)

ADDR2essInputHoldTime

控制信号时序测试

tIS(base)

ControlInputSetupTime

tIH(base)

ControlInputSetupTime

数据信号时序测试

tDS(base)

DQ/DMinputsetuptime(differentialstrobe)

tDH(base)

DQ/DMinputholdtime(differentialstrobe)

tDS1(base)

DQandDMinputsetuptime(single-endedstrobe)

tDH1(base)

DQandDMinputholdtime(single-endedstrobe)

tDQSCK

DQSoutputaccesstimefromCK,/CK

tDQSQ

DQS-DQskewforDQSandassociatedDQsignals,ForBGAPackage

tQH

DQ/DQSoutputholdtimefromDQS

tDQSS

DQSlatchingtransitiontoassociatedclockedge

tDSS

DQSfallingedgetoCKsetuptime

tDSH

DQSfallingedgeholdtimefromCK

tHZDQ

DQouthigh-impedancetimefromCK,/CK

tLZDQ

DQlow-impedancetimefromCK,/CK

tLZDQS

DQSlow-impedancetimefromCK,/CK

tHZDQS

DQShigh-impedancetimefromCK,/CK

tRPRE

ReadPreamble

tRPST

ReadPostamble

tWPRE

WritePreamble

tWPST

WritePostamble

5.2.4时钟信号需要测试以下指标

表格7时钟信号测试项目列表

测量参数

参数的含义

时钟信号波形测试

Vid

ACdifferentialinputvoltage

Vix

ACdifferentialinputcrosspointvoltage

tCK

PeriodRisingEdgeMeasurements

PeriodFallingEdgeMeasurements

tCH

clockHIGHpulsewidth

tCL

clockLOWpulsewidth

tCK(avg)

AverageclockPeriodRisingEdgeMeasurements

AverageclockPeriodFallingEdgeMeasurements

tCH(avg)

AverageclockHIGHpulsewidth

tCL(avg)

AverageclockLOWpulsewidth

Vmax

MaximumInputVoltage

Vmin

MinimumInputVoltage

VSWING(MAX)

InputSignalMaximumPeakToPeakSwing

SLEWr

Inputsignalminimumrisingslewrate

SLEWf

Inputsignalminimumfallingslewrate

时钟信号Jitter测试

Tj(10e-12)

TotalJitter(10e-12)

Dj

DeterministicJitter

Rj

RandomJitter

tJIT(per)

ClockPeriodJitterRisingEdgeMeasurements

ClockPeriodJitterfallingEdgeMeasurements

tJIT(cc)

CycletoCyclePeriodJitterRisingEdgeMeasurements

CycletoCyclePeriodJitterfallingEdgeMeasurements

tJIT(duty)

TheHalfPeriodJitterAverageHighPulseMeasurement

TheHalfPeriodJitterAverageLowPulseMeasurement

tERR(n-per)

CumulativeError(acrossncycles)RisingEdgeMeasurements

CumulativeError(acrossncycles)FallingEdgeMeasurements

5.3DDR2SDRAM参数测试说明

5.3.1DDR2SDRAM读写区分的方法

1、通过数据延迟来区分读写

使用示波器的两个通道CH1和CH3,CH1连接到DDR2SDRAM端,CH3连接到存储器控制端,使用CH1为触发源,当捕获到的波形显示,CH3落后于CH1时,就是读周期。

2、通过DQ和DQS的关系来区分读写

在DDR2SDRAM中,DQS的是源同步时钟。

DQS和DQ都是三态信号,在PCB走线上双向传输,读操作时,DQS信号的边沿在时序上与DQ的信号边沿处对齐,如图表2所示;而写操作时,DQS信号的边沿在时序上与DQ信号的中心处对齐。

如图表3所示:

图表2DDR2SDRAM读操作DQS与DQ时序图

图表3DDR2SDRAM写操作DQS与DQ时序图

3、通过驱动电平来区分

一般在DDR2SDRAM的应用中,可以以数据信号的驱动能力来区分。

接收的波形幅度要小于发送的波形幅度。

但是这个并不是总是这样的。

使用的时候最好用第一种或者第二种方法,来验证一下。

图表4为某单板在5665端测试的DQS与DQ数据信号,幅值比较低的为读信号,幅值比较高的为写信号。

但是并不是总是这样的,比如其他单板上的SDRAM的信号,不管在那端测试,QE/TME的驱动的写数据信号的幅度总是大于读数据信号的幅度。

图表4某单板在5665端测试的DQS和DQ信号

5.3.2单端信号AC输入参数测量

5.3.2.1VSWING(MAX)的测试方法

输入信号峰峰值中的最大值。

使用示波器自带的自动测试项Vp-p,进行测试,测试结果中的max作为测试结果。

见下图为该参数的测试示意图和测试示例。

如下信号需要测试该参数:

地址信号、控制信号、数据信号,时钟信号。

图表5VSWING(MAX)的测试示意图

图表6VSWING(MAX)的测试示例

5.3.2.2SlewR参数测量方法

输入信号上升沿最小斜率。

这个测试的目的是为了验证,被测信号的上升沿Slewrate是否大于等于DDR2SDRAM规范中规定的最小值。

见下图为该参数的测试示意图和测试示例。

如下信号需要测试该参数:

地址信号、控制信号、数据信号(DQ,DM和单端DQS模式的DQS信号,按照这个方法测试,如果是差分DQS模式,DQS信号需要按照差分SlewR方法测试)。

图表7单端信号的SlewR测量示意图

图表8单端信号的SlewR测试示例

5.3.2.3SlewF参数的测量方法

输入信号下降沿最小斜率。

这个测试的目的是为了验证,被测信号的下降沿的Slewrate是否大于等于DDR2SDRAM规范中规定的最小值。

见下图为该参数的测试示意图和测试示例。

如下信号需要测试该参数:

地址信号、控制信号、数据信号(DQ,DM和单端DQS模式的DQS信号,按照这个方法测试,如果是差分DQS模式,DQS信号需要按照差分SlewF方法测试)。

图表9单端信号的SlewF测量示意图

图表10单端信号的SlewF测试示例

5.3.2.4VIH的测试方法

DDR2SDRAM接口使用的是SSTL_2电平。

输入信号的电平分为AC和DC。

需要保证任何输入的单端信号必须大于VIH(AC)值一定时间,可能由于振铃信号,信号会回落,但是不能回落到VIH(DC)电平之下。

可以使用余晖的方式,累计显示是否有不符合要求的信号。

如下信号需要测试该参数:

地址信号、控制信号、数据信号(DQ,DM和单端DQS模式的DQS信号)。

图表11SSTL_2输入电压示意图

5.3.2.5VIL的测试方法

DDR2SDRAM接口使用的是SSTL_2电平。

输入信号的电平分为AC和DC。

需要保证任何输入的单端信号必须小于VIL(AC)值一定时间,可能由于振铃信号,信号会回落,但是不能回落到VIL(DC)电平之上。

可以使用余晖的方式,累计显示是否有不符合要求的信号。

如下信号需要测试该参数:

地址信号、控制信号、数据信号(DQ,DM和单端DQS模式的DQS信号)。

图表12SSTL_2输入电压示意图

5.3.2.6tDIPW的测试方法

输入DQ/DM信号的脉冲宽度。

分为高电平宽度和低电平宽度。

测试方法:

从DQ/DM信号边沿的Vref电平到下个边沿的Vref电平的时间差。

需要在写周期测试。

5.3.2.7tIPW的测试方法

输入控制信号和地址信号的脉冲宽度。

分为高电平宽度和低电平宽度。

测试方法:

从控制信号和地址信号边沿的Vref电平到下个边沿的Vref电平的时间差。

需要在写周期测试。

5.3.3输入信号过冲欠冲测试

5.3.3.1信号过冲测试方法

信号的过冲测试分为过冲幅值测试和过冲面积测试,测试的目的是为了验证是否与DDR2SDRAM规范相一致。

过冲的最大值等于波形幅度的最大值与VDD的差;过冲面积的计算是通过计算过冲的时间与过冲幅度的积来计算的。

见下图为该参数的测试示意图和测试示例。

如下信号需要测试该参数:

地址信号、控制信号、数据信号

图表13过冲测试示意图

图表14过冲测试示例

5.3.3.2信号欠冲测试方法

信号的欠冲测试分为欠冲幅值测试和欠冲面积测试,测试的目的是为了验证是否与DDR2SDRAM规范相一致。

欠冲幅度等于波形幅度的最小值与VDD的差;欠冲面积的计算是通过计算欠冲的时间与欠冲幅度的积来计算的。

见下图为该参数的测试示意图和测试示例。

如下信号需要测试该参数:

地址信号、控制信号、数据信号

图表15欠冲测试示意图

图表16过冲测试示例

5.3.4差分信号AC参数测量

5.3.4.1SlewR测试方法

输入信号上升沿最小斜率。

这个测试的目的是为了验证,被测信号的上升沿Slewrate是否大于等于DDR2SDRAM规范中规定的最小值。

测试方法:

从差分输入信号上升沿的-250mv到500mv的斜率。

注:

测试差分信号时,注意差分探头和差分信号的极性。

测试步骤:

1、使用差分探头连接被测信号,差分探头的正负,分别连接差分信号的主信号和辅助信号。

2、假设被测信号在CH1,在示波器内设置CH1的top值为500mv,base值为-250mv。

3、使用示波器内的自动测试参数项slewrate测试,使用slewrate的最小值作为测试结果。

见图表17为差分信号的SlewR的测试示例。

如下信号需要测试该参数:

差分DQS信号、差分时钟信号。

图表17差分信号SlewR的测试示例

5.3.4.2SlewF测试方法

输入信号下降沿最小斜率。

这个测试的目的是为了验证,被测信号的下降沿Slewrate是否大于等于DDR2SDRAM规范中规定的最小值。

测试方法:

从差分输入信号下降沿的250mv到-500mv的斜率。

注:

测试差分信号时,注意差分探头和差分信号的极性。

测试步骤:

1、使用差分探头连接被测信号,差分探头的正负,分别连接差分信号的主信号和辅助信号。

2、假设被测信号在CH1,在示波器内设置CH1的top值为250mv,base值为-500mv。

3、使用示波器内的自动测试参数项slewrate测试,使用slewrate的最小值作为测试结果。

见图表18为差分信号的SlewF的测试示例。

如下信号需要测试该参数:

差分DQS信号、差分时钟信号。

图表18差分信号SlewF的测试示例

5.3.4.3VID测试方法

差分输入电压测试。

测试目的是为了验证是否与DDR2SDRAM规范一致。

使用两个通道,一个通道连接差分的主信号,一个通道连接差分的辅助信号。

用主信号的高电平值(使用直方图统计或者使用示波器的自动测量参数)减去辅助信号的低电平值(使用直方图统计或者使用示波器的自动测量参数)。

见下图为该参数的测试示意图和测试示例。

如下信号需要测试该参数:

时钟信号、差分DQS信号。

图表19VID测试示意图

图表20VID测试示例

5.3.4.4VIX测试方法

差分输入交叉点电压测试。

测试目的是为了验证是否与DDR2SDRAM规范一致。

使用两个通道,一个通道连接差分的主信号,一个通道连接差分的辅助信号。

使用示

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- ddr2 测试 规范

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx