HBEEMPOSIIISV210实验箱的构成.docx

HBEEMPOSIIISV210实验箱的构成.docx

- 文档编号:6775299

- 上传时间:2023-01-10

- 格式:DOCX

- 页数:13

- 大小:440.68KB

HBEEMPOSIIISV210实验箱的构成.docx

《HBEEMPOSIIISV210实验箱的构成.docx》由会员分享,可在线阅读,更多相关《HBEEMPOSIIISV210实验箱的构成.docx(13页珍藏版)》请在冰豆网上搜索。

HBEEMPOSIIISV210实验箱的构成

1.实验目的:

了解三星S5PV210处理器的结构及特点;掌握HBE-EMPOSIII-SV210的系统构造及特征。

2.实验内容:

对照实验箱,阅读并理解以下资料。

阅读材料:

3.HBE-EMPOSIII-SV210系统概要

3.1S5PV210处理器构造及特征

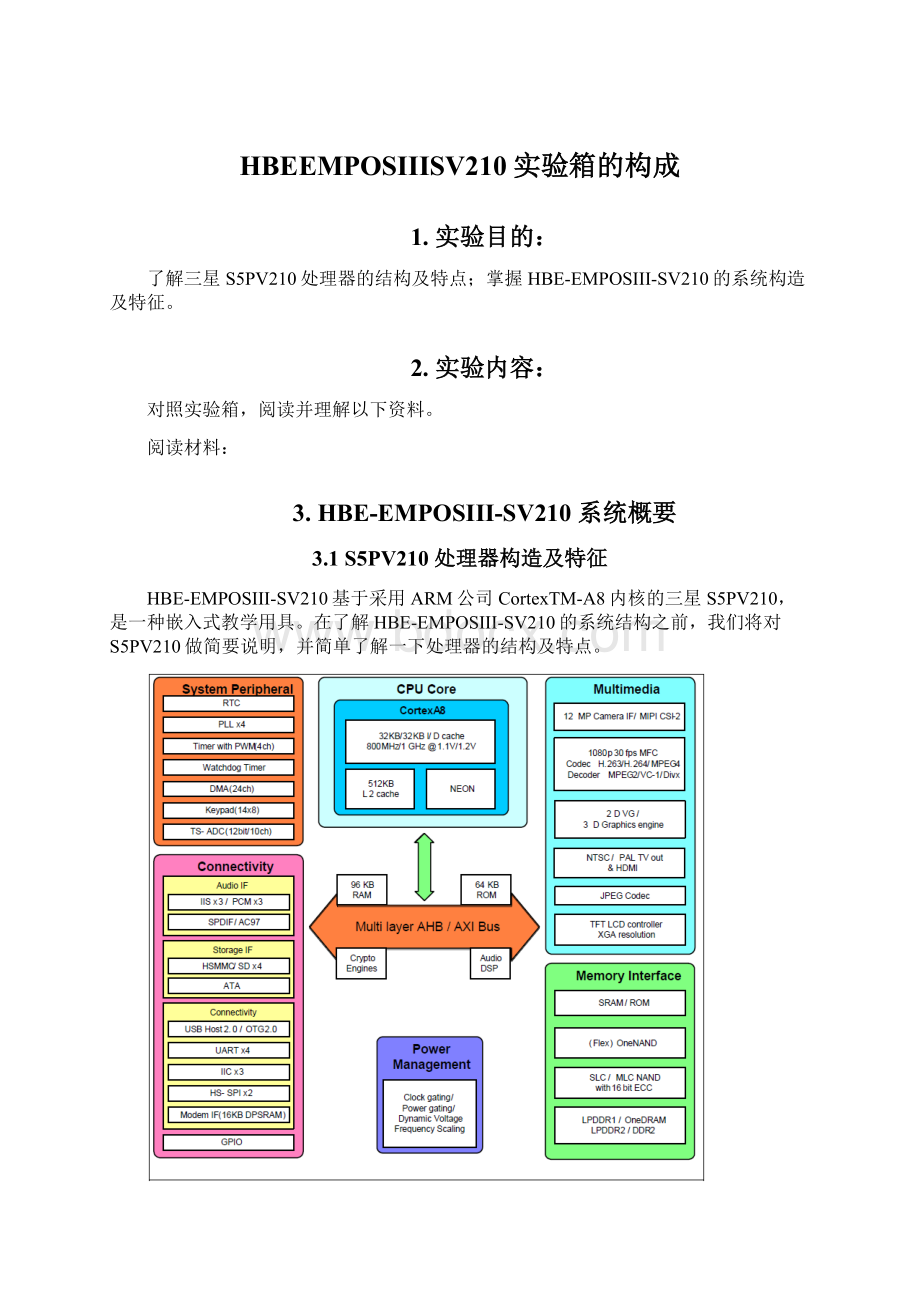

HBE-EMPOSIII-SV210基于采用ARM公司CortexTM-A8内核的三星S5PV210,是一种嵌入式教学用具。

在了解HBE-EMPOSIII-SV210的系统结构之前,我们将对S5PV210做简要说明,并简单了解一下处理器的结构及特点。

[图11]S5PV210的框图

S5PV210的框图如[图1-1]所示。

从图中可知,S5PV210由ARM内核、系统外围设备(SystemPeripheral)、多媒体(Multimedia)、存储器接口(MemoryInterface)、电源管理(PowerManagement)、连通性(Connectivity)等功能块构成。

S5PV210基于三星开发的ARMCortexTM-A8,是一种实现ARM架构V7-A的32位RISC微处理器。

它为要求低耗电、高性能的移动及普通应用提供解决方案。

此外,为提供3G和3.5G通信服务相关的优化硬件性能,S5PV210还具有64位内部总线结构。

S5PV210针对动作视频处理(MotionVideoProcessing)、显示控制及缩放(DisplayControlAndScaling)等,内置了多个功能强大的硬件加速器。

其中,MFC(MultiFormatCodec,多格式编码译码器)提供了有关MPEG-1/2/4、H.263/H.264的编码和解码,还提供了有关VC1、Divx的解码。

此外,这种硬件加速器还支持实时电视会议和模拟电视输出、HDMI接口。

.

S5PV210的特征如下。

©ARMCortexTM-A8basedCPUSubsystemwithNEON

▪32/32KBI/DCache,512KBL2Cache

▪Operatingfrequencyupto800Mhzat1.1V,1GHzat1.2V

©64-bitMulti-layerbusarchitecture

▪MSYSdomainforARMCortexTM-A8,3Dengine,MultiFormatCodecandInterruptController

©Operatingfrequencyupto200Mhzat1.1V

▪DSYSdomainmainlyforDisplayIPs(suchasLCDcontroller,Camerainterface,andTVout),andMDMA

©Operatingfrequencyupto166Mhzat1.1V

▪PSYSdomainmainlyforothersystemcomponentsuchassystemperipherals,externalmemoryinterface,periDMAs,connectivityIPs,andAudiointerfaces.

©Operatingfrequencyupto133Mhzat1.1V

▪Audiodomainforlowpoweraudioplay

©Advancedpowermanagementformobileapplications

©64KBROMforsecurebootingand128KBRAMforsecurityfunction

©8-bitITU601/656CameraInterfacesupportshorizontalsizeupto4224pixelsforscaledand8192pixelsforun-scaledresolution

©MultiFormatCodecprovidesencodinganddecodingofMPEG-4/H.263/H.264upto1080p@30fpsandcodingofMPEG-2/VC1/Divxvideoupto1080p@30fps.

©JPEGcodecsupportupto80Mpixels/s

©3DGraphicsAccelerationwithprogrammableshaderupto20Mtriangles/sand1000Mpixels/s

©2DGraphicsAccelerationupto160MPixels/s

©1/2/4/8bppPalletizedor8/16/24bppNon-PalletizedColor-TFTrecommendeduptoXGAresolution.

©TV-outandHDMIinterfacesupportforNTSCandPALmodewithimageenhancer

©MIPI-DSIandMIPI-CSIinterface

©OneAC-97audiocodecinterfaceand3-channelPCMserialaudiointerface

©3-channel24-bitI2Sinterface

©1-channelTXonlyS/PDIFinterfacesupportfordigitalaudio

©3-channelI2Cinterface

©2-channelSPIinterface

©4-channelUARTincluding3MbpsportforBluetooth2.0

©On-chipUSB2.0OTGsupportinghighspeed(480Mbps,on-chiptransceiver)

©On-chipUSB2.0Host

©AsynchronousModemInterface

©4SD/SDIO/HS-MMCinterface.

©ATA/ATAPI-6standardinterface

©24-channelDMAcontroller(8channelsforMemory-to-memoryDMA,16channelsforPeripheralDMA)

©14x8keymatrixinterface

©10-channel12-bitmultiplexedADC

©ConfigurableGPIOs

©Realtimeclock,PLL,timerwithPWMandwatchdogtimer.

©Systemtimersupportforaccurateticktimeinpowerdownmode(exceptsleepmode)

©MemorySubsystem

▪AsynchronousSRAM/ROM/NORInterfacewithx8orx16databus.

▪NANDInterfacewithx8databus

▪Muxed/DemuxedOneNANDInterfacewithx16databus.

▪LPDDR1Interfacewithx16orx32databus(266~400Mbps/pinDDR)

▪DDR2interfacewithx16orx32databus(400Mbps/pinDDR)

▪LPDDR2interface(400Mbps/pinDDR)

3.2HBE-EMPOSIII-SV210的系统构造及特征

在本节中,记述了目标板—HBE-EMPOSIII-SV210的系统构造及特征。

3.2.1系统构造

HBE-EMPOSIII-SV210以S5PV210处理器为中心,主要由CPU模块(由NANDFlashmemory、DDR2SDRAM和缓存等构成)、通过NORFlashMemory、LCD、UART、USB、Audio、Ethernet、Camera、SDCardslot等外围设备和FPGA控制的DipSwitch、DotMatrix、LEDs、CharacterLCD、OLED、7-Segment、蜂鸣器、Keypad、CMOSCamera等多种应用设备以及基板(提供通过Microcontroller控制的各种传感器)构成。

下[图1-2]显示了HBE-EMPOSIII-SV210的整体框图。

[图12]HBE-EMPOSIII-SV210整体框图

3.2.2系统特征

HBE-EMPOSIII-SV210主要由CPU模块和基板构成,将提供以下多种功能。

.

❑HBE-EMPOSIII-SV210CPUModule

▪三星S5PV210(ARMCortexTM-A8Core)

▪512MByteDDR2SDRAM:

128MByte*4ea

▪256MByteNANDFlashMemory:

256MByte*1ea

❑HBE-EMPOSIII-SV210BaseBoard(CPUConnected)

▪10/100Base-TEthernetController

▪7”TFTLCDwithTouchScreen

▪3.1MPixelCMOSCamera

▪IISAudioCodec:

Speaker,MIC&Line-In

▪USB2.0Host3PortandUSB2.0OTG1Port

▪RS232LevelUART3Port

▪TTLLevelUART4Port

▪Bluetooth

▪SD/MMCCardConnector2Port

▪CompositeVideoOut1Port

▪HDMI1Port

▪SPDIF1Port

▪5*3Keypad

▪1eaJogSwitch

▪1eaPowerOn/OffSwitch

▪2eaBootModeSwitch

❑HBE-EMPOSIII-SV210BaseBoard(FPGAConnected)

▪CharacterLCD(16*2)

▪1,3MPixelCMOSCamera

▪6Digit7-Segment

▪512KbyteSRAM*2ea

▪18,752LogicElementsFPGAEP2C20

▪7*5DotMatrix2ea

▪4*4Keypad

▪8pointDIPSwitch2ea

▪OLED

▪LED8ea

▪Buzzer

▪TactSwitch4ea

▪LightSensor

▪Temperature/HumiditySensor

3.3HBE-EMPOSIII-SV210产品构成

下<表1-1>显示了一套HBE-EMPOSIII-SV210产品中所包含的所有组件。

.

<表11>HBE-EMPOSIII-SV210产品构成

项目

Feature

HBE-EMPOSIII-SV210

ByteBlaster

USB线

(MinitoAType)

LAN线

(Straight)

LAN线

(Crossover)

并行数据线

Serial线

电源线

教材及产品CD

实验设备:

PC机和HBE-EMPOSIII-SV210实验箱各一台;

实验步骤:

1、对照阅读材料,在实验箱上找到CPU模块、FPGA模块、单片机模块;

2、记录个模块主要的连接部件,主要的芯片型号;

3、

实验注意事项:

本次实验无需打开实验箱电源。

实验思考题:

1、将下面材料翻译成中文,要求表达正确,专业术语表达恰当。

(1)S5PV210的特征如下。

©ARMCortexTM-A8basedCPUSubsystemwithNEON

▪32/32KBI/DCache,512KBL2Cache

▪Operatingfrequencyupto800Mhzat1.1V,1GHzat1.2V

©64-bitMulti-layerbusarchitecture

▪MSYSdomainforARMCortexTM-A8,3Dengine,MultiFormatCodecandInterruptController

©Operatingfrequencyupto200Mhzat1.1V

▪DSYSdomainmainlyforDisplayIPs(suchasLCDcontroller,Camerainterface,andTVout),andMDMA

©Operatingfrequencyupto166Mhzat1.1V

▪PSYSdomainmainlyforothersystemcomponentsuchassystemperipherals,externalmemoryinterface,periDMAs,connectivityIPs,andAudiointerfaces.

©Operatingfrequencyupto133Mhzat1.1V

▪Audiodomainforlowpoweraudioplay

©Advancedpowermanagementformobileapplications

©64KBROMforsecurebootingand128KBRAMforsecurityfunction

©8-bitITU601/656CameraInterfacesupportshorizontalsizeupto4224pixelsforscaledand8192pixelsforun-scaledresolution

©MultiFormatCodecprovidesencodinganddecodingofMPEG-4/H.263/H.264upto1080p@30fpsandcodingofMPEG-2/VC1/Divxvideoupto1080p@30fps.

©JPEGcodecsupportupto80Mpixels/s

©3DGraphicsAccelerationwithprogrammableshaderupto20Mtriangles/sand1000Mpixels/s

©2DGraphicsAccelerationupto160MPixels/s

©1/2/4/8bppPalletizedor8/16/24bppNon-PalletizedColor-TFTrecommendeduptoXGAresolution.

©TV-outandHDMIinterfacesupportforNTSCandPALmodewithimageenhancer

©MIPI-DSIandMIPI-CSIinterface

©OneAC-97audiocodecinterfaceand3-channelPCMserialaudiointerface

©3-channel24-bitI2Sinterface

©1-channelTXonlyS/PDIFinterfacesupportfordigitalaudio

©3-channelI2Cinterface

©2-channelSPIinterface

©4-channelUARTincluding3MbpsportforBluetooth2.0

©On-chipUSB2.0OTGsupportinghighspeed(480Mbps,on-chiptransceiver)

©On-chipUSB2.0Host

©AsynchronousModemInterface

©4SD/SDIO/HS-MMCinterface.

©ATA/ATAPI-6standardinterface

©24-channelDMAcontroller(8channelsforMemory-to-memoryDMA,16channelsforPeripheralDMA)

©14x8keymatrixinterface

©10-channel12-bitmultiplexedADC

©ConfigurableGPIOs

©Realtimeclock,PLL,timerwithPWMandwatchdogtimer.

©Systemtimersupportforaccurateticktimeinpowerdownmode(exceptsleepmode)

©MemorySubsystem

▪AsynchronousSRAM/ROM/NORInterfacewithx8orx16databus.

▪NANDInterfacewithx8databus

▪Muxed/DemuxedOneNANDInterfacewithx16databus.

▪LPDDR1Interfacewithx16orx32databus(266~400Mbps/pinDDR)

▪DDR2interfacewithx16orx32databus(400Mbps/pinDDR)

▪LPDDR2interface(400Mbps/pinDDR)

(2)系统特征

❑HBE-EMPOSIII-SV210CPUModule

▪三星S5PV210(ARMCortexTM-A8Core)

▪512MByteDDR2SDRAM:

128MByte*4ea

▪256MByteNANDFlashMemory:

256MByte*1ea

❑HBE-EMPOSIII-SV210BaseBoard(CPUConnected)

▪10/100Base-TEthernetController

▪7”TFTLCDwithTouchScreen

▪3.1MPixelCMOSCamera

▪IISAudioCodec:

Speaker,MIC&Line-In

▪USB2.0Host3PortandUSB2.0OTG1Port

▪RS232LevelUART3Port

▪TTLLevelUART4Port

▪Bluetooth

▪SD/MMCCardConnector2Port

▪CompositeVideoOut1Port

▪HDMI1Port

▪SPDIF1Port

▪5*3Keypad

▪1eaJogSwitch

▪1eaPowerOn/OffSwitch

▪2eaBootModeSwitch

❑HBE-EMPOSIII-SV210BaseBoard(FPGAConnected)

▪CharacterLCD(16*2)

▪1,3MPixelCMOSCamera

▪6Digit7-Segment

▪512KbyteSRAM*2ea

▪18,752LogicElementsFPGAEP2C20

▪7*5DotMatrix2ea

▪4*4Keypad

▪8pointDIPSwitch2ea

▪OLED

▪LED8ea

▪Buzzer

▪TactSwitch4ea

▪LightSensor

▪Temperature/HumiditySensor

2、写出实验中记录的各模块主要的连接部件及主要的芯片型号,并简单描述各芯片的功能。

CPU模块–SAMSUNGS5PV210AHARMCortexTM-A8

EM-S5PV210是一款功能极其强大的高端ARMCortex-A8开发平台,其功能全面、接口丰富,完美展现了SamsuungS5PV210芯片的强大,主要面向企业用户进行产品开发过程中,对S5PV210芯片的性能评估、设计参考使用。

其丰富的外设接口及强大的性能,也成为高校、科研机构等单位的最佳科研设备。

EM-S5PV210开发板具有更高的主频和更丰富外设,能适用于对性能和处理能力有更高要求的嵌入式系统应用场合。

FPGA模块–ALTERAcyclone11EPEC20F484C8NKCBD9Y0937A

CycloneIIFPGA据称比上一代成本低30%,逻辑容量多三倍。

CycloneII器件采用了TSMC验证的90nm低K介电质工艺制造的成本优化架构,容量从4,608至68,416个逻辑单元(LE),是第一代Cyclone器件的三倍;同时,CycloneII器件具有达150个嵌入18×18乘法器,适合于实现低成本数字信号处理(DSP)应用,这些乘法器能运行至250MHz,消除了由复杂算法计算所导致的性能瓶颈,能用CycloneII器件作为FPGA协处理器;此外CycloneII器件支持最近推出的NiosII系列嵌入式处理器,在CycloneII器件中实现NiosII嵌入式处理器,能够在仅为0.35美元的逻辑上实现超过100DMIPS的性能。

单片机模块–EMPOSIII-SC1XXBASEver2.1

提供具体支持

第二题

翻译

的ARMCortexTM-A8与霓虹灯的CPU子系统

32/32KBⅠ/D缓存,512KB二级缓存

1GHz的工作频率高达800兆赫,在1.1V到1.2V

64位多层总线架构

MSYS的域名为ARMCortexTM-A8,3D引擎,多格式编解码器,中断控制器

工作频率高达200MHz在1.1V

DSYS主要用于显示IP地址域(如

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- HBEEMPOSIIISV210 实验 构成

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx