微机原理与接口技术习题 答案修订版.docx

微机原理与接口技术习题 答案修订版.docx

- 文档编号:8852796

- 上传时间:2023-02-02

- 格式:DOCX

- 页数:24

- 大小:176.89KB

微机原理与接口技术习题 答案修订版.docx

《微机原理与接口技术习题 答案修订版.docx》由会员分享,可在线阅读,更多相关《微机原理与接口技术习题 答案修订版.docx(24页珍藏版)》请在冰豆网上搜索。

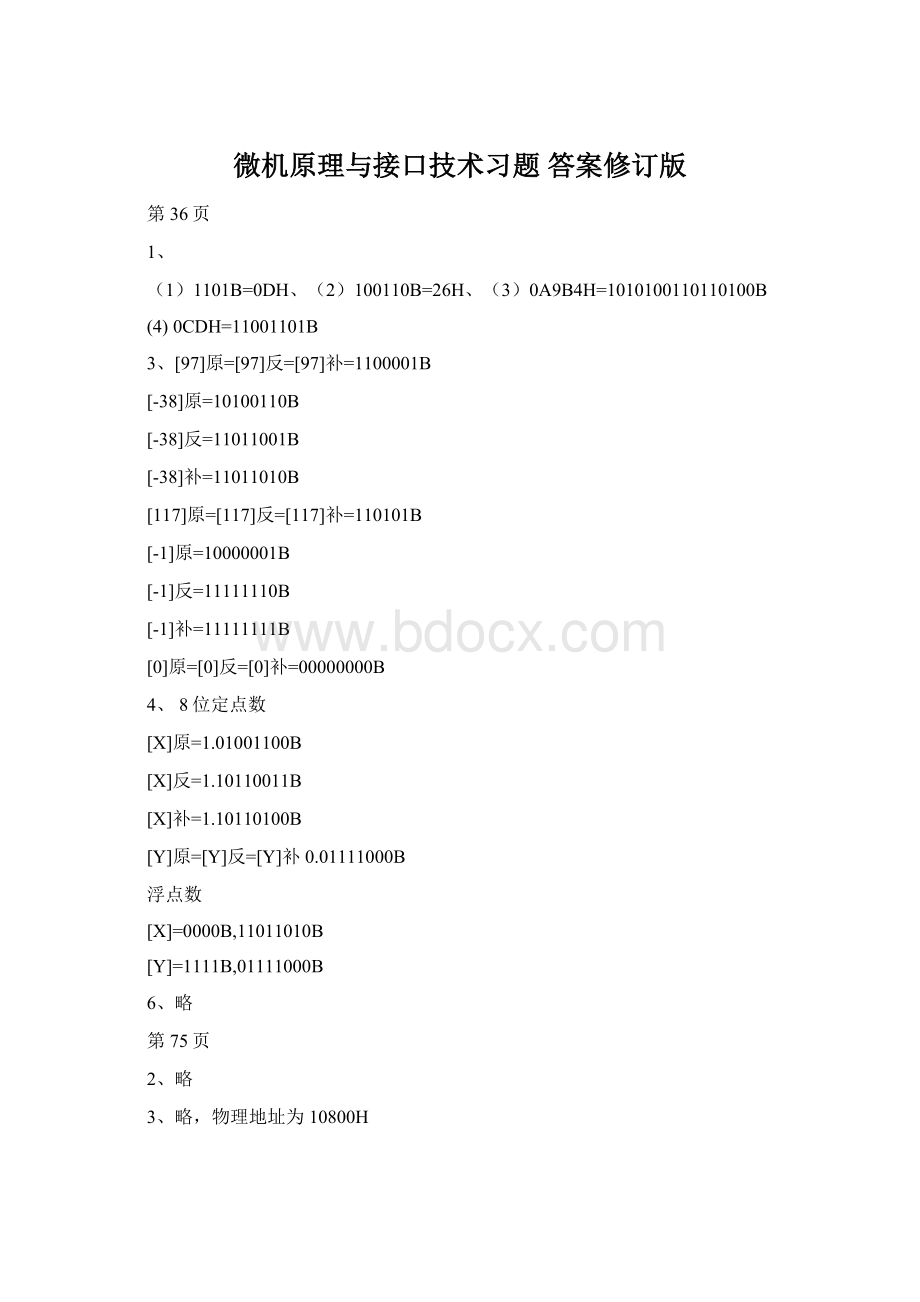

微机原理与接口技术习题答案修订版

第36页

1、

(1)1101B=0DH、

(2)100110B=26H、(3)0A9B4H=1010100110110100B

(4)0CDH=11001101B

3、[97]原=[97]反=[97]补=1100001B

[-38]原=10100110B

[-38]反=11011001B

[-38]补=11011010B

[117]原=[117]反=[117]补=110101B

[-1]原=10000001B

[-1]反=11111110B

[-1]补=11111111B

[0]原=[0]反=[0]补=00000000B

4、8位定点数

[X]原=1.01001100B

[X]反=1.10110011B

[X]补=1.10110100B

[Y]原=[Y]反=[Y]补0.01111000B

浮点数

[X]=0000B,11011010B

[Y]=1111B,01111000B

6、略

第75页

2、略

3、略,物理地址为10800H

4、由于8086系统的地址的低16位与数据引脚公用,地址信号与数据信号是分时复用这些引脚的。

这样先送出的地址信号可能被后送出的数据信号所代替,因此要有一个地址锁存器来保存先送出来的地址信息。

锁存器主要用来锁存地址的低16位。

5、AH内容送到9100H时,由于执行的是写操作,并且是数据的高8位数据,所以

、

/S7为低电平。

数据由9100H到CPU的AL时,由于执行的是读写操作,并且是数据的低8位数据,所以

、DT/

6、分时复用是由于CPU引脚数量有限,使得一些引脚起多个作用,在某一时刻传送地址,在另一时刻传送数据,这样的工作方式就称为分时复用的地址/数据总线。

8086CPU分时复用的引脚有:

①地址/数据复用的AD0~AD15

②地址/状态复用引脚A19/S6~A16/S3

③高8位数据允许/状态复用信号引脚

/S7

分时复用只要解决CPU制造工艺,因为管脚不能太多,引脚过多会使相邻两个引脚间距过小,不利于PCB板的焊接

11、略

第100页

1、

(1)源操作数为立即寻址,源操作数没有物理地址

(2)源操作数为直接寻址方式,源操作数物理地址为:

10100H

(3)源操作数为直接寻址方式,源操作数物理地址为:

10050H

(4)源操作数为变址寻址方式,源操作数物理地址为:

100A0H

(5)源操作数为基址加变址寻址方式,源操作数物理地址为:

10150H

(6)源操作数为相对基址寻址方式,源操作数物理地址为:

150B0H

(7)源操作数为寄存器寻址方式,源操作数没有物理地址

(8)源操作数为立即寻址方式,源操作数物理地址为:

CS*10H+IP

(9)源操作数为变址寻址方式,源操作数物理地址为:

200A0H

(10)源操作数为相对基址加变址寻址方式,源操作数物理地址为:

101A2H

2、

(1)LEABX,,[BLOCK+4]

MOVDX,[BX]

(2)LEABX,,BLOCK

MOVDX,4[BX]

(3)LEABX,[BLOCK]

MOVSI,4

MOVDX,[BX+SI]

3、

4、

(1)、(AX)=1800H

(2)、(AX)=100H

(3)(BX)=(21200H)=4CAH(4)、(DX)=(21200H)=4CAH

(5)、(202102H)=7856H(6)、(AX)=(21202H)=65B7H

5、

执行MOVAX,TABLE指令后(AX)=1234H

执行leaAX,TABLE指令后(AX)=0048H

6、

(1)MOVAX,Z

ADDAX,X

ADDAX,W

MOVZ,AX

(2)MOVAX,X

ADDAX,6

MOVBX,R

SUBBX,9

MOVCX,W

SUBCX,AX

SUBCX,BX

MOVZ,CX

7、

MOVBX,OFFSETTABLE;或LEABX,TABLE

MOVAL,CL

XLAT

8、

(1)MOVAX,W

MULX

MOVBX,R

ADDBX,6

DIVBX

MOVZ,AX

(2)MOVW,AX

SUBAX,X

MOVBL,5

DIVBL

CBW;这里商在AL中,余数在AH中,为了使商乘以Y

MULY

SALAX,1

RCLDX,1

MOVZ,AX

MOVZ+2,DX

9、

(1)(DX)=4D2BH

(2)(DX)=9A6CH

(3)(DX)=35B6h(4)(DX)=1356H

(5)(DX)=0D356H(6)=0D5B4H

(7)(DX)=9ADBH(8)(DX)=0D5B6H

10、

(1)CF=1、SF=0、OF=1、ZF=0

(2)CF=0、SF=1、OF=0、ZF=0

(3)CF=0、SF=1、OF=0、ZF=0

(4)CF=0、SF=1、OF=0、ZF=0

11、

(1)(BX)=009AH

(2)(BX)=0061H

(3)(BX)=00FBH(4)(BX)=001CH

(5)(BX)=0000H(6)(BX)=00E3H

12、

该程序段是完成将DL寄存器的低4位与AH寄存器的低四位合成一个新的字节(DL寄存器的低4位在前,AH寄存器的低四位在后)

13、

(1)

MOVAX,1234H;(AX)=1234H

MOVCL,4;(AX)=1234H

ROLAX,CL;(AX)=2341H

DECAX;(AX)=2340H

MOVCX,4;(AX)=2340H

MULCX;(AX)=3400H

(2)

MOVAX,1234H;CF=0、SF=0、ZF=0

MOVCL,4;CF=0、SF=0、ZF=0

ROLAX,CL;CF=0、SF=0、ZF=0

DECAX;CF=0、SF=0、ZF=0

MOVCX,4;CF=0、SF=0、ZF=0

MULCX;CF=1、SF=0、ZF=0

(3)AX=3400H,DX=002H

14、

(1);AX=14C6H,BX=80DCH

ADDAX,BX;AX=95A2H

JNCL2;CF=0,在此转向L2

SUBAX,BX

JNCL3

JMPSHORTL5

所以转向L2处执行

(2);AX=B568H,BX=54B7H

ADDAX,BX;AX=4B0AH

JNCL2;CF=1

SUBAX,BX;B568H

JNCL3;CF=1

JMPSHORTL5;执行该指令

所以转向L5处执行

15、

MOVCX,5

LEASI,OLDS

LEADI,NEWS

CLRDF

NEXT:

CMPSB

JZNEWS_LESS

LOOPNEXT

……

NEWS_LESS:

……

第124页

1、

(1)STADDB18,-59,0ABH,49H

(2)ARRAYDW1235H,65H,100,0C7H

(3)ALPHADD12H,12345678H,0EH

(4)BETADB4DUP(8),6DUP(‘A’),10DUP(?

),10DUP(5,6)

(5)STRINGDB‘THISISASTR’

(6)SUMEQU180

2、

3、

COUNT的值为10,他表示X2、X3两个数组所占字节空间数

4、

5、

字数据3000H的偏移地址为33H

6、

(1)LEABX,BUF1;或MOVBX,OFFSETBUF1

(2)MOVAL,BYTEPTR[BUF2+4]

(3)MOVAL,24H

MOV[BUF3+2],AL

(4)COUNTEQUBUF4-BUF2

(5)MOVAX,BUF2+1

MOVBL,BUF4

MOVBH,0

ADDAX,BX

MOVBUF3,AL

MOVBUF3+1,AH

7、

(1)AX=0A47CH

(2)BX=6752H

(3)CH=67H

(4)DL=34H

(5)DH=4

8、先执行后面的AND指令,得09h

后执行前面的AND指令,AX=9

ANDAX,9

9、

MOVBX,AX

MOVDX,0

SALAX,1

RCLDX,1

ADDAX,BX

ADCDX,0

SALAX,1

RCLDX,1

ADDAX,BX

ADCDX,0

10、AX=1D00H

11、

DATASEGMENT

BUFDW0ABC3H,0F7AH,6E78H

FLAGDB?

DATAENDS

CODESEGMENT

ASSUMECS:

CODE,DS:

DATA

MOVAX,DATA

MOVDS,AX

MOVAX,BUF

CMPAX,BUF+2

JZEQ1

CMPAX,BUF+4

JZEQ2

MOVAX,BUF+2

CMPAX,BUF+4

JZEQ2

MOVFLAG,0

JMPEXIT

EQ1:

CMPAX,BUF+4

JNZEQ2

MOVFLAG,2

JMPEXIT

EQ2:

MOVFLAG,1

EXIT:

MOVAH,4CH

INT21H

CODEENDS

END

12、

次数

AX

CX

0

100

5

1

95

4

2

91

3

3

88

2

4

86

1

5

85

0

AX=85,CX=0

13、

次数

AL

CX

N2

1

5

4

5

2

6

3

6

3

7

2

7

4

8

1

8

5

9

0

9

所以N2区的数据依次为:

5、6、7、8、9

14、

DATASEGMENT

DAT1DW0ABC3H,0F7AH,6E78H,3,6,9,3,0

Dw3,643,5324,324,995,67,6575,68;这里定义100个数

MAXDW8000H

MINDW7FFFH

DATAENDS

CODESEGMENT

ASSUMECS:

CODE,DS:

DATA

MOVAX,DATA

MOVDS,AX

MOVCX,100

MOVSI,OFFSETDAT1

LOP:

MOVAX,[SI]

CMPAX,MAX

JLLITTLE

MOVMAX,AX

JMPNEXT

LITTLE:

CMPAX,MIN

JGEQ2

MOVMIN,AX

NEXT:

INCSI

LOOPLOP

MOVAH,4CH

INT21H

CODEENDS

END

15、

DATASEGMENT

NUMDB0ABH,0C3H,0F7H,3AH,6EH,78H,3,6,9,3,0

DB3H,63H,53H,24,3,24,99,5,67H,65,75,68;这里定义100个数

CNTDB$-NUM

PLUSDBCNTDUP(?

)

DATAENDS

CODESEGMENT

ASSUMECS:

CODE,DS:

DATA

MOVAX,DATA

MOVDS,AX

MOVCX,CNT

MOVSI,OFFSETNUM

MOVDI,OFFSETPLUS

LOP:

MOVAL,[SI]

CMPAL,0

JLNEXT

MOV[DI],AL

INCDI

NEXT:

INCSI

LOOPLOP

MOVAH,4CH

INT21H

CODEENDS

END

16、

DATASEGMENT

ARRAYDB34H,53H,063H,3AH,64H,78,30,60,90,63,80

DB73H,63H,53H,84,83,64,99,65,67H,26,75,68;这里定义200个数

CNTDB200

NUM90DB0

NUM80DB0

NUM70DB0

NUM60DB0

NUMDB0

LTEVDB0

DATAENDS

CODESEGMENT

ASSUMECS:

CODE,DS:

DATA

MOVAX,DATA

MOVDS,AX

MOVCL,CNT

MOVCH,0

MOVSI,OFFSETNUM

MOVDX,0

LOP:

MOVAL,[SI]

CMPAL,90

JLNEXT1

INCNUM90

JMPNEXT

NEXT1:

CMPAL,80

JLNEXT2

INCNUM80

JMPNEXT

NEXT2:

CMPAL,70

JLNEXT3

INCNUM70

JMPNEXT

NEXT3:

CMPAL,60

JLNEXT4

INCNUM60

JMPNEXT

NEXT4:

INCNUM

JMPNEXT

NEXT:

MOVAH,0

ADDDX,AX

INCSI

LOOPLOP

MOVAX,DX

DIVCNT

MOVLTEV,AL

MOVAH,4CH

INT21H

CODEENDS

END

17、

CODESEGMENT

ASSUMECS:

CODE

NEXT :

MOVAL,1

INT21H

CMPAL,’*’

JZEXIT

CMPAL,’a’

JBNEXT

CMPAL,’z’

JANEXT

SUBAL,20H

MOVDL,AL

MOVAH,2

INT21H

JMPNEXT

EXIT:

MOVAH,4CH

INT21H

CODEENDS

END

18、

DATASEGMENT

DATDB34H,’#’,‘#’,3AH,64H,78,30,60,90,63,80,”ETEWTRGEG#”,’9’

DB73H,63H,53H,84,83,64,99,65,67H,’#’,75,68;这里定义100个数

CUTDB00

DATAENDS

CODESEGMENT

ASSUMECS:

CODE,DS:

DATA

MOVAX,DATA

MOVDS,AX

MOVCX,100

MOVSI,OFFSETDAT

LOP:

MOVAL,[SI]

CMPAL,’#’

JNZNEXT

INCCUT

NEXT:

INCSI

LOOPLOP

MOVAX,DX

DIVCNT

MOVLTEV,AL

MOVAH,4CH

INT21H

CODEENDS

END

19、

DATASEGMENT

ARRAYDB“wdeqwdfvfbrexzacvrgrewafkazc$”

DATAENDS

CODESEGMENT

ASSUMECS:

CODE,DS:

DATA

MOVAX,DATA

MOVDS,AX

MOVSI,OFFSETNUM

Movdi,si

LOPW:

MOVBL,[DI]

CMPBL,’$’

JZEXIT

LOPN:

INCSI

MOVAL,[SI]

CMPAL,’$’

JZEXIT1

CMPAL,[DI]

JAENEXT

MOV[DI],AL

MOV[SI],BL

NEXT:

INCSI

JMPLOPN

EXIT1:

INCDI

JMPLOPW

Exit:

MOVAH,4CH

INT21H

CODEENDS

END

20、

.MODELSMALL

.DATA

DAT1DB30H,31H,32H,33H,34H,35H,36H,37H,38H,39H,41H,42H,43H,44H,45,46H

DAT2DB1,2,3,5,0AH,4,9,0,7,0FH,0BH,4,3,7

COUNTDW$-DAT2

DAT3DB20DUP(?

),'$'

.CODE

MOVAX,@DATA

MOVDS,AX

MOVSI,OFFSETdat2

LEADI,DAT3

MOVCX,COUNT

MOVBX,OFFSETDAT1

LOPW:

MOVAL,[SI]

XLAT

MOV[DI],AL

INCSI

INCDI

LOOPLOPW

LEADX,DAT3

MOVAH,9

INT21H

MOVAH,4CH

INT21H

END

21、

CODESEGMENT

ASSUMECS:

CODE

MOVCX,10

MOVBL,00;最大值

MOVBH,0FH;最小值

LOPN:

MOVAH,1

INT21H

SUBAL,30H

CMPAL,BH

JAEABOVE

MOVBH,AL

ABOVE:

CMPAL,BL

JBENEXT

MOVBL,AL

NEXT:

MOVDL,BH

ADDDL,30H

MOVAH,2

INT21H

MOVDL,BL

ADDDL,30H

MOVAH,2

INT21H

MOVAH,4CH

INT21H

CODEENDS

END

第151页

1~3略

4、由于计算机的CPU速度很高,而主RAM存储器速度低于微处理器的速度。

高速缓冲存是一种特殊的存储器,高速缓冲存储器总是比主RAM存储器速度快。

这样在CPU与主存之间插入高速缓存器,CPU直接从高速缓存中取数据,访问快速快。

CPU不需要从主存储器中读取数据直接从高速缓存读数据。

5、存储器和CPU连接包括数据总线连接、地址总线连接、控制总线连接,连接时注意如下问题:

①在小型系统中,CPU总线的负载能力是可以驱动存储器系统的。

但当CPU和大容量的标准ROM、RAM一起使用或扩展成一个多插件系统时,就必须用接入缓冲器或总线驱动器等方法增加CPU总线的驱动能力。

地址总线只需接入单向的驱动器,例如74LS244、74LS373等,数据总线需要接入双向驱动器,例如74LS245等。

②存储器与CPU的速度匹配问题

在选择存储器芯片时,就应考虑与CPU速度的匹配问题。

CPU严格按照存储器读写周期的时序进行读写操作,当存储器速度跟不上CPU时序时,设计系统时应注意插入TW。

但随着大规模集成电路的发展,目前存储器芯片与CPU的速度匹配已不成大问题。

③存储器的寻址方法

存储器芯片与CPU地址总线的连接方式,必须满足对这些芯片所分配的地址范围的要求。

CPU发出的地址信号必须实现两种选择:

首先对存储器芯片的选择,使相关芯片的片选端CS为有效,这称为片选。

然后在选中的芯片内部再选择某一存储单元,这称为字选。

片选信号和字选信号均由CPU发出的地址信号经译码产生。

片选信号由存储器芯片的外部译码电路产生,这部分译码电路用户不需设计。

6、

(1)对于16KX8bit的芯片的引脚:

地址线14条,数据线8条,电源线2条,控制线:

读、写、片选,所以该芯片最小的引脚数为14+8+2+1+1+1=23

(2)14个引脚如下:

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

最小

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0000H

…

…

…

…

…

…

…

…

…

…

…

…

…

…

……

最大

1

1

1

1

1

1

1

1

1

1

1

1

1

1

3FFFH

所以其地址范围为0000H~3FFFH

7、

①全译码方式:

存储器芯片中的每一个存储单元对应一个唯一的地址。

译码需要的器件多;

②部分译码方式:

存储器芯片中的一个存储单元有多个地址。

译码简单;

③线选方式:

存储器芯片中的一个存储单元有多个地址。

地址有可能不连续。

不需要译码。

8、

能储存数据的容量为(214×8)/8=16KB

(16K×8bit)/(8K×4bit)=4(片)

9、

(1)能储存数据的容量为(216×8)/8=64KB

(2)(64K×8bit)/(8K×4bit)=16(片)

(3)∵24=16

∴需要4位地址线作为片选

10、(8K×8bit)/(2K×4bit)=8(片)

第一组芯片片选信号为A13=0,片选逻辑为A19A18A17A16A15A14A13=0001110

第二组芯片片选信号为A14=0,片选逻辑为A19A18A17A16A15A14A13=0001101

第三组芯片片选信号为A15=0,片选逻辑为A19A18A17A16A15A14A13=0001011

第四组芯片片选信号为A16=0,片选逻辑为A19A18A17A16A15A14A13=0000111

第一组芯片地址范围为:

1C000H~1DFFFH

第二组芯片地址范围为:

1A000H~1BFFFH

第三组芯片地址范围为:

16000H~17FFFH

第四组芯片地址范围为:

0E000H~0FFFFH

11、

(4K×16bit)/(1K×8bit)=8(片)

存储器的地址低10(A9~A0)位作为片内寻址,再用(A10、A11、A12、A13)4位作为片选信号,其余未用

第一组芯片片选信号为A13=0,片选逻辑为A19A18A17A16A15A14A13A12A11A10=0000000111

第二组芯片片选信号为A12=0,片选逻辑为A19A18A17A16A15A14A13A

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 微机原理与接口技术习题 答案修订版 微机 原理 接口 技术 习题 答案 修订版

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx