湖工大 抢答器万年历 EDA课程设计.docx

湖工大 抢答器万年历 EDA课程设计.docx

- 文档编号:11113063

- 上传时间:2023-02-25

- 格式:DOCX

- 页数:28

- 大小:410.09KB

湖工大 抢答器万年历 EDA课程设计.docx

《湖工大 抢答器万年历 EDA课程设计.docx》由会员分享,可在线阅读,更多相关《湖工大 抢答器万年历 EDA课程设计.docx(28页珍藏版)》请在冰豆网上搜索。

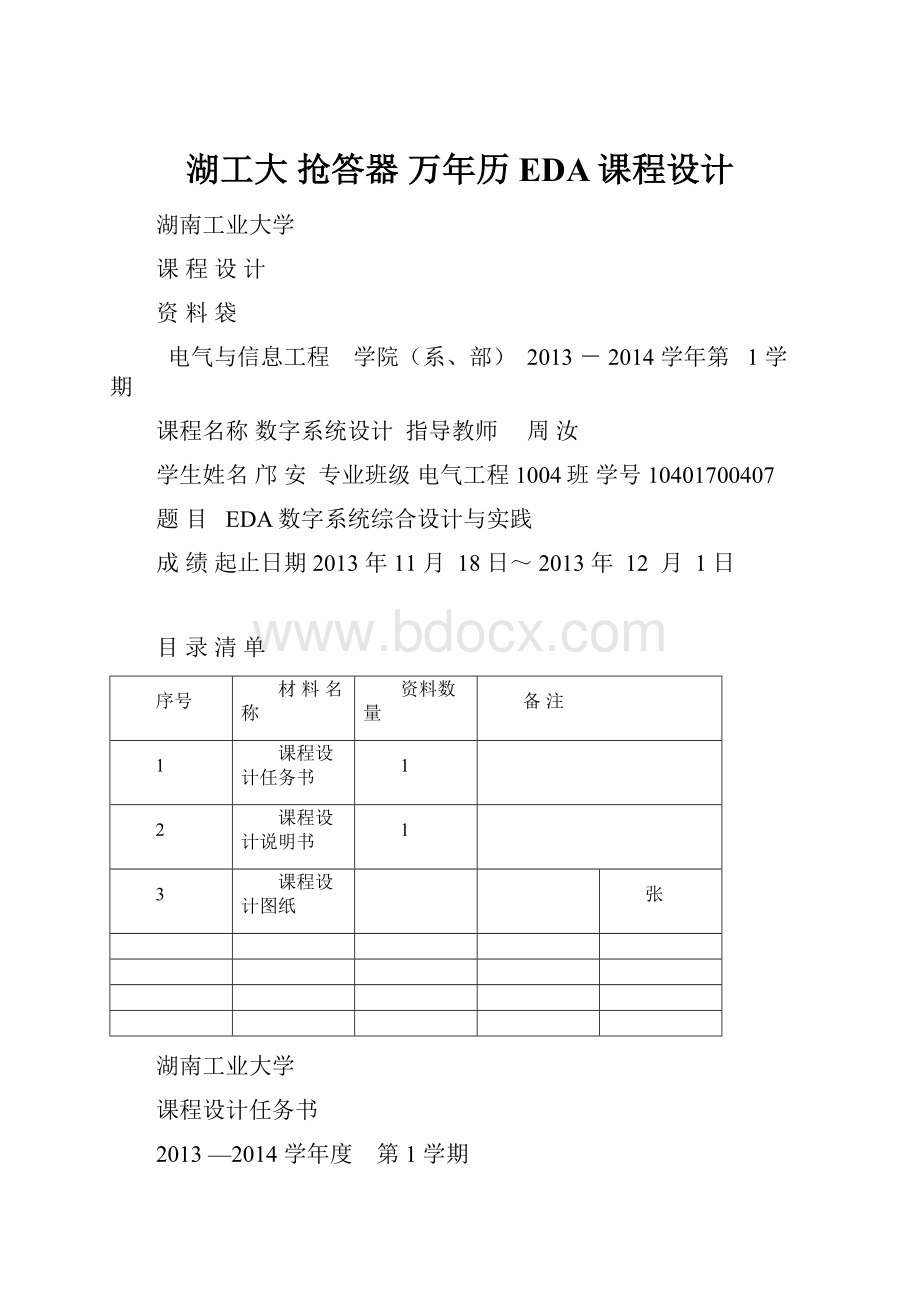

湖工大抢答器万年历EDA课程设计

湖南工业大学

课程设计

资料袋

电气与信息工程学院(系、部)2013-2014学年第1学期

课程名称数字系统设计指导教师周汝

学生姓名邝安专业班级电气工程1004班学号10401700407

题目EDA数字系统综合设计与实践

成绩起止日期2013年11月18日~2013年12月1日

目录清单

序号

材料名称

资料数量

备注

1

课程设计任务书

1

2

课程设计说明书

1

3

课程设计图纸

张

湖南工业大学

课程设计任务书

2013—2014学年度 第1学期

电气与信息工程学院(系、部)电气工程及其自动化专业1004班

课程名称:

数字系统设计

设计题目:

EDA数字系统综合设计与实践

完成期限:

2013年11月18日~2013年12月1日共2周

内

容

及

任

务

数字系统设计,就是要求学生利用EDA技术进行综合性的数字电子系统设计,培养学生综合应用能力、独立设计与安装调试能力,并树立工程设计观念。

具体任务如下:

(1)智力抢答器的设计与实现:

包括系统设计原理,VHDL等程序设计,时序仿真与分析,逻辑综合与分析等;

(2)综合计时系统的设计:

包括系统设计原理,VHDL等程序设计,时序仿真与分析,逻辑综合与分析、硬件验证等;

各子课题的设计具体要求详见附件一。

进

度

安

排

起止日期

工作内容

第13周周一上午08:

00-12:

00

布置任务,讲解课题设计要求(电204)

第14周周五上午08:

00-12:

00

智力抢答器的设计(电204)

第14周周六上午08:

00-12:

00

综合计时系统的设计(电204)

第14周周六下午14:

00-17:

00

设计验收(电204)

其它时间

学生自行查找资料,自行进行实践,撰写报告

主

要

参

考

资

料

[1]谭会生,张昌凡.EDA技术及应用(第三版)[M].西安:

西安电子科技大学出版社,2011

[2]谭会生,瞿遂春.EDA技术综合应用实例与分析[M].西安:

西安电子科技大学出版社,2004

指导教师(签字):

2013年12月1日

系(教研室)主任(签字):

2013年12月1日

数字系统设计课程

设 计 说 明 书

EDA数字系统综合设计与实践

起止日期:

2013年11月18日~2013年12月1日共2周

学生姓名

邝安

班级

电气工程1004班

学号

10401700407

成绩

指导教师(签字)

电气与信息工程学院

2013年11月30日

一智力抢答器的设计与实现

(一)系统设计要求:

在许多比赛活动中,为了准确、直观地判断抢答者,通常设置一台抢答器,并通过灯光、声响、数码管等显示出第一抢答者,同时还可完成计分、扣分等功能。

本设计具体要求如下:

(1)设计一个可供四组参赛者使用的抢答器,每组设置一个抢答按钮;

(2)电路具有第一抢答信号的鉴别功能,当主持人按下清零复位键后,开始抢答,将第一抢答者组别实现出来(数码管显示组号,LED指示灯点亮,并发出“嘀”的声音);

(3)设置计分电路,四组参赛者在开始时预置成100分。

抢答后回答正确的加10分,错误则扣10分,将计分结果用数码管显示出来;

*(4)设置总显示按钮,当主持人按下按钮后,可将每组的得失分情况用数码管直观地显示出来。

(二)系统设计方案:

采用自顶向下的调试方法进行设计,将设计分为抢答模块、计分模块、数据选择模块以及译码显示模块。

(1)抢答模块

主要完成4组参赛者抢答鉴别功能。

CLR=0时输出清零,CLR=1时,A、B、C、D哪组输入为1(用实验箱逻辑电平开关代替抢答键),相应路输出有效信号1,并点亮组别指示灯。

两组同时抢答无效。

其VHDL源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYQDJBIS

PORT(CLR:

INSTD_LOGIC;

A,B,C,D:

INSTD_LOGIC; --4个组

A1,B1,C1,D1:

OUTSTD_LOGIC;

STATES:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDENTITYQDJB;

ARCHITECTUREARTOFQDJBIS

CONSTANTW1:

STD_LOGIC_VECTOR:

=”0001”;

CONSTANTW2:

STD_LOGIC_VECTOR:

=”0010”;

CONSTANTW3:

STD_LOGIC_VECTOR:

=”0100”;

CONSTANTW4:

STD_LOGIC_VECTOR:

=”1000”;

BEGIN

PROCESS(CLR,A,B,C,D)IS

BEGIN

IFCLR='1'THENSTATES<="0000";

ELSIF(A<='1'ANDB<='0'ANDC<='0'ANDD<='0')THEN

A1<=’1’;B1<=’0’;C1<=’0’;D1<=’0’;STATES<=W1;

ELSIF(A<='0'ANDB<='1'ANDC<='0'ANDD<='0')THEN

A1<=’0’;B1<=’1’;C1<=’0’;D1<=’0’;STATES<=W2;

ELSIF(A<='1'ANDB<='0'ANDC<='1'ANDD<='0')THEN

A1<=’1’;B1<=’0’;C1<=’1’;D1<=’0’;STATES<=W3;

ELSIF(A<='0'ANDB<='0'ANDC<='0'ANDD<='1')THEN

A1<=’0’;B1<=’0’;C1<=’0’;D1<=’1’;STATES<=W4;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREART;

抢答鉴别模块(QDJB)仿真波形

(2)计分模块

主要完成加减计分功能。

当有1组抢答成功后,EN1为1,启动该组计分模块。

CLK3为计分脉冲(用单次脉冲开关代替),ADD为加分使能键,为1有效。

DEC为减分使能键,为1有效。

每组初始分为100分,抢答后回答正确的加10分,错误则扣10分,结果百位、十位、个位分别用4位二进制表示。

VHDL源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJFQIS

PORT(RST:

INSTD_LOGIC;

ADD:

INSTD_LOGIC;

CHOS:

INSTD_LOGIC_VECTOR(3DOWNTO0);

OUT1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDENTITYJFQ;

ARCHITECTUREARTOFJFQIS

BEGIN

PROCESS(RST,ADD,CHOS)IS

VARIABLEPOINTS_A0:

STD_LOGIC_VECTOR(3DOWNTO0);

VARIABLEPOINTS_B0:

STD_LOGIC_VECTOR(3DOWNTO0);

VARIABLEPOINTS_C0:

STD_LOGIC_VECTOR(3DOWNTO0);

VARIABLEPOINTS_D0:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IF(ADD'EVENTANDADD='1') THEN

IFRST='1'THEN

POINTS_A0:

="0000";

POINTS_B0:

="0000";

POINTS_C0:

="0000";

POINTS_D0:

="0000";

ELSIFCHOS="0001"THEN

IFPOINTS_A0="1001"THEN

POINTS_A0:

="0000";

ELSE

POINTS_A0:

=POINTS_A0+1;

ENDIF;

ELSIFCHOS="0010"THEN

IFPOINTS_B0="1001"THEN

POINTS_B0:

="0000";

ELSE

POINTS_B0:

=POINTS_B0+1;

ENDIF;

ELSIFCHOS="0011"THEN

IFPOINTS_C0="1001"THEN

POINTS_C0:

="0000";

ELSE

POINTS_C0:

=POINTS_C0+1;

ENDIF;

ELSIFCHOS="0100"THEN

IFPOINTS_D0="1001"THEN

POINTS_D0:

="0000";

ELSE

POINTS_D0:

=POINTS_D0+1;

ENDIF;

ENDIF;

ENDIF;

IFchos="0001"thenout1<=POINTS_a0;

ELSIFchos="0010"thenout1<=POINTS_b0;

ELSIFchos="0011"thenout1<=POINTS_c0;

ELSIFchos="0100"thenout1<=POINTS_D0;

ELSIFchos="0000"thenout1<="0000";

ENDIF;

ENDPROCESS;

ENDARCHITECTUREART;

记分模块(JFQ)仿真波形

(3)计时模块JSQ

本系统的计时器电路既有计时初始值的预置功能,又有减计数功能。

其中,初始值的预置功能是将两位数分解成两个数分别进行预置。

计时模块(JSQ)仿真波形框图

其VHDL源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYJSQIS

PORT(CLR,LDN,EN,CLK:

INSTD_LOGIC;

TA,TB:

INSTD_LOGIC_vector(3DOWNTO0);

QA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);--gewei

QB:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));--shiwei

ENDENTITYJSQ;

ARCHITECTUREARTOFJSQIS

BEGIN

PROCESS(CLK)IS

VARIABLETMPA:

STD_LOGIC_VECTOR(3DOWNTO0);

VARIABLETMPB:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFCLR='1'THENTMPA:

="0000";TMPB:

="0110";--清零,倒计时60秒

ELSIFCLK'EVENTANDCLK='1'THEN

IFLDN='1'THENTMPA:

=tA;TMPB:

=tB;--置数控制,如果不想要60可以从TA,TB输入倒计时秒数

ELSIFEN='1'THEN--计时开始

IFTMPA="0000"THEN--遇到9则自动变为0,否则减一

TMPA:

="1001";

IFTMPB="0000"THENTMPB:

="0110";

ELSETMPB:

=TMPB-1;

ENDIF;

ELSETMPA:

=TMPA-1;

ENDIF;

ENDIF;

ENDIF;

QA<=TMPA;QB<=TMPB;

ENDPROCESS;

ENDARCHITECTUREART;

计时模块(JSQ)仿真波形

(4)译码显示模块

主要完成数码管动态扫描显示。

将计分结果百位、十位、个位的4位二进制转化为“0-9”8位字型段码,LEDW为数码管位选信号,“000”对应右边第1个数码管,“001”对应右边第2个数码管,…,依此类推。

CLK2为1KHZ动态扫描脉冲。

其VHDL源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYYMQIS

PORT(AIN4:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DOUT7:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDYMQ;

ARCHITECTUREARTOFYMQIS

BEGIN

PROCESS(AIN4)

BEGIN

CASEAIN4IS

WHEN"0000"=>DOUT7<="1111110"; --0

WHEN"0001"=>DOUT7<="0110000"; --1

WHEN"0010"=>DOUT7<="1101101"; --2

WHEN"0011"=>DOUT7<="1111001"; --3

WHEN"0100"=>DOUT7<="0110011"; --4

WHEN"0101"=>DOUT7<="1011011"; --5

WHEN"0110"=>DOUT7<="1011111"; --6

WHEN"0111"=>DOUT7<="1110000"; --7

WHEN"1000"=>DOUT7<="1111111"; --8

WHEN"1001"=>DOUT7<="1111011"; --9

WHENOTHERS=>DOUT7<="0000000";

ENDCASE;

ENDPROCESS;

ENDARCHITECTUREART;

译码器显示模块(YMQ)仿真波形

(5)顶层文件

其VHDL源程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYqdqIS

PORT(qd:

INSTD_LOGIC_VECTOR(3DOWNTO0);

clk,en,ldn,add,rst,clrqd,clrsjINstd_logic;

ta,tb:

INSTD_LOGIC_VECTOR(3DOWNTO0);

qdo:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

out1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

out2:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

out4:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

out3:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

END;

ARCHITECTUREaaOFqdqIS

COMPONENTqdjbIS

PORT(CLR:

INSTD_LOGIC;

A,B,C,D:

INSTD_LOGIC;

A1,B1,C1,D1:

OUTSTD_LOGIC;

STATES:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDcomponentQDJB;

COMPONENTjsqIS

PORT(CLR,LDN,EN,CLK:

INSTD_LOGIC;

TA,TB:

INSTD_LOGIC_vector(3downto0);

QA:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

QB:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCOMPONENTJSQ;

COMPONENTymqIS

PORT(AIN4:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DOUT7:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDCOMPONENTYMQ;

COMPONENTjfqIS

PORT(RST:

INSTD_LOGIC;

ADD:

INSTD_LOGIC;

CHOS:

INSTD_LOGIC_VECTOR(3DOWNTO0);

out1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCOMPONENTJFQ;

signaltmp1,tmp2,tmp3,tmp4:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

u1:

qdjbPORTmap(clr=>clrqd,a=>qd(0),b=>qd

(1),c=>qd

(2),d=>qd(3),

a1=>qdo(0),b1=>qdo

(1),c1=>qdo

(2),d1=>qdo(3),STATES=>tmp1);

u2:

jfqPORTmap(rst=>rst,add=>add,chos=>tmp1,out1=>out2);

u3:

jsqPORTmap(clr=>clrsj,ldn=>ldn,en=>en,clk=>clk,ta=>ta,tb=>tb,qa=>out3,qb=>out4);

out1<=tmp1;

END;

顶层文件仿真图:

在这个模块中是对前几个模块的综合编写的顶层文件。

顶层参考电路原理图

二综合计时系统设计与分析

(一)系统设计要求

设计一个综合性的计时系统,要求能实现年、月、日、时、分、秒及星期的计数等综合计时功能,同时将计时结果通过15个七段数码管显示,并且可通过两个设置键,对计时系统的有关参数进行调整。

具体系统功能面板如图2-1所

图2-1系统功能面板

根据系统设计要求可知,本综合计时系统可分成三个主要模块:

综合计时电路、显示控制电路和调整控制电路。

其中综合计时电路用于完成各种计时的功能,在面板上体现为面板上方的15个七段数码管,依次可以显示年、月、日、时、分、秒及星期;显示控制电路用于完成计时结果的显示控制及显示译码等功能,集成后体现为面板下方左侧的按键电路;而调整控制电路则用于调整计时系统的有关参数,可参照面板上右下角的两个按键:

模式和调整。

(二)系统设计方案

2.1综合计时电路的设计

根据系统的设计要求,综合计时电路可分为计秒电路、计分电路、计时电路、计星期电路、计日电路、计月电路、计年电路等7个子模块,这7个子模块必须都具有预置、计数和进位功能,设计思想如下:

(1)计秒电路:

以直接输入或由分频器产生的秒脉冲作为计秒电路的计数时钟信号,待计数至60瞬间,进位,计分电路加1,而计秒电路则清零并重新计秒。

(2)计分电路、计时电路:

其设计思想与计秒电路类似。

(3)计日电路:

将计时电路产生的进位脉冲信号作为计日电路的计数时钟信号,通过系统辨认,确定本月总天数X(包括28、29、30、31四种情况),待计数至X+1瞬间,进位,计月电路加1,而计日电路返回1重新开始计数。

(4)计星期电路:

将计时电路产生的进位脉冲信号作为计星期电路的计数时钟信号,待计数至7瞬间,计星期电路返回1重新开始计数。

(5)计月电路:

将计日电路产生的进位脉冲信号作为计月电路的计数时钟信号,待计数至12瞬间,进位,计年电路加1,而计月电路返回1重新开始计数。

(6)计年电路:

将计月电路产生的进位脉冲信号作为计年电路的计数时钟信号,待计数至100瞬间,计年电路返回0重新开始计数。

(注:

由于本系统的计年范围仅为2000~2099年,所以计年模块只对年份的后两位进行计数,年份的前两位始终保持为“20”。

)

下面介绍CNT60、CNT30计数模块的设计[11]。

CNT60计数模块是一个多用计时模块,它既可作为计秒电路调用,又可作为计分电路、计时电路调用。

图2-2是其输入、输出端口图。

其中,输入信号LD为置数控制信号,低电平有效;输入信号CLK为计数时钟信号;输入信号DATA为待预置数;输出信号NUM为计数结果;输出信号CO为计数溢出信号。

图2-2CNT60计数模块输入、输出端口

CNT30计数模块是一个计日模块。

由于该计数模块涉及到大小月及闰年问题,所以CNT30的计数范围并非固定不变,而是存在1~28、1~29、1~30及1~31这四种情况。

图2-3是其输入、输出端口图。

其中输入信号LD为置数控制信号,低电平有效;输入信号CLK为计数时钟信号;输入信号DATA为待预置数;输入信号NIAN为当前计时的年份数;输入信号YUE为当前计时的月份数;输出信号NUM为计数结果;输出信号CO为计数溢出信号,输出信号MAX_DAYS为当前月的天数。

图2-3CNT30计数模块的输入、输出端口图

(1)CNT60的主要VHDL程序段如下:

IF(LD='0')THEN

NUM<=DATA;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 湖工大 抢答器 万年历 EDA课程设计 抢答 EDA 课程设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《JAVA编程基础》课程标准软件16级.docx

《JAVA编程基础》课程标准软件16级.docx