智力竞赛抢答器设计文档格式.docx

智力竞赛抢答器设计文档格式.docx

- 文档编号:13187146

- 上传时间:2022-10-07

- 格式:DOCX

- 页数:10

- 大小:112.83KB

智力竞赛抢答器设计文档格式.docx

《智力竞赛抢答器设计文档格式.docx》由会员分享,可在线阅读,更多相关《智力竞赛抢答器设计文档格式.docx(10页珍藏版)》请在冰豆网上搜索。

Outlook"

isnotwhattheperformance.

4.peoplerespondedtothestartingpointofthequestion,andrepliedtoquestionspoint.Manisthesumofsocialrelationships.Wecannotleavethechichuanyongdu,housing,tourismandentertainment,entertaining,andevencertainpolitical,economic,culturalandsocialenvironment,andsoon.Duetohumanneeds,allwalksoflifewillcomeintobeing.Peoplecreatefortheirsurvival,andcontinueenjoyingtheresultsoftheconstruction.Colorfulinthetransformationofthepeopleoftheworld,communityvitalityinthecreationofman.Therefore,anyworkwedo,thestartingpointishuman,whatarepeople.Usspeedupdevelopment,thecoreofwhichistomeettheneedsofpeople,includingsurvivalneeds,emotionalneedsandself-actualizationneeds.Itshouldbenotedthatpeoplearenotmachines,nottheslaveofanobject,nottobecontrolled.Peoplehavetheirownpersonality,hasitsownpersonality,hasitsowndignity.Personinneedofcare,youneedtounderstand,needtomeet.Itissaidthatinthe"

agriculturalsociety,peopleplant"

;

in"

industrialsociety,manisananimal"

"

theinformationsociety,return《专业课程设计

(一)》课程设计说明书

智力竞赛抢答器设计

1技术指标

设计一个四组抢答器,有人抢答时,蜂鸣器发声,同时优先抢答者对应的指示灯亮,而后抢答者对应的指示灯不亮。

主持人具有将抢答器复原的功能。

2设计方案及其比较

2.1方案一

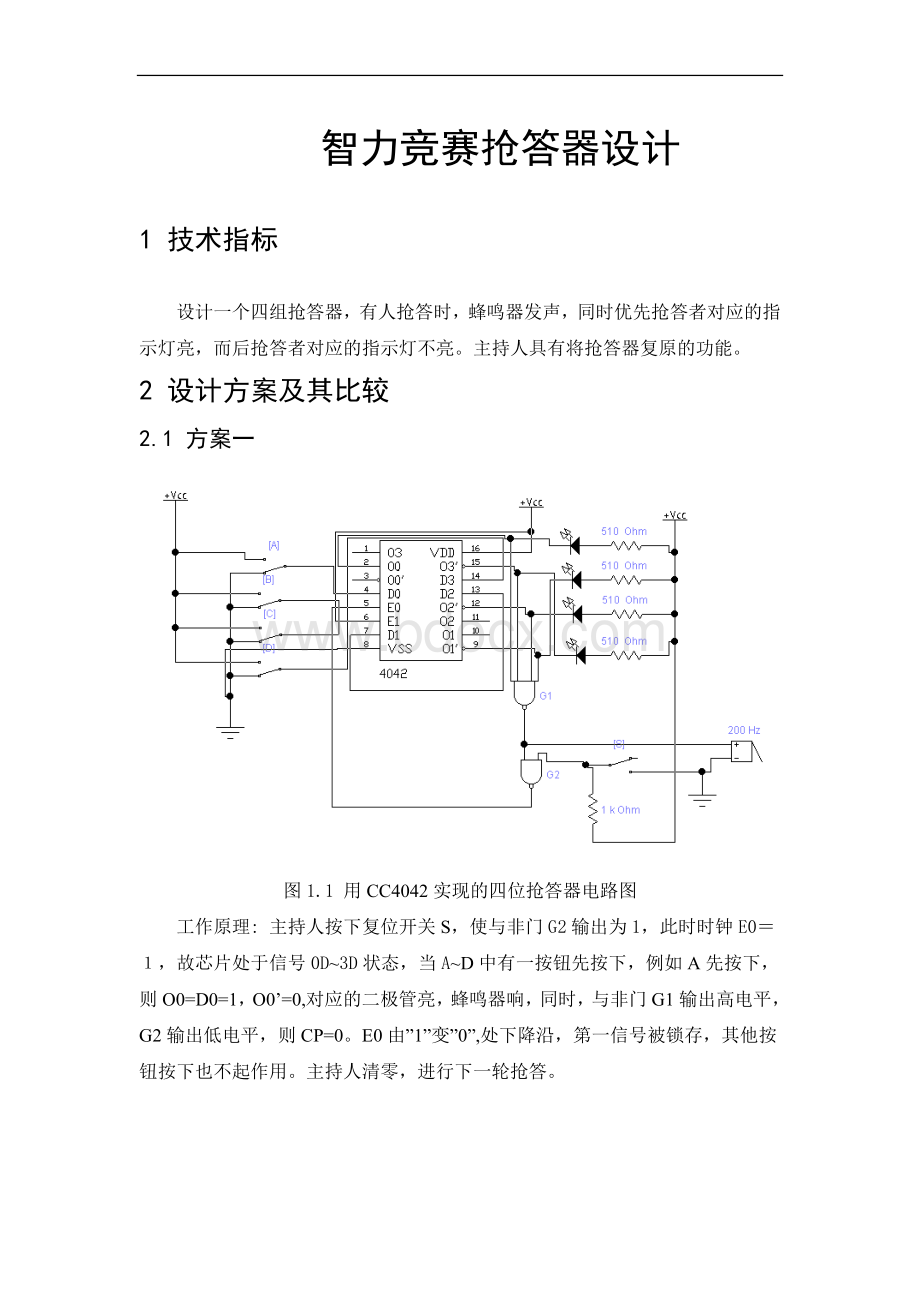

图1.1用CC4042实现的四位抢答器电路图

工作原理:

主持人按下复位开关S,使与非门G2输出为1,此时时钟E0=1,故芯片处于信号0D~3D状态,当A~D中有一按钮先按下,例如A先按下,则O0=D0=1,O0’=0,对应的二极管亮,蜂鸣器响,同时,与非门G1输出高电平,G2输出低电平,则CP=0。

E0由”1”变”0”,处下降沿,第一信号被锁存,其他按钮按下也不起作用。

主持人清零,进行下一轮抢答。

所用器件引脚图及功能

E0时钟输入端

E1时钟方式控制端

D0~D3数据输入端

O0~O3原码数据输出端

O’0~O’3反码数据输出端

图1.2CC4042锁存器引脚图

H高电平

L低电平

↑低到高电平跳变

↓高到低电平跳变

X任意

表1CC4042锁存器功能表

输入

输出

E0

E1

D

O

O’

L

d

d’

↑

X

锁存

H

↓

功能:

CC4042包含四个锁存器电路。

输入的数据在由E1选择的E0电平期间传送至O和O’输出端,当E1=0,在0E0电平期间传送,当E1=0,在0E0电平期间传送。

当E0电平转换时,输入端数据在此期间保持在输出端。

VDD正电源

VSS地

I1~I8数据输入端

O1,O2数据输出端

逻辑表达式Y=

图1.3CC4012四输入正向逻辑与非门

2.2方案二

图2.1用4D触发器所设计的4位抢答器电路图

工作原理:

主持人用K端清零后,开始抢答。

选手按下A~D任一个开关,例如,按下A开关,则1Q输出高电平,对应的二极管亮,蜂鸣器响。

同时,1Q’输出低电平,则与门G1输出低电平,与非门G2输出,使CLK处于高电平,触发器停止工作,其他选手若按下开关也不会起作用。

VCC正电源

GND地

CLK时钟输入端

CLR’清零端

1D~4D输入端

1Q~4Q输出端

1Q’~4Q’反相输出端

图2.274ls175四D边沿触发器引脚图

Q0规定的稳态输入条件建立前Q的电平

Q0’规定的补码稳态输入条件建立前Q’的电平或Q0的补码

表274ls174四D边沿触发器功能表

CLR’

CLK

Q

Q’

Q0

Q0’

CLR为清零端,低电平有效。

当CLR为高电平时,在时钟CLK上升沿作用下,Q与数据端D相一致,当CLK为高电平或低电平时,D对Q没有影响。

1A~1D数据输入端

2A~2D数据输出端

1Y,2Y数据输出端

逻辑表达式Y=A·

B·

C·

图2.374ls21两组四输入与门引脚图

1A~4D数据输入端

1Y~4Y数据输出端

图2.474ls00二输入四与非门引脚图

2.3方案三

主持人用S端清零后,RS触发器的端均为0,4个触发器输出端1Q~4Q置”0”,灯不亮。

当主持人将S断开时,抢答器处于等待开始状态。

当有选手将A~D任一端按下时,例如按下D,74ls148的输出经RS锁存后,1Q=1,E1=1,74ls148处于禁止工作状态,封锁了其他键的输入,保证了抢答键的优先性,此时,4Q3Q2Q输出100,灯L4亮,蜂鸣器响。

主持人清零,继续下一轮抢答。

所用器材及功能

E1输入使能端

E0输出使能端

GS优先编码状态标志

0~7数据输入端

A0~A2数据输出端

图3.274ls148优先编码器引脚图

表3

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 智力 竞赛 抢答 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整版)固定资产盘点表.xls

(完整版)固定资产盘点表.xls