最新版FPGA毕业课程设计报告Word文档格式.docx

最新版FPGA毕业课程设计报告Word文档格式.docx

- 文档编号:14356872

- 上传时间:2022-10-22

- 格式:DOCX

- 页数:34

- 大小:3.75MB

最新版FPGA毕业课程设计报告Word文档格式.docx

《最新版FPGA毕业课程设计报告Word文档格式.docx》由会员分享,可在线阅读,更多相关《最新版FPGA毕业课程设计报告Word文档格式.docx(34页珍藏版)》请在冰豆网上搜索。

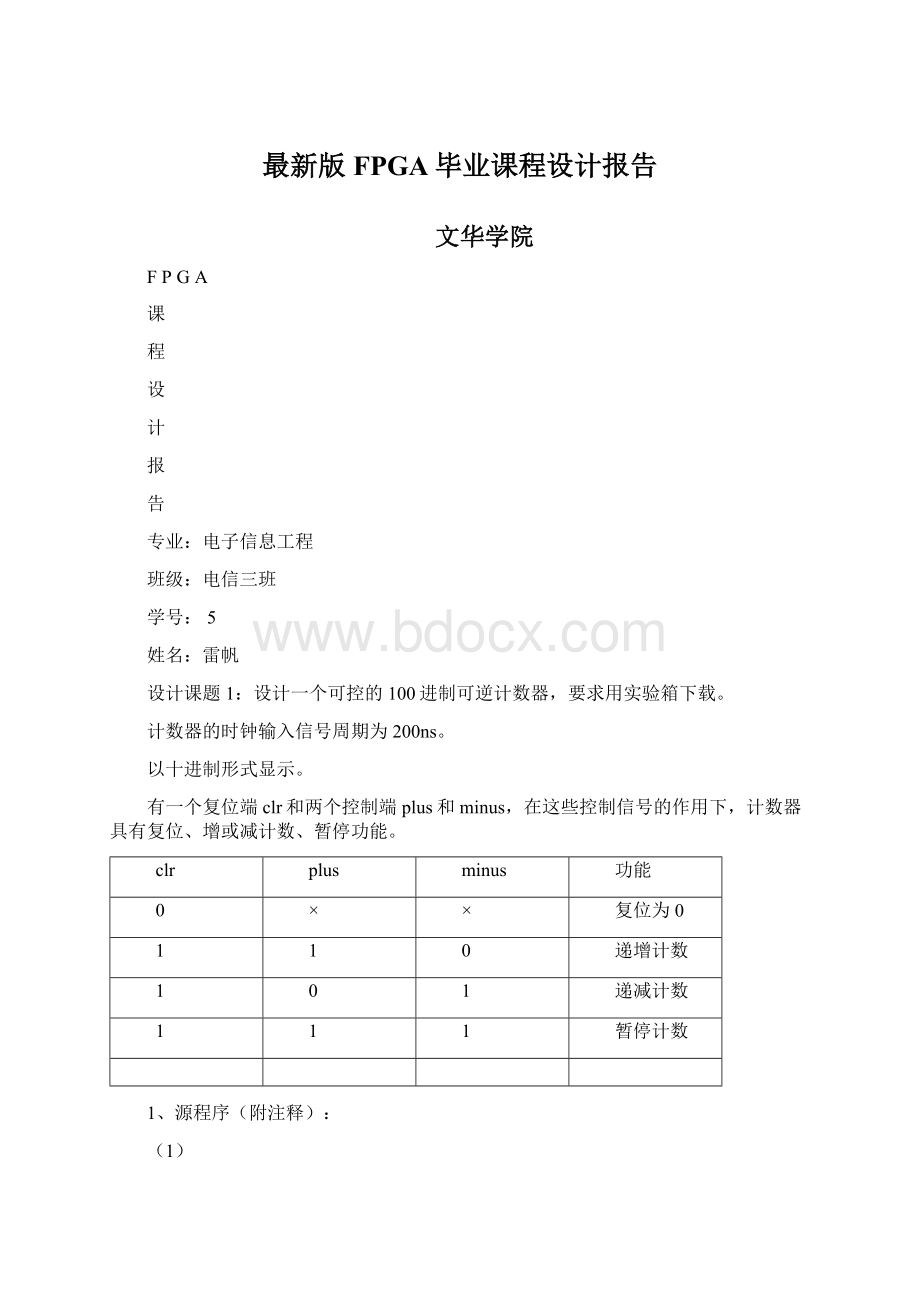

复位为0

1

递增计数

递减计数

暂停计数

1、源程序(附注释):

(1)

modulecounter100(out,clk,clr,plus,minus);

output[7:

0]out;

inputclk,plus,minus,clr;

reg[7:

always@(posedgeclk)

begin

if(!

clr)out<

=0;

//若CLR为0将计数复位为0

else

begin

case({plus,minus})

2'

b10:

begin//若PLUS为1并且MINUS为0

if(out[3:

0]==9)//若计数低四位为9

begin

out[3:

0]<

//将低四位置0

if(out[7:

4]==9)out[7:

4]<

//若高四位为9则将高四位置0

else

out[7:

=out[7:

4]+1;

//否则将高四位加1

end

elseout[3:

=out[3:

0]+1;

//若计数低四位不为9则加1

b01:

begin//若PLUS为0并且MINUS为1

0]==0)//若低四位为0

=9;

//低四位置9

4]==0)out[7:

//若高四位为0高四位置9

4]-1;

//否则高四位减1

0]-1;

//若计数低四位不为0则减1

b11:

out<

=out;

//若PLUS和MINUS同时为1计数为原值不变

default:

out<

endcase

end

endmodule

2、生成的波形图:

counter100:

(1)当clr为0时,复位为0;

当PLUS为1,MILUS为0时按递增计时。

(2)当PLUS为1,MILUS为1时暂停计时。

(3)当PLUS为0,MILUS为1时按递减计时。

3、管脚分配:

4、下载过程等的截图和注解:

(1)为下载选择正确的实验板型号

(2)下载使用的BDF电路图:

(3)开始下载,选择Tools>

Programmer,并单击Start.

设计课题2:

交通灯控制系统,要求用实验箱下载。

(1)设计一个十字路口交通信号灯的定时控制电路。

要求红、绿灯按一定的规律亮和灭,绿灯亮时,表示该车道允许通行;

红灯亮时,该车道禁止通行。

并在亮灯期间进行倒计时,并将运行时间用数码管显示出来。

(2)要求主干道每次通行时间为40秒,支干道每次通行时间为30秒。

每次变换运行车道前绿灯闪烁,持续时间为5秒。

即车道要由主干道转换为支干道时,主干道在通行时间只剩5秒钟时,绿灯闪烁5秒显示,支干道仍为红灯,以便主干道上已过停车线的车继续通行,未过停车线的车停止通行。

同理,当车道由支干道转换为主干道时,支干道绿灯闪烁显示5秒钟,主干道仍为红灯。

(3)定时器要求采用递减计时方式进行计时。

注:

TimeH、TimeL分别表示计数器的高位和低位

HG、HR分别表示主干道的绿灯和红灯

CG、CR分别表示支干道的绿灯和红灯

两个定时时间:

绿灯闪烁和绿灯停止闪烁

源程序(附注释):

moduletraffic00(clk,en,lampar,fag,lampbr,fbg,numa,numb);

inputclk,en;

output[7:

0]numa,numb;

//计时显示

outputfag,fbg,lampar,lampbr;

//fag:

flashagreen

reglampar,lampag,lampbr,lampbg;

//表示主路?

路共四个灯

regtempa,tempb;

//装入计数

reg[2:

0]counta,countb;

//灯亮的顺序

0]ared,agreen,bred,bgreen;

always@(en)

if(!

en)

begin//设置各种灯的预置数

ared<

=8'

b;

agreen<

bred<

bgreen<

if(en)

tempa)

begintempa<

=1;

case(counta)//控制灯亮的顺序

0:

beginnuma<

=agreen;

lampag<

lampar<

counta<

1:

=ared;

lampag<

lampar<

elsebegin//倒计时

if(numa>

8'

b)

beginif(numa[3:

0]==0)

beginnuma[3:

=4'

b1001;

numa[7:

=numa[7:

elsenuma[3:

=numa[3:

if(numa==8'

b)tempa<

elsebeginlampar<

tempa<

end

always@(posedgeclk)//该进程控制B方向的四种灯

tempb)

begintempb<

case(countb)

beginnumb<

=bred;

lampbr<

lampbg<

countb<

=bgreen;

lampbr<

lampbg<

elsebegin

if(numb>

b)//倒计时

if(numb[3:

0]==0)

beginnumb[3:

numb[7:

=numb[7:

elsenumb[3:

=numb[3:

if(numb==2)tempb<

elsebeginlampbr<

tempb<

countb<

assignfag=(numa>

5)?

(lampag?

1:

0):

clk&

lampag;

//主干道绿灯倒数5秒闪耀

assignfbg=(numb>

(lampbg?

lampbg;

//?

干道绿灯倒数5秒闪耀

(2)

moduledecode4_7(

input[3:

0]indec_0,indec_1,indec_2,indec_3,indec_4,indec_5,indec_6,indec_7,

outputreg[6:

0]dout_0,dout_1,dout_2,dout_3,dout_4,dout_5,dout_6,dout_7

);

always@(indec_0orindec_1orindec_2orindec_3orindec_4orindec_5orindec_6orindec_7)

case(indec_0)

4'

h1:

dout_0=7'

b111_1001;

//

h2:

b010_0100;

//||

h3:

b011_0000;

//51

h4:

b001_1001;

h5:

b001_0010;

h6:

b000_0010;

h7:

b111_1000;

//42

h8:

b000_0000;

h9:

b001_1000;

ha:

b000_1000;

hb:

b000_0011;

hc:

b100_0110;

hd:

b010_0001;

he:

b000_0110;

hf:

b000_1110;

h0:

b100_0000;

case(indec_1)

dout_1=7'

case(indec_2)

dout_2=7'

dout_

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 最新版 FPGA 毕业 课程设计 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx