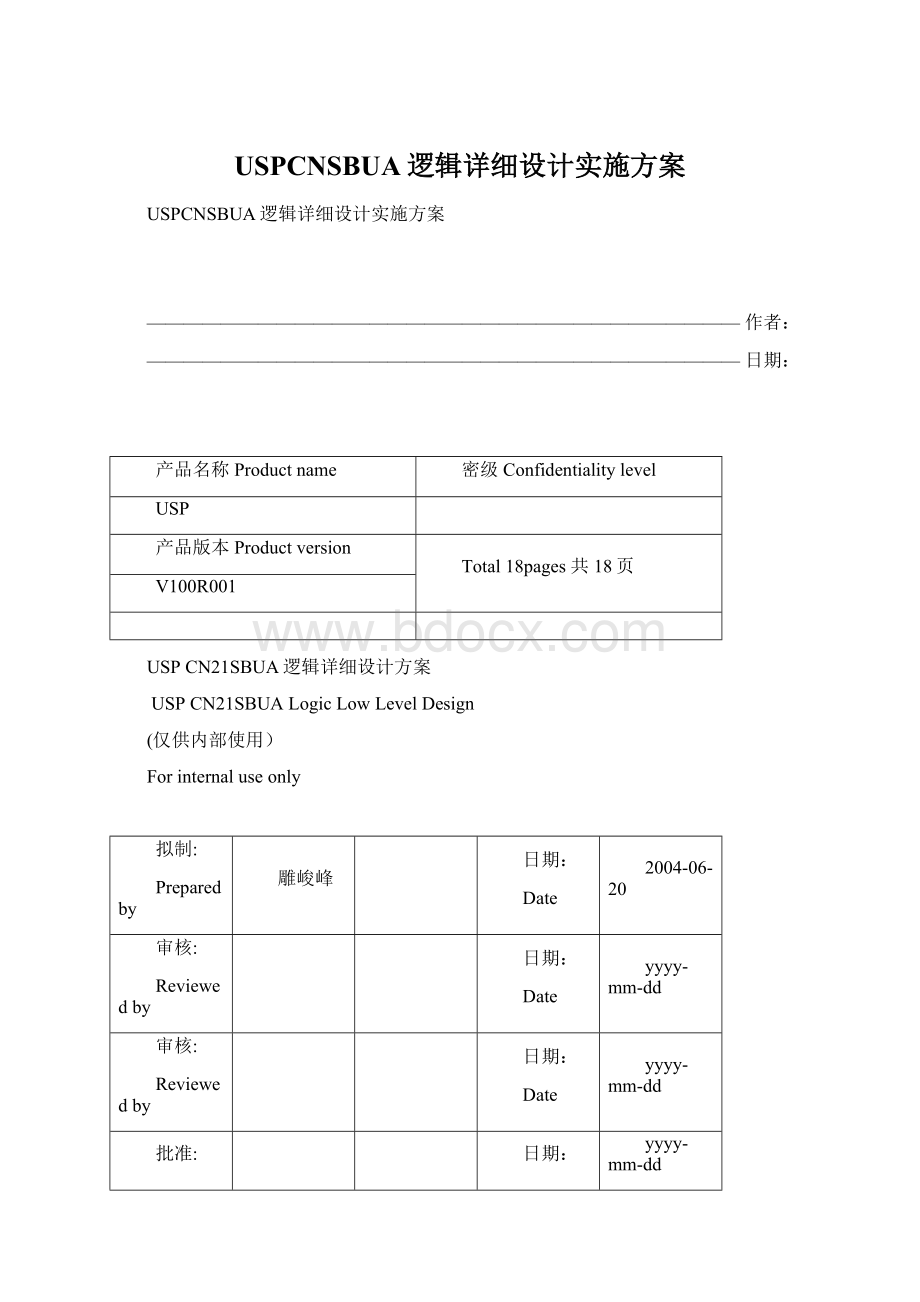

USPCNSBUA逻辑详细设计实施方案Word文档下载推荐.docx

USPCNSBUA逻辑详细设计实施方案Word文档下载推荐.docx

- 文档编号:20884274

- 上传时间:2023-01-26

- 格式:DOCX

- 页数:34

- 大小:82.52KB

USPCNSBUA逻辑详细设计实施方案Word文档下载推荐.docx

《USPCNSBUA逻辑详细设计实施方案Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《USPCNSBUA逻辑详细设计实施方案Word文档下载推荐.docx(34页珍藏版)》请在冰豆网上搜索。

PDTR&

DRepresentative>

2

ProjectManager>

3

Teammembers>

4

CustomerRepresentative>

5

Others>

目录TableofContents

表目录ListofTables

图目录ListofFigures

关键词Keywords:

EPLD,Altera,EPM3256AQC208

摘要Abstract:

本文档详细描述了CN21SBUA单板逻辑的功能实现。

缩略语清单Listofabbreviations:

Abbreviations缩略语

Fullspelling英文全名

Chineseexplanation中文解释

UniversalServicePlatform

通用业务平台

ATCA

AdvancedTelecomComputingArchitecture

先进的电信计算结构

1

Introduction简介

1.1Purpose目的

本文档是USP平台CN21SBUA单板逻辑(位置号U41)的详细设计。

适用单板CN21SBUA.A。

2各模块详细设计方案

逻辑选型是42010084:

:

Altera的EPM3256208-10。

逻辑主要实现以下功能:

1、看门狗WDT2#(ADM706)接口电路。

逻辑外挂一片ADM706用于监控BMC,实现WDT2#的功能。

上电后,BMC必须定时通过逻辑清这片ADM706,否则会被复位,同时关断2条IPMI通路。

2、电源上电控制

根据E7501芯片组的要求,逻辑根据各个电源的pwrok信号作上电时序控制。

3、BMC扩展GPIO控制,BMC外挂FLASH译码等。

由于BMC的GPIO管脚数量不够使用,而且BMC的GPIO驱动能力较弱,同时可靠性要求部分控制信号被锁存,保证BMC运行过程中复位或失效不会影响到Xeon小系统,因此逻辑的部分管脚作为BMC的扩展GPIO,受BMC的控制。

BMC外挂一片FLASH,BMC对FLASH的操作通过逻辑译码来完成。

4、同时逻辑完成其它一些零碎的控制功能。

单板逻辑功能框图如图所示:

图1单板逻辑功能框图

由于逻辑是由STANDBY的3.3V供电,上电最早,下电最迟,因此逻辑设计中需要避免闩锁的影响。

2.1逻辑管脚分配

逻辑管脚分配如下:

表1逻辑管脚分配

编号

网络号

I/O特性

说明

PWRON_FCP

O

该信号控制FCP的3.3V(FCPIO电源)和Core电源的使能信号,高有效:

当PWRGOOD_VDD2V5和PWRGOOD_VDD1V8都有效时,PWRON_FCP就变为有效;

(因为1.8V有效就表示3.3V也有效)

EPLD上电复位时,该管脚初始化为‘0’。

P64H2_2_PWROK

(到硬盘扣板)

输出到P64H2_2的PWROK管脚的PWROK信号。

当P64H2_0_PWROK和SCSI_PWROK都为‘1’时,该信号为‘1’,否则为‘0’。

P64H2_1_PWROK

(到后插板)

P64H2_1的PWROK管脚输入信号。

当P64H2_0_PWROK和RTM_PWROK都为‘1’时,该信号为‘1’,否则为‘0’。

82546_0_B_SIGDET

保留。

输出3态。

82546_2_A_SIGDET

6

82546_2_B_SIGDET

7

82546_PWR_GD

82546的PWROK信号。

如果PWRGOOD_VDD1V5、PWRGOOD_VDD1V8、PWRGOOD_VDD2V5都为‘1’,那么82546_PWR_GD为‘1’,否则为‘0’。

8

ADM708_PFO_

I

9

ADM708_RST_

EPLD上电复位信号。

由ADM708上电时输入,保证EPLD可靠复位。

10

BMC_A[16:

23]

BMC地址总线

11

BMC_AD[0:

15]

BI

BMC数据总线

12

BMC_AH_

H2168控制信号

13

BMC_AS_

14

BMC_COM1_TXD

接BMC的发端

15

BMC_COM1_RXD

接BMC的收端

16

SIO_COM1_TXD

接LPC47S422发端

17

接LPC47S422收

18

E_COM1_TXD

逻辑串口发端。

19

E_COM1_RXD

逻辑串口收端。

串口的MUX选择关系由BMC控制。

20

BMC_CPCS1_

H2168输出片选

21

BMC_CS256_

H2168输出片选(保留)

22

BMC_ETRST_

送给BMC的JTAG接口的TRST_信号。

低有效。

当HUDI_ETRST_为‘0’、或BMC_RESET_为‘0’时,该信号就为‘0’;

只有HUDI_ETRST_和BMC_RESET_都为‘1’时,该信号才为‘1’。

23

BMC_FWE

BMC写控制信号

24

BMC_F_A[8:

Flash地址总线

25

BMC_F_CS_

BMC外挂的Flash片选信号。

26

BMC_HWR_

BMC读写控制信号

27

BMC_MD[0:

1]

BMC模式输入。

28

BMC_MODE_SEL

BMC模式选择,由跳线控制。

默认为‘1’,即没有上跳线帽。

29

BMC_PFSEL

30

BMC_PWROK_

BMC输出到EPLD的PWROK_信号,经过EPLD送到ICH3的PWROK#管脚。

和面板上的RESET按钮所起作用相同。

(不可靠)

31

BMC_RD_

BMC读信号

32

BMC_RESO_

BMC输出的复位信号,可以用于复位Xeon。

调试阶段保留。

33

B_FC_OUTEN

BMC使能FCP的FC通道0/1输出到背板。

高有效。

另外如果P64H2_0_PWROK为低,那么该信号也必须为低,考虑到防止闩锁。

34

DBR_RESET#

CPU的ITP测试接口引入的复位信号,备用。

35

EPLD_ADM706_MR_

36

EPLD_ADM706_RST_

37

EPLD_ADM706_WDI

38

EPLD_ADM706_WDO_

39

EPLD_CLK

EPLD输入时钟信号。

33MHz,备用。

40

EPLD_GOE

41

EPLD_TCK/EPLD_TDI

EPLD_TDO/EPLD_TMS

JTAG

42

EPLD_P1_SKTOCC#

CPU1在位信号

‘1’表示CPU1不在位,‘0’表示CPU1在位

43

44

FCP_GPIO_IN_ON_

BMC允许后插板信号输入到FCP的GPIO,通过16244隔断。

EPLD上电复位时,该管脚初始化为'

1'

。

45

FCP_GPIO_OUT_ON_

BMC允许FCP的GPIO输出到后插板,通过16244隔断。

46

FC_MUX

‘1’选择从背板输入的FC通道连接到FCP;

‘0’选择从后插板输入的FC通道连接到FCP。

47

FRONT_RST_

面板复位按钮输入。

低有效

48

FWH0_ID0

BMC控制,输出到FWH0的ID0管脚。

调试阶段设为“0”。

49

FWH1_ID0

BMC控制,输出到FWH1的ID0管脚。

和FWH0_ID0反相。

调试阶段设为“1”。

51

HUDI_ETRST_

HUDI仿真插座引入的对BMC的JTAG接口的TRST_管脚的复位信号。

52

HUDI_RST_O_

HUDI仿真插座引入的对BMC复位的信号。

53

ICH3_EPLD_GPIO[0:

3]

保留

54

ICH3_LED_HEALTHY0_

ICH3输出的HEALTHY灯驱动信号0。

55

ICH3_LED_HEALTHY1_

ICH3输出的HEALTHY灯驱动信号1。

56

ICH3_LED_OOS_

ICH3输出的OOS灯驱动信号。

‘1’灭,‘0’亮。

57

ISOLATE_IPMB0

控制IPMB0与背板之间的buffer是否关断。

当WDT2#溢出时关断buffer,直至BMC重新正常对WDT2#清狗。

“0”表示关断,“1”表示开通。

58

ISOLATE_IPMB1

控制IPMB1与背板之间的buffer是否关断。

59

LED_BLUE_

前面板蓝灯控制信号。

“1”灭,“0”亮。

60

LED_DEBUG[0:

1]_

逻辑测试指示灯。

默认输出为‘0’,点亮LED。

61

62

LED_DIMM[0:

3]_ERR

DIMM错误信号,由BMC检测。

63

LED_HEALTHY0_

面板HEALTHY灯的驱动信号(红色)。

由ICH3和BMC共同控制。

‘0’亮,‘1’灭。

64

LED_HEALTHY1_

面板HEALTHY灯的驱动信号(绿色)。

65

LED_OOS0_

面板OOSLED(黄色,欧洲模式)的驱动信号。

66

LED_OOS1_

面板OOSLED(红色,北美模式)的驱动信号。

67

LED_PWRGD_

备用。

68

LED_PWROK_

单板电源(除VRD)输出状态指示灯,只有PWRGOOD_DC、PWRGOOD_VDD1V2、PWRGOOD_VDD1V5、PWRGOOD_VDD1V8、PWRGOOD_VDD2V5都为‘1’,该信号才为‘0’,点亮指示灯,否则为‘1’;

“亮”表示电源正常,“灭”表示电源未正常工作

69

LED_VRD_PWROK_

VRD电源输出状态指示灯,PWRGOOD_VRD为‘1’,则该信号为‘0’,点亮指示灯,否则为‘1’;

“亮”表示VRD电源正常,“灭”表示VRD电源未正常工作;

70

LM80A_INT_

LM80送过来的中断。

71

MCH_HI_VDD1V2_ON

BMC控制MCH的HI接口参考电压1.2V上电。

‘0’不上电。

是默认状态。

‘1’上电。

BMC允许后插板上电工作时,BMC置该信号为‘1’。

但是BMC必须在后插板送过来的“RTM_PWROK”变为高以后,才可以置MCH_HI_VDD1V2_ON信号为‘1’。

72

P64H2_0_PCIRST_

ICH3输入的复位信号。

73

PON_VDD3V3

当SLP_S5_为高时,该信号为‘1’,否则为‘0’。

74

PON_VDD12V

75

ICH3_VRDPWRGD_

输出给ICH3的VRDPwrgood信号。

CK408_V18_PWRGD_

不处理,高阻输出。

CK408_PWRGD_

76

PWRGOOD_DC

二次电源模块(-48V/12V,-48V/3.3V,12V/5V)的POWERGOOD信号。

高有效

77

PWRGOOD_VDD1V2

3.3V-→1.2V电源的POWERGOOD信号

78

PWRGOOD_VDD1V5

3.3V-→1.5V电源的POWERGOOD信号

79

PWRGOOD_VDD1V8

3.3V-→1.8V电源的POWERGOOD信号

80

PWRGOOD_VDD2V5

DDR2.5V电源的POWERGOOD信号

81

PWRGOOD_VRD

VRD的POWERGOOD信号输入

82

E7501_PWROK,

ICH3_PWROK,

P64H2_0_PWROK

这3根信号是相同的处理。

1,PWRGOOD_DC、PWRGOOD_VDD1V2、PWRGOOD_VDD1V5、PWRGOOD_VDD1V8、PWRGOOD_VDD2V5都为‘1’以后,这3根信号同时为‘1’。

2,BMC可以置这些信号为‘0’,结果是ICH3复位单板(不包括BMC)。

BMC由此复位单板。

暂时保留。

3,FRONT_RST_(面板按钮)为‘0’时,这些信号为‘0’,结果是ICH3复位单板(不包括BMC)。

‘1’有效,‘0’表示单板上电还没有完成。

EPLD上电复位时,这3根信号初始化为'

0'

83

PWRON_VRD

VRD输出使能。

PWRGOOD_DC、PWRGOOD_VDD1V2、PWRGOOD_VDD1V5、PWRGOOD_VDD1V8、PWRGOOD_VDD2V5都有效以后才使能VRD。

OpenDrain输出,‘0’关断VRD,‘高阻’使能VRD

84

PWRON_VDD2V5

PWRON_VDD2V5(DDR上电)。

1.2V_PWR_GOOD信号为高时输出高阻,使能DDR电源;

1.2V_PWR_GOOD信号为低时输出‘0’,关断DDR电源;

85

PWR_BID[0:

3]

电源扣板的PCB_ID信息。

BMC读取。

86

RTM_BLUE_LED_

后插板BLUE灯控制信号。

‘0’表示亮,‘1’表示灭。

87

RTM_HEALTHY_G_

输出到后插板的HEALTHY(绿色)点灯信号。

88

RTM_HEALTHY_R_

输出到后插板的HEALTHY(红色)点灯信号。

89

RTM_OOSR_

输出到后插板得OOSLED(红色)点灯信号。

90

RTM_OOSY_

输出到后插板得OOSLED(黄色)点灯信号。

91

RTM_PCIRST_

后插板复位信号。

P64H2_0_PCIRST_和RTM_PWROK都为‘1’时才为‘1’,否则为‘0’。

EPLD上电复位时,该管脚初始化为‘0’

92

RTM_PWROK

后插板送过来、表示后插板上电完成的信号。

‘0’后插板没有上电,或没有完成上电。

‘1’后插板上电完成。

93

RTM_VBUS_ON

BMC控制后插板VBUS(+12V)电源ON/OFF。

后插板的2根“EN”都有效以后,该信号也有效。

‘1’表示ON,‘0’表示/OFF

94

RTM_VSB_ON

BMC控制后插板VSB电源ON/OFF。

95

R_FC_OUTEN

使能FCP的FC通道0/1输出到后插板。

96

SCSI_PCIRST_

硬盘扣板复位信号。

复制P64H2_0_PCIRST_输出。

97

THRMTRIP_LTCH

CPU温度过高时,THERM_EN有效,关断VRD电源。

98

BMC_708_RESET_

BMC的708输出的复位信号。

99

VDD_ID

当VDDID为低时,表示DIMM内存条的VDD和VDDQ不是同一电压,单板不能上电;

当VDDID为高时,表示DIMM内存条的VDD和VDDQ是同一电压,单板可以上电;

100

WDT3_DOG

BMC送过来的WDT3清狗信号。

101

SLP_S5_

ICH3送出的“睡眠状态”信号:

‘0’表示处于“睡眠状态”,也是单板上电时的初始状态。

此时信号PON_VDD3V3和PON_VDD12V输出为低;

主电源模块关断。

‘1’表示单板不再处于“睡眠状态”。

此时信号PON_VDD3V3和PON_VDD12V输出为高;

主电源模块使能输出电源。

SLP_S5_由‘0’到‘1’是通过输入到ICH3的ICH3_PWRBTN_来实现的。

102

DISK_PWROK

硬盘扣板输入的PWROK信号。

‘0’表示硬盘扣板没有上电完成,或没有上电;

‘1’表示硬盘扣板上电完成;

103

HIP6301_DPMODE

控制VRD电源的LoadLine。

‘1’表示Xeon1在位;

‘0’表示Xeon1不在位;

该信号是输入信号EPLD_P1_SKTOCC#的反相。

104

LM80A_INT_

SERVER板LM80输出的中断信号,BMC读取,保留。

105

ICH3_PWR_BTN_

EPLD上电复位时,该管脚置为‘0’。

以后由BMC控制。

默认为‘0’。

调试阶段不处理。

106

BMC_RESET_

EPLD输出给BMC的RES_管脚的复位信号。

当HUDI_RST_O_或BMC_708_RESET_有一个为‘0’时,该信号为‘0’;

同时关断连接CMM的2条I2C总线。

另外,如果EPLD外挂的706溢出,BMC_RESET_也输出为‘0’;

调试阶段此功能保留。

2.2ADM706接口

略。

2.3电源上电控制

根据E7501芯片组和ISP2312对上电顺序的要求,逻辑实现以下功能:

1、根据1.2V的pwrok信号,使能2.5V/1.25V的上电;

2、根据单板其它电源的pwrok,使能VRD上电;

3、根据3.3V、2.5V、1.5V的pwrok,使能ISP2312上电;

2.4BMC(H2168)接口

该模块主要实现和BMCH2168F器件)的逻辑的接口,逻辑提供相应的可以读写的寄存器。

H2168和逻辑的连接关系如图所示:

图2CPU和逻辑数据地址总线接口图

硬件上H2168和逻辑的连线包括的地址线A23~A16(高位地址),数据地址复用AD15~AD8,地址线AD7~AD0。

设计上选用H2168的“地址数据复用扩展模式”,访问空间为CS256片选对应的地址空间(0xF80000~0xFBFFFF),BMC软件设置8-bit寻址空间模式,这种情况AD15~AD8为数据地址复用,AD7~AD0以及A23~A16作为地址(用IO方式模拟);

H2168外部扩展的器件包括CPLD和FLASH,逻辑内部通过A23作为片选,A23=‘1’选中CPLD,A23=‘0’选中外扩FLASH。

读写信号为BMC_RD_/BMC_HWR_,片选信号采用Bmc_cs256_。

BMC读写时序如下图所示:

图3BMC存储器接口读写时序

CPLD内部用Bmc_ad[10:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- USPCNSBUA 逻辑 详细 设计 实施方案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx