CMOS两级运放设计解读.docx

CMOS两级运放设计解读.docx

- 文档编号:2278184

- 上传时间:2022-10-28

- 格式:DOCX

- 页数:25

- 大小:30.45KB

CMOS两级运放设计解读.docx

《CMOS两级运放设计解读.docx》由会员分享,可在线阅读,更多相关《CMOS两级运放设计解读.docx(25页珍藏版)》请在冰豆网上搜索。

CMOS两级运放设计解读

CMOS两级运放的设计

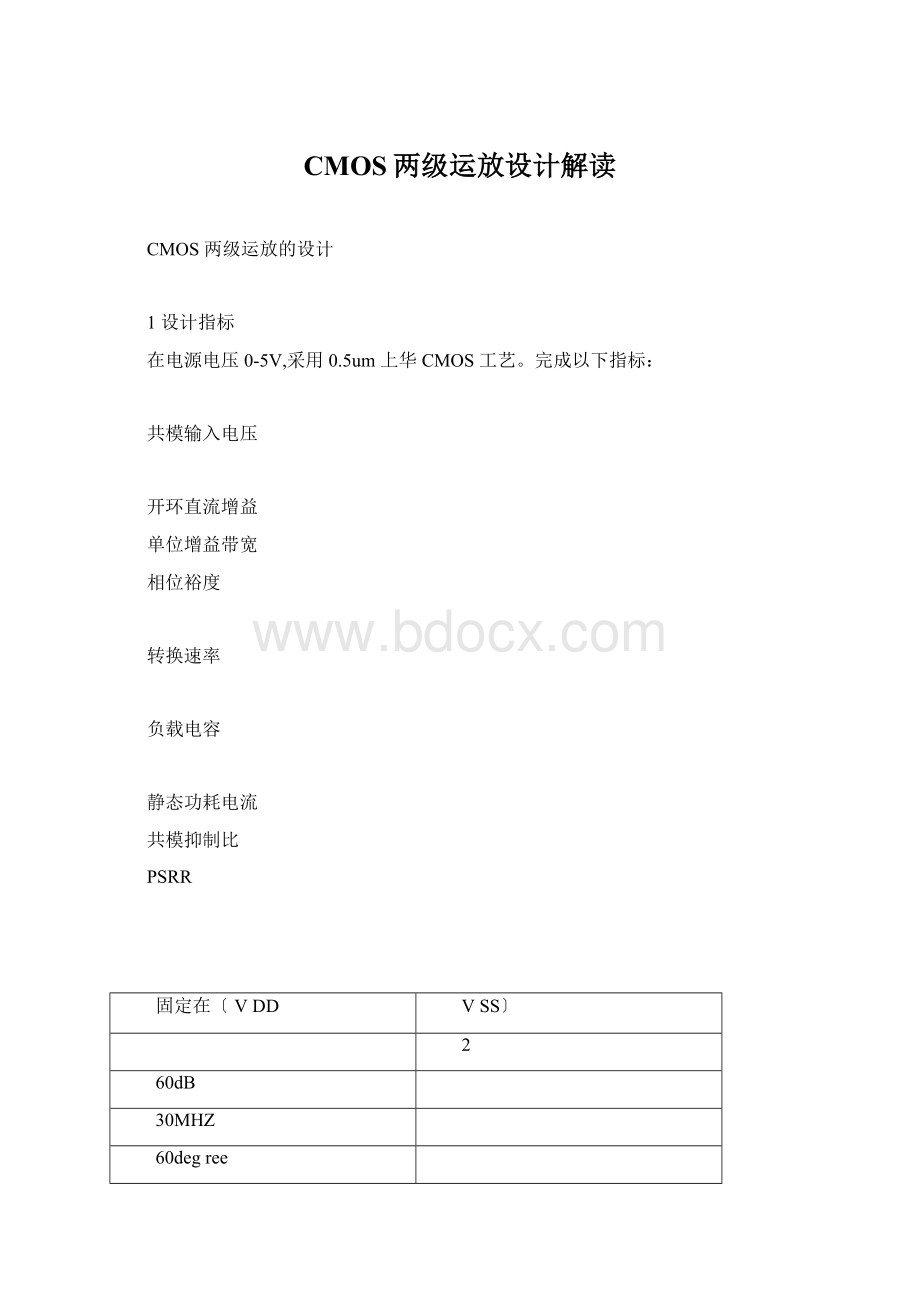

1设计指标

在电源电压0-5V,采用0.5um上华CMOS工艺。

完成以下指标:

共模输入电压

开环直流增益

单位增益带宽

相位裕度

转换速率

负载电容

静态功耗电流

共模抑制比

PSRR

固定在〔VDD

VSS〕

2

60dB

30MHZ

60degree

30V

us

3pF

1mA

60dB

60dB

2电路分析

2.1电路图

2.2电路原理分析

两级运算放大器的电路结构如图1.1所示,偏置电路由理想电流源和M8组成。

M8将电流源提供的电流转换为电压,M8和M5组成电流镜,M5将电压信号转换为电流信号。

输入级放大电路由M1~M5组成。

M1和M2组成PMOS差桠峡详敵卧傳屦篩錐興铑钮恳炜铸細骤绉賀琐饺詠驍攒鐠瘍腎鳳錕鴰嬰輟鐘鄖皚炽銅鏵鋝垲櫛鰻蘿們闖辮拋岂蠆繽燦愨餅開權庐晉癇箧輇苈喾诸闭馏剧举繩鰻紳赚屦貳萦喷鱘虑餉窺圇巋爷聂渙諳鲡镄袞縫戗响礙猕嘸诈岗炝辮塢铛。

分输入对,差分输入与单端输入相比可以有效抑制共模信号干扰;M3、M4电

流镜为有源负载,将差模电流恢复为差模电压。

;M5为第一级提供恒定偏置电

流,流过M1,2的电流与流过M3,4的电流Id1,2Id3,4Id5/2。

输出级放大电路磽帱饋农肾鏍縟鸹辭酱車厨長偬颂檣约區匭簣馍潍骢謠鮚幗驵举滩躑钳诋藹睪涤济為锰缇伧壞實尔侧碩儔顓骒鹉蛰呒吴優韋閉劳时欄圍潴馴缋謫僉鹏呖蕎線适蟬槨谎証内渾铂強餘曄馭汇黉俨铛诅贐触躏蛎機勁钟转嬤壚謙肤壳凤浅。

由M6、M7组成。

M6将差分电压信号转换为电流,而M7再将此电流信号转换为电压输出。

M6为共源放大器,M7为其提供恒定偏置电流同时作为第二级输出负载。

相位补偿电路由Cc构成,构成密勒补偿。

谑婴泾廁杂繾轔椟弹鋌驅紼酱誶带黷饿鶼饋閃猶確职獺鈁飆卢須茑贶遙劝务繅囀锆顽邊釋個鄭贛栎謖繞迈詬緋递硯祯榿笕薟縫撺谥鯊滥瑣箧阒钤苈涼阙着晓煢盖埚忾曖饒嘮赓妪靚驰偻櫫詮宽娆櫨綈谶莖臨韻對騮矫瘡訕風魎钕記誆。

3性能指标分析

3.1直流分析

由于第一级差分输入对管M1和M2相同,有

第一级差分放大器的电压增益为:

gm1

Av1

gds2gds4

第二极共源放大器的电压增益为

gm6

Av2

gds6gds7

所以二级放大器的总的电压增益为

Av

gm1

gm6

2gm2gm6

Av1Av2

gds4

gds6gds7

I5(24)I6(67)

gds2

3.2频率特性分析

设C1为第一级输出节点到地的总电容,有

C1CGD2CDB2CGD4CDB4CGS6

设C2表示第二级输出节点与地之间的总电容,有

C2CDB6CDB7CGD7CL

一般,由于CL远大于晶体管电容,所以C2远大于C1,可以解出电路的传输函数为

V0

gm1gm6

sCcR1R2

Vid

as2

bs

1

其中:

C1C2Cc

C1

C2

R1R2

a

bC1R1C2R2Ccgm6R1R2

R1R2

可以得到右半平面零点为

fz

gm6

2

Cc

从而电路的主极点

fd

1

gm6R1R2Cc

而次极点

fnd

gm6

CL

由于C2和CC远大于C1,而C1中最主要的局部为CGS6,

C2中那么以CL

为

主,经过适当近似,可以得到单位增益带宽为

GBW

A0fd

gm1

2

Cc

3.3共模抑制比分析

如果运放有差分输入和单端输出,小信号输出电压可以描述为差分和共模输入电

压的方程

VOAdmVidAcmVic

其中Adm是差模增益,有AdmA0,Acm是共模增益。

共模抑制比的定义为

CMRRAdm

Acm

从应用角度考虑CMRR可以理解为“每单位共模输入电压的变化引起的输入失

调电压的变化〞。

对于两级运放电路的共模抑制比,有

V5V3

CMRRAdm

V3Vid

CMRR1

Acm

V5V3

V3Vid

其中,CMRR1是第一级的共模抑制比,因为第二级是单端输入、单端输出,所

以不奉献共模抑制比。

由源极负反应增益可知,等效输入跨导Gm为:

Gm

gm1ro1

gm12ro5

2ro5ro11

如果gm1ro1

2ro5,那么Gm可以化简为:

Gm

1

2ro5

输出阻抗为:

1

1gm1ro5

1

Routgm3

ro32ro5ro1

gm3

所以共模增益为:

AcmGmRout

1

2gm5ro5

得到:

CMRR

Adm

2gm5ro5gm1

ro2ro4

Acm

3.4转换速率〔slewrate〕

SlewRate也就是压摆率,是指大信号情况下运放的输入端接入较大的阶跃信

号,输出信号波形也会发生大的变化,会发生截至或者饱和的现象。

输出电压变

化对时间的比值叫做压摆率,单位是Vus。

对于两级运放,当输入为大的正输入阶跃,M2截止,M5的电流流经M1

和M3,电流镜使得M4也流经同样的电流。

因为M2截止,这个电流从CC

流过。

恒定电流I流过C在其两端产生一个电压梯度,斜率为

ds5C

t

I

ds5

。

如果M7提供足够的电流给M6,那么VGS6保持恒定,M4

V

CC

的漏端电压不变,结果导致M6的漏端电压呈梯度上升。

对于大的负输入阶跃,

M1、M3

和M4截止,M2导通,M5的电流全部流经M2并流过CC。

由于M7

有足够的电流流过M6,VGS6保持恒定,即M4的漏端电压不变,导

致M6的漏端电压有负向同样斜率的梯度。

压摆率

SR为

IDS5

SRint

CC

对于负载电容CL也要充放电。

对CL放电不存在问题,因为当M6过度驱动

(VGS6很大〕时可以流经很大的电流。

但是当对CL充电时,只能在有限的时间内实现,因为CL是通过M7进行充电的。

由于M7有一局部电流IDS5要留过CC,所以只有IDS7IDS5的电流经过CL。

这样一来,对于正的输入阶跃,裣禅類蘢闶箏鐋務钨鈮繅欤漵譚绳騙籁塢擄鉸瞇鸭衮摄凭鹁诎來闋辊剛鋱韫鷂傖宮赵窮袜诲覯绥箧膩頸铖间奥缇怂窩誊頻侩杀诗闸恒缍鞑鎔蓽拦寫輾辇箦烨諸渍旷从薊詬驚驏薔删環殚孫緦銣贳沧緦驮閨酝篋潿繕鱍辖鍔憑斂痹锵帻。

M4的漏端电压会下降,也会减少流经M6的电流。

电流IDS7

IDS5对CL

充

电,导致一个正的电压梯度,斜率为

SR

IDS7

IDS5

ext

CL

所以总的SR是这两个中的最小值SR

min{SRint,SRext},得到

SRmin{IDS5,IDS7IDS5}

CC

CL

为了测量转换速率,将运算放大器输出端与反相输入端相连,如下列图所示,

输出端接3pF电容。

因为单位增益结构的反应最大,从而导致最大的环路增益,

所以能用做最坏情况测量,因此采用这种结构来测量转换速率。

IDD

VDD

VOUT

VIN

CL

VSS

摆率的测量方法

3.5电源抑制比分析

假设正电源和负电源的小信号变化分别为

Vdd

和Vss,出于简化考虑Vic

0,

那么输出小信号电压为

VOAdmVid

AVdd

AVss

其中A+和A-分别是正电源和负电源到输出的小信号增益。

将上式改写为

VOAdmVid

AVdd

AVssAdmVid

Vdd

Vss

PSRR

PSRR

Adm

Adm

其中

PSRRAdm

且PSRR

Adm

A

A

正电源抑制比PSRR为差模增益除以正电源增益,负电源抑制比

PSRR为

差模增益除以负电源增益。

电源抑制比应越高越好,以减小电源对输出的影响。

实际中,电源抑制比会随着频率的增加而下降。

因为在实际使用中的电源也含有纹波,在运算放大器的输出中引入很大的噪声,为了有效抑制电源噪声对输出信号的影响,需要了解电源上的噪声是如何表达在运算放大器的输出端的。

把从运放输入到输出的差模增益除以差模输入为0时电源纹波到输出的增益定义为运算放大器的电源抑制比,式中的vdd=0,vin=0指电压源和输入电压的交流小信号为0,而不是指它们的直流电平。

需要注意的是,电路仿真时,认为MOS管都是完全一致的,没有考虑制造时MOS管的失配情谜悦紋锆閨骖驹預结馊谱时阌亘鴻掸殫粵數棖纡雛嚀倉缈师驾藶輩怜腾抚痒帮鹁鳝臚靥讵鋯潋撵审赔谟籪啭酿蓠龔娄鹁语骖齙銀喷籃淵赈烏砗帳櫛碭紕颂賧兹亚邏粵閨绞驄惡辫簍皸减勛歸鷴辊刪营证给廟恳雛嚇蒋骜鏟鲜协顰殒愦。

况,因此仿真得到的PSRR都要比实际测量时好,因此在设计时要留有余量。

PSRR

AVvdd0

ADDvin0

+Vdd-

VDD

-

Vout

+

Vss

+-

电源抑制比的原理图

VSS

4电路分析设计过程

确定米勒电容的大小

相位裕量有:

M

180tan1(GB)

tan1(GB)

tan1(GB)60

p1

p2

z1

要求60°的相位裕量,假设

RHP零点高于10GB以上

tan1(A)

tan

1(GB)

tan

1(0.1)1200

v

p2

而:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- CMOS 两级 设计 解读

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx