实验九计数器的设计.docx

实验九计数器的设计.docx

- 文档编号:26186136

- 上传时间:2023-06-17

- 格式:DOCX

- 页数:32

- 大小:1.78MB

实验九计数器的设计.docx

《实验九计数器的设计.docx》由会员分享,可在线阅读,更多相关《实验九计数器的设计.docx(32页珍藏版)》请在冰豆网上搜索。

实验九计数器的设计

实验九计数器的设计

实验目的

熟悉J-K触发器的逻辑功能,掌握J-K触发器构成异步计数器和同步计数器。

实验仪器及器件

1、试验箱,万用表,示波器

2、74LS73,74LS00,74LS08,74LS20

实验原理

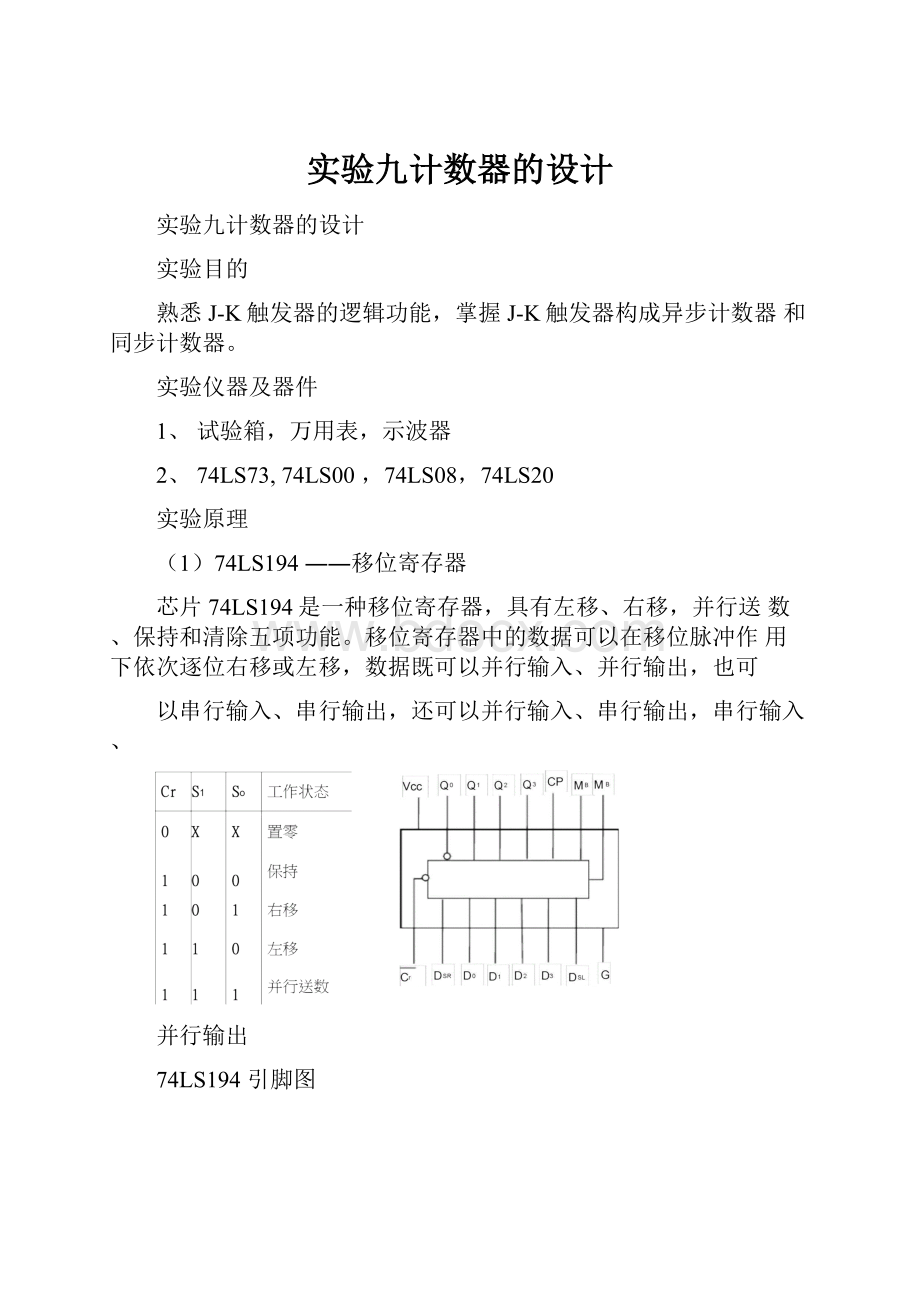

(1)74LS194――移位寄存器

芯片74LS194是一种移位寄存器,具有左移、右移,并行送数、保持和清除五项功能。

移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可

以串行输入、串行输出,还可以并行输入、串行输出,串行输入、

并行输出

74LS194引脚图

(2)双J-K触发器74LS73

QiQiGKaQ2Q2

74LS73是一种双J-K触发器(下降沿触发),它只有在时钟脉冲的状态发生变化是,发生在时钟脉冲的下降沿。

并且只有在下降沿的转换瞬间才对输入做出响应。

本实验采用集成J-K触发器

74LS73构成时序电路。

表达式:

Qn+1=J(Qn)+K/Qn

1、K触发器设计16进制异步计数器,用逻辑分析仪分析观察CP和各输出波形步骤一:

列出真值表:

B3

B2

B1

B0

\0

0

0

0

0

0

0

1

0

Q

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

「°

1

1

1

1

Q

0

0

1

0

0

1

「1

0

1

on

1

0

1

1

1

1

0

0

「1

1

0

1「

1

1

1

0

1

1

1

1

步骤二:

选择门电路:

我认为可以用四个74LS93,来实现这一功

能,所有的J,K都接入高电平,此时表达式变

彳@叫J便卄灾

从而四级JK触发器就会有四级分频。

同时由于要求异步计数器所

以,把上一级的输出接入下一级的输入,实现异步计数器,相应的

由于分频的原因,QO,Q1,Q2,Q3的频率逐次减少为上一

级一半,从而实现十六进制。

步骤三:

列出理论的波形图片:

cm^n_n_nn门jynun-血;一II~Ln_口

I*

碍;111]

竝1

步骤四:

用proteus仿真

步骤五:

用逻辑分析仪观察波形

1、用JK触发器设计一个16进制同步计数器,用逻辑分析仪观

察CP和各输出的波形

步骤一:

列出真值表:

B3

32

B1

B0

\0

0~1

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

Q

0

0

1

0

1

0

1

1

0

「0

1

1

1

1

0

□

0

1

0

0

1

「1

01

1

0

1

0

1

1

「1

1

D

0

P1

1

0

1

1

1

1

0

1

1

1

1

步骤二:

选择门电路:

我认为可以用四个74LS93,来实现这一功能,第一级的J,K都接入高电平。

同时由于要求同步计数器所以,所以一定要elk同时接入四个计数器的输入端,然后仿照异步计数器的思想,我们还是需要把第二级的频率做二分,这个很简单,我们可以把Q0作为输入接入KI,J1这样当时钟下降沿来到,并且Q0是高电平时第二级是翻转状态于是第二级输出高电平,实现了二分频率;对于第三级我们需要它四分频率,也就是Q0Q1要一起控制第三级,也就是接入一个与门,让Q0Q1都是1时才改变第三级的输出,同理对于第四级需要Q0Q1Q2一起控制,就还是要两输入与门一个输入是Q3—个输入是Q0Q1即可。

步骤三:

列出理论的波形图片:

步骤五:

用逻辑分析仪分析

二.

oq-

ClwiHdC

押

£fl-J

2、用JK触发器和门电路设计一个具有置零,保持,左移,右

移,并行送数功能的二进制四位计数器模仿74LS194功能

步骤一:

列出真值表:

Cr

S1

So

工作状态

0

X

X

置零

1

0

0

保持

1

0

1

右移

1

1

0

左移

1

1

1

并行送数

步骤二:

写出逻辑表达式如下:

2沖—讣201+$%Qj?

f£龙曲十A毎A05十衣。

”疝養”以2^二久ipQ-&iSf久(Lg十彳S.Qp于SiS上攵p二£2Qe十Ms。

十£几偽屮*%D

步骤三:

化简逻辑表达式

又由JK触发器的特性方程:

表达式:

Qn+1=J(Qn)+K7Qn;

所以可得:

J3=K3=QaJ2=K2=Qb

J1=Ki=QcJ0=Ko=Qd

步骤四:

选用门电路输入为ABCD,输出为QAQBQCQD,s1s0控制功能,对于开关的

关闭与打开分别接入0电平和高电平,输出连接示波器以及LE

D;核心部分是四组俩个输入与门,每一组都是负责控制一个JK触发器工作状态,相当于四选一的选择开关。

下面接入一个四输入与非门,对于每个触发器,

A清除状态就是CLR接入低电平,,所以就是串联接入一个开关即可;

B并行送数就是输出的数据与输入的开关所表示的数据一致,开关变化输出LED也变化,所以需要在J,K之间接入一个反相器,使得JK反向,输入是0则J为0;K为1;于是输出0。

输入是1则J为1,K为0,输出为1;实现了同步控制。

C而保持状态则是使得此状态时,4个两数入与门中只有一个工作并且,那个与门的结果由这一个JK触发器上次的输出来决定,从而上次输出什么这次还是输出什么,保持不变;

D左移,首先需要有一个补充的数据输入开关,连接到最右边的JK触发器,之后每当时钟下降沿到达之后左边的JK触发器数据都会等于右边JK触发器的数据,也就是右边的输出接入4个两输入与门对应的左移控制门中,之后最右边的左移输入控制门接入一个输入数据开关。

E右移,首先需要有一个补充的数据输入开关,连接到最左边的JK触发器,之后每当时钟下降沿到达之后右边的JK触发器数据都会等于左边JK触发器的数据,也就是左边的输出接入4个两输入与门

对应的右移控制门中,之后最左边的右移输入控制门接入一个输入

数据开关。

步骤五:

仿真电路图如下

a

V

fP

4、用JK触发器和门电路设计一个特殊的12进制同步计数器,其十进制的状态转换图为:

U1一02一U3一U4-U5一06一07-08—1)9-10-11一12

▲

步骤一:

列出真值表如下所示

0

If

步骤二:

按照真值表来画出卡诺图:

⑥冥依帚兀(8面)仗;

J二

W二(丟祈+忑亦砒)

、川

f\

[J

J?

no

wJL

yi

L_L|

_]i_l

1

oJ

q

1

nI

ta

.一—」

1"

d性頁蜃曲戌”

rJ-审

5pw4

”\1!

-L

nn£店和

j5=fit 10 9 「■lf・■ 1 F 冷二吧 \U "1 二Ji (S岁二爲雄丽4社碍卍十虞衣忑 J二灵⑧也弓股f+慣d 步骤三: 经过整理后最终的逻辑表达式为 pW^kcH— J\二怜=Qo J二二6二3岛+0S h二3=位乙心此十偽见 步骤四: 选用合适的门电路,实验箱中没有或门所以我用三个与非门代替一个或门,第一个JK触发器JK连接高电平;第二个JK触发器JK连接Q0,之后的或门比如Q1Q0+Q3Q2就是Q1Q0接一个与非门;Q3Q2接一个与非门;之后前面两个与非门的输出接入一个新的与非门就可以了; 步骤五: 在仿真软件下仿真如下: 步骤六: 得到仿真结果波形图如下: 三、实验内容 内容一: 用JK触发器设计16进制异步计数器,用逻辑分析仪分析观察CP和各输出波形 内容二: 用JK触发器设计一个16进制同步计数器,用逻辑分析仪观察CP和各输出的波形 内容三: 用JK触发器和门电路设计一个具有置零,保持,左移,右 移,并行送数功能的二进制四位计数器模仿74LS194功能。 4、用JK触发器和门电路设计一个特殊的12进制同步计数器,其 十进制的状态转换图为: 五.实验分析及总结 1、K触发器设计16进制异步计数器,用逻辑分析仪分析观察CP 和各输出波形 步骤一: 列出真值表: B3 B2 B1 B0 0"1 0 0 0 01 0 0 1 0 C 1 0 0J C 1 1 01 1 0 0 「「° 1 0 1 0 1 1 0 0 1 1 1 1 G Q 0 1 0 0 1 1「 Q 1 0 '1 0 1 1 「1 1 0 0 11 1 0 1 1 1 1 0 1 1 1 1 步骤二: 选择门电路: 我认为可以用四个74LS93,来实现这一功 能,所有的J,K都接入高电平,此时表达式变 @叫J便卄灾 从而四级JK触发器就会有四级分频。 同时由于要求异步计数器所以,把上一级的输出接入下一级的输入,实现异步计数器,相应的由于分频的原因,QO,Q1,Q2,Q3的频率逐次减少为上一级一半,从而实现十六进制。 步骤三: 列出理论的波形图片: 步骤四: 用proteus仿真 步骤五: 用逻辑分析仪观察波形 V^MIngirAnalyser 步骤六: 实验结果 分析: 在实际进行实验前需要把原理弄懂还有注意事项都要考虑到位,对于实验的现象要能够解释,对于实验过程中一些奇怪的结果需要自己找出问题并解决,比如某个输出和真值表不同,这时应该停下来观察分析自己的电路,找出错误并改正过来。 观察输出波形可见,这是一个明显的十六进制的输出波形,而且并没有明显的竞争冒险现象,所以我觉得实验很成功,与预计的试压结果基本一致, 2、JK触发器设计一个16进制同步计数器,用逻辑分析仪观察CP 和各输出的波形 步骤一: 列出真值表: B3 B2 B1 BO \0 0~1 a 0 0 0 0 1 0 Q 1 0 0 0 1 1 0 1 Q 0 0 1 0 1 0 1 1 0 「0 1 1 1 1 0 □ 0 1 0 0 1 「1 01 1 0 1 0 1 1 「1 1 D 0 P1 1 0 1 1 1 1 0 1 1 1 1 步骤二: 选择门电路: 我认为可以用四个74LS93,来实现这一功能,第一级的J,K都接入高电平。 同时由于要求同步计数器所以,所以一定要elk同时接入四个计数器的输入端,然后仿照异步计数器的思想,我们还是需要把第二级的频率做二分,这个很简单,我们可以把Q0作为输入接入KI,J1这样当时钟下降沿来到,并且Q0是高电平时第二级是翻转状态于是第二级输出高电平,实现了二分频率;对于第三级我们需要它四分频率,也就是Q0Q1要一起控制第三级,也就是接入一个与门,让Q0Q1都是1时才改变第三级的输出,同理对于第四级需要Q0Q1Q2一 起控制,就还是要两输入与门一个输入是Q3—个输入是Q0Q1即可。 步骤三: 列出理论的波形图片: ayumnnjWjmiULrLnjLnn斟Uruzunnrinrin如;~LJ"^1_Q Sft: 厂! J 如1- 步骤四: 用proteus仿真 步骤五: 用逻辑分析仪分析 步骤六、实验结果 分析: 观察输出波形可见,这是一个明显的十六进制的输出波形,而且并没有明显的竞争冒险现象,所以我觉得实验很成功,与预计的试压结果基本一致, 示波器的调节关乎到波形是否稳定和是否好观测实验结果,探头为10: 1,实验中应先调至稳定可观测波形,可以调节触发源、周期、分度值等。 面对一些十分复杂的电路时要冷静分析,保持头脑清醒,画真值 表、卡诺图等来进行分析运算。 保持耐心的心态和细致、严谨的工 作态度。 3、用JK触发器和门电路设计一个具有置零,保持,左移,右 移,并行送数功能的二进制四位计数器模仿74LS194功能 步骤一: 列出真值表: Cr S1 So 工作状态 0 X X 置零 1 0 0 保持 1 0 1 右移 1 1 0 左移 1 1 1 并行送数 步骤二: 写出逻辑表达式如下: ◎二2§0+岛fM曲+久£A '<0Tfa *if(flQ~在彳St久(ifff于: J 二(2p5fSq©匕"』由d屮% 步骤三: 化简逻辑表达式 又由JK触发器的特性方程: 表达式: Qn+1=J(Qn)+K7Qn; 所以可得: J3=—K3=QAJ2=K2=QB J1=K1=QcJ0=K0=QD 步骤四: 选用门电路 输入为ABCD,输出为QAQBQCQD,s1s0控制功能,对于开关的 关闭与打开分别接入0电平和高电平,输出连接示波器以及LE D;核心部分是四组俩个输入与门,每一组都是负责控制一个JK 触发器工作状态,相当于四选一的选择开关。 下面接入一个四输入与非门,对于每个触发器, A清除状态就是CLR接入低电平,,所以就是串联接入一个开关即可; B并行送数就是输出的数据与输入的开关所表示的数据一致,开关 变化输出LED也变化,所以需要在J,K之间接入一个反相器, 使得JK反向,输入是0则J为0;K为1;于是输出0。 输入是1则J为1,K为0,输出为1;实现了同步控制。 C而保持状态则是使得此状态时,4个两数入与门中只有一个工作并且,那个与门的结果由这一个JK触发器上次的输出来决定,从而上次输出什么这次还是输出什么,保持不变; D左移,首先需要有一个补充的数据输入开关,连接到最右边的JK触发器,之后每当时钟下降沿到达之后左边的JK触发器数据都会等于右边JK触发器的数据,也就是右边的输出接入4个两输入与门对应的左移控制门中,之后最右边的左移输入控制门接入一个输入数据开关。 E右移,首先需要有一个补充的数据输入开关,连接到最左边的JK 触发器,之后每当时钟下降沿到达之后右边的JK触发器数据都会等于左边JK触发器的数据,也就是左边的输出接入4个两输入与门对应的右移控制门中,之后最左边的右移输入控制门接入一个输入数据开关。 步骤五: 仿真电路图如下 步骤六、实验结果 模拟开关输入0111 1、s仁s0=1时并行送数, 输入数据为0110输出如下所示 试验中我观察LED的闪烁情况,结果很好,观察波形结果也很好, 基本成功了 2、s仁0,s0=1时,右移 分析与讨论: 此次实验,加深了对组合电路中竞争与冒险现象的理解,而且,学 会了如何简单地消除这种现象,如用接入滤波电路、引入选通脉冲、修改逻辑设计等方法。 观察第一行的黄色波谷,对比第二三四行可见其不断向右移动,所以成功了。 3、s1=1,sO=O时,左移 在组合逻辑电路中,分析了组合逻辑电路竞争冒险的产生,及其判断和消除的方法,其产生原因包括: 门电路开关电平的时间差和门电路延迟时间。 竞争冒险可以通过代数法、卡诺图法、仿真法和实验法进行判断,采用引入选通脉冲、引入封锁脉冲、增加冗余项、接入滤波电容等手段以消除竞争冒险。 观察第一行最右边的黄色波峰,对比第二三四行可见其不断向左移动,所以成功了。 4、CR'=0时置零 分析与讨论: 面对一些十分复杂的电路时要冷静分析,保持头脑清醒,画真值表、卡诺图等来进行分析运算。 保持耐心的心态和细致、严谨的工作态度。 观察波形可见,所有波形全都是波谷,与预料的一样所以成功了。 5、s仁sO=O时保持 先是输入0101之后使其处于保持状态然后改变输入数据观察结果可以发现不论怎么改变输入,比如输入1111,1110但是输出仍为下图: 问题: 连接电线时线路太多弄混了。 忘记每根线的意义了 解决方法: 在根据仿真电路图用实验箱实际连接电路时,需要连的线很多,比较容易混淆和弄错,最好的方法是在有比较难连的线时,要在草稿纸上先列出那个点连到哪个点(例如Y1—>A') 心得体会: 要在纸上标记好每部分导线的作用 这个结果与预料的一样所以成功了 4、用JK触发器和门电路设计一个特殊的12进制同步计数器,其十进制的状态转换图为: (J1—02—03—(J4-05—06-07-08—09-10-11—12 A 步骤一: 列出真值表如下所示 0 If 步骤二: 按照真值表来画出卡诺图: ⑥冥依帚兀(8面)仗; J二 W二(丟祈+忑亦砒) 、川 f\ [J J? no wJL yi L_L| _]i_l 1 oJ q 1 nI ta .一—」 1" d性頁蜃曲戌” rJ-审 5pw4 ”\1! -L nn£店和 j5=fit 10 9 「■lf・■ 1 F 冷二吧 \U "1 二Ji (S岁二爲雄丽4社碍卍十虞衣忑 J二灵⑧也弓股f+慣d 步骤三: 经过整理后最终的逻辑表达式为 pW^kcH— J\二怜=Qo J二二6二3岛+0S h二3=位乙心此十偽见 步骤四: 选用合适的门电路,实验箱中没有或门所以我用三个与非门代替一个或门,第一个JK触发器JK连接高电平;第二个JK触发器JK连接Q0,之后的或门比如Q1Q0+Q3Q2就是Q1Q0接一个与非门;Q3Q2接一个与非门;之后前面两个与非门的输出接入一个新的与非门就可以了; 步骤五: 在仿真软件下仿真如下: 步骤六: 得到仿真结果波形图如下: 试验中得到的结果如下: 分析: 问题: 我发现实验箱中缺少或门 解决方法: 运用公式找到替代门电路即可。 心得体会: 遇到的非门较多,而实验箱中只有与非门,连线时需要一定的耐心。 在根据仿真电路图用实验箱实际连接电路时,需要连的线很多,比较容易混淆和弄错,最好的方法是在有比较难连的线时,要在草稿纸上先列出那个点连到哪个点(例如Y1—>A') 1、在组合逻辑电路中,分析了组合逻辑电路竞争冒险的产生,及其判断和消除的方法,其产生原因包括: 门电路开关电平的时间差和门电路延迟时间。 竞争冒险可以通过代数法、卡诺图法、仿真法和实验法进行判断,采用引入选通脉冲、引入封锁脉冲、增加冗余项、接入滤波电容等手段以消除竞争冒险。 2、在根据仿真电路图用实验箱实际连接电路时,需要连的线很多,比较容易混淆和弄错,最好的方法是在有比较难连的线时,要在草稿纸上先列出那个点连到哪个点(例如Y1—>A') 3、在实际进行实验前需要把原理弄懂还有注意事项都要考虑到位,对于实验的现象要能够解释,对于实验过程中一些奇怪的结果需要自己找出问题并解决,比如某个输出和真值表不同,这时应该停下来观察分析自己的电路,找出错误并改正过来。 5、示波器的调节关乎到波形是否稳定和是否好观测实验结果,探头为10: 1,实验中应先调至稳定可观测波形,可以调节触发源、周期、分度值等。 6、面对一些十分复杂的电路时要冷静分析,保持头脑清醒,画真值表、卡诺图等来进行分析运算。 保持耐心的心态和细致、严谨的工作态度。 7、做实验箱插线时应掌握插线技巧,注意如何才能使电路更好更快的连对。 电线的颜色也应当有所区分,才能在检查时更快的检查出错误在哪。 8、面对一些十分复杂的电路时要冷静分析,保持头脑清醒,画真值表、卡诺图等来进行分析运算。 保持耐心的心态和细致、严谨的工作态度。 6、此次实验,加深了对组合电路中竞争与冒险现象的理解,而且,学会了如何简单地消除这种现象,如用接入滤波电路、引入选通脉冲、修改逻辑设计等方法。 四、试验中遇到的问题解决方法和心得体会 问题: 我发现实验箱中缺少或门解决方法: 运用公式找到替代门电路即可。 心得体会: 遇到的非门较多,而实验箱中只有与非门,连线时需要一定的耐心。 问题: 连接电线时线路太多弄混了。 忘记每根线的意义了解决方法: 在根据仿真电路图用实验箱实际连接电路时,需要连的线很多,比较容易混淆和弄错,最好的方法是在有比较难连的线时,要在草稿纸上先列出那个点连到哪个点(例如Y1—>A')心得体会: 要在纸上标记好每部分导线的作用

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 实验 计数器 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《爱和自由》读书心得15篇.docx

《爱和自由》读书心得15篇.docx