开放式CPU 运算器部件实验移位器.docx

开放式CPU 运算器部件实验移位器.docx

- 文档编号:28644437

- 上传时间:2023-07-19

- 格式:DOCX

- 页数:14

- 大小:35.84KB

开放式CPU 运算器部件实验移位器.docx

《开放式CPU 运算器部件实验移位器.docx》由会员分享,可在线阅读,更多相关《开放式CPU 运算器部件实验移位器.docx(14页珍藏版)》请在冰豆网上搜索。

开放式CPU运算器部件实验移位器

运算器部件实验移位器

一、实验目的

1、理解寄存器、移位器的原理。

2、掌握5种移位器及其用途。

二、实验原理

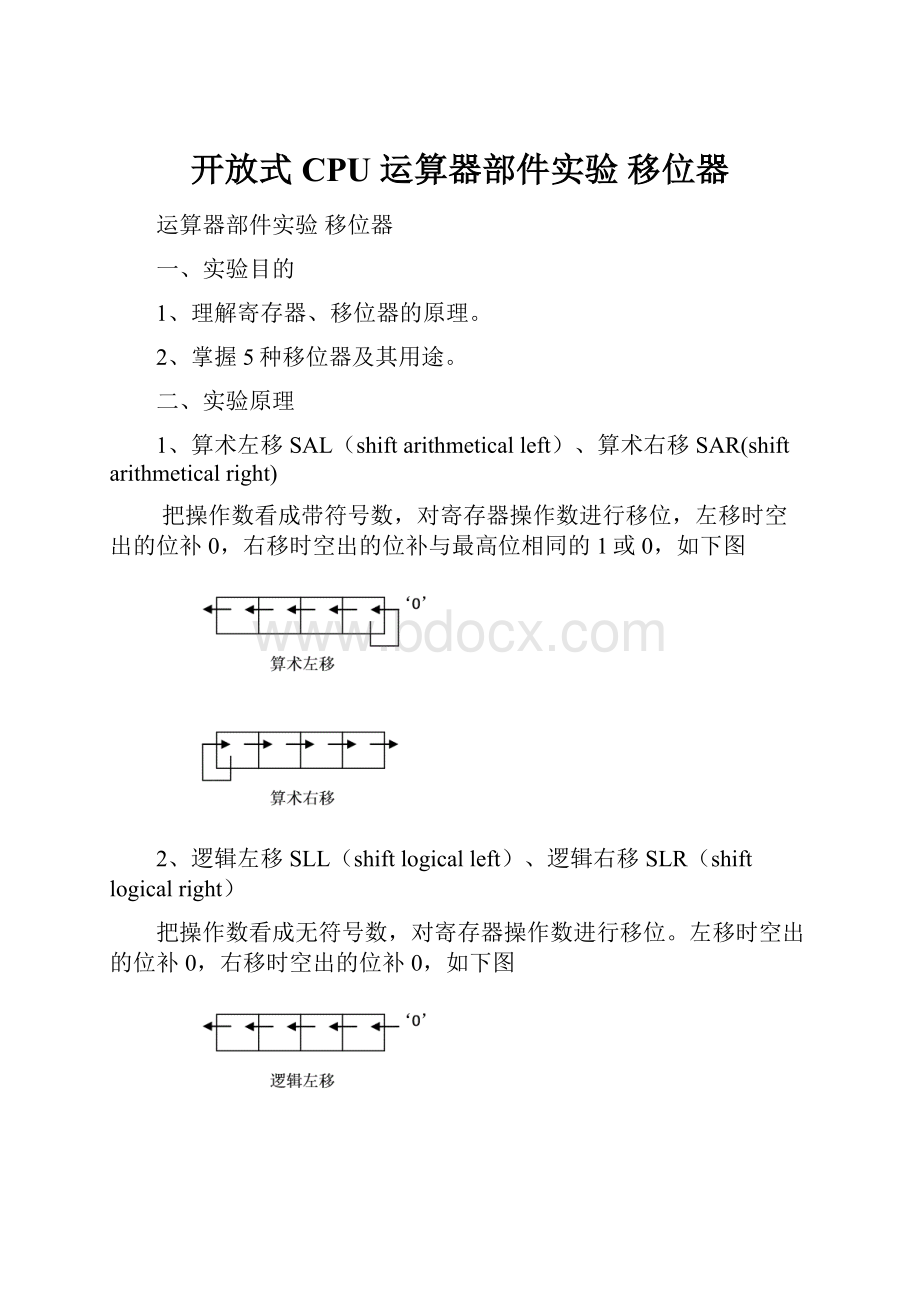

1、算术左移SAL(shiftarithmeticalleft)、算术右移SAR(shiftarithmeticalright)

把操作数看成带符号数,对寄存器操作数进行移位,左移时空出的位补0,右移时空出的位补与最高位相同的1或0,如下图

2、逻辑左移SLL(shiftlogicalleft)、逻辑右移SLR(shiftlogicalright)

把操作数看成无符号数,对寄存器操作数进行移位。

左移时空出的位补0,右移时空出的位补0,如下图

3、循环左移ROF(rotationleft)、循环右移ROR(rotationright)

循环左右移其实是一样的,比如说8位的操作数,左移n(0≤n≤8)位和右移n-8位结果是一样的。

左移时,移出的最高位移回到最低位;右移时,移出的最低位移回到最高位,如下图

三、实验步骤

1、打开QuartusⅡ,安装ByteBlasterⅡ。

2、将子板上的JTAG端口和PC机的并行口用下载电缆连接。

打开试验台电源。

3、执行Tools—Programmer命令,将shifter.sof下载到FPGA中。

4、在实验台上通过模式开关选择FPGA-CPU独立调试模式010。

四、输入输出规则

1、将开关CLKSEL拨到1,将短路子DZ3短接且短路子DZ4断开,使FPGA-CPU所需要的时钟使用正单脉冲时钟。

2、输入的8位操作数D7~D0对应开关SD15~SD8。

3、移动的位数n(3位数)对应开关SD7~SD5。

4、方向dir(左移还是右移)对应开关SD4,0代表左移,1代表右移。

5、移位类型kind(2位)对应开关SD3~SD2,00代表算数移,01代表逻辑移,10代表循环移。

6、在按下实验台上的单脉冲按钮后,对操作数移位的结果在灯A7~A0上体现。

五、实验结果

1.对8位数10110100进行移位操作,结果如下表1。

表1第一组数据:

10110110

操作

运算

n

dir

kind

移位结果

逻辑左移2位

010

0

01

11011000

逻辑右移5位

101

1

01

11111101

算术左移3位

011

0

00

1011000

算术右移4位

100

1

00

11111011

循环左移1位

001

0

10

01101101

循环右移7位

111

1

10

01101101

2.对8位数01001101进行移位操作,结果如下表2。

表2第二组数据:

01001101

操作

运算

n

dir

kind

移位结果

逻辑左移2位

010

0

01

00110100

逻辑右移5位

101

1

01

11111101

算术左移3位

011

0

00

01101000

算术右移4位

100

1

00

00000100

循环左移1位

001

0

10

10011010

循环右移7位

111

1

10

10011010

3.对8位数01010101进行移位操作,结果如下表3。

表3第三组数据:

01010101

操作

运算

n

dir

kind

移位结果

逻辑左移2位

010

0

01

01010100

逻辑右移5位

101

1

01

11111010

算术左移3位

011

0

00

10101000

算术右移4位

100

1

00

00000101

循环左移1位

001

0

10

10101010

循环右移7位

111

1

10

10101010

六、心得体会

通过这次实验初步对实验台布局有了大致了解。

又重新使用VHDL,在很多细节但很重要的方面摔倒、爬起,比如说信号量赋值是在进程结束后完成,但编程时却忘记这一规则,在进程内就使用了未完成赋值的信号量,结果出错。

另外,移位器编写时由于分类较多,只关注了case的各种情况,而忽略了时钟信号的使用,以至于调试时测试了很久都是在开关拨动时移位就开始了,而不等时钟信号的控制,这些都是粗心大意惹的祸,浪费了很多时间,以后倍加注意。

libraryieee;

useieee.std_logic_1164.all;

entitymoveis

port

(

clk:

instd_logic;

D:

instd_logic_vector(7downto0);

N:

instd_logic_vector(2downto0);

dir:

instd_logic;

kind:

instd_logic_vector(1downto0);

light:

outstd_logic_vector(7downto0)

);

endentity;

architecturertlofmoveis

begin

process(clk)

begin

if(clk'eventandclk='1')then

if(dir='0')then

if(kind="10")then

caseNis

when"001"=>

light(7downto1)<=D(6downto0);

light(0)<=D(7);

when"010"=>

light(7downto2)<=D(5downto0);

light

(1)<=D(7);

light(0)<=D(6);

when"011"=>

light(7downto3)<=D(4downto0);

light(2downto0)<=D(7downto5);

when"100"=>

light(7downto4)<=D(3downto0);

light(3downto0)<=D(7downto4);

when"101"=>

foriin7downto5loop

light(i)<=D(i-5);

endloop;

light(4downto0)<=D(7downto3);

when"110"=>

light(7)<=D

(1);

light(6)<=D(0);

light(5downto0)<=D(7downto2);

when"111"=>

light(7)<=D(0);

light(6downto0)<=D(7downto1);

whenothers=>light<=D;

endcase;

elsif(kind="00"orkind="01")then

caseNis

when"001"=>

foriin7downto1loop

light(i)<=D(i-1);

endloop;

light(0)<='0';

when"010"=>

foriin7downto2loop

light(i)<=D(i-2);

endloop;

light

(1)<='0';

light(0)<='0';

when"011"=>

foriin7downto3loop

light(i)<=D(i-3);

endloop;

light(2downto0)<="000";

when"100"=>

foriin7downto4loop

light(i)<=D(i-4);

endloop;

light(3downto0)<="0000";

when"101"=>

foriin7downto5loop

light(i)<=D(i-5);

endloop;

foriin4downto0loop

light(i)<='0';

endloop;

when"110"=>

light(7)<=D

(1);

light(6)<=D(0);

foriin5downto0loop

light(i)<='0';

endloop;

when"111"=>

light(7)<=D(0);

foriin6downto0loop

light(i)<='0';

endloop;

whenothers=>light<=D;

endcase;

endif;

elsif(dir='1')then

if(kind="10")then

caseNis

when"001"=>

foriin0to6loop

light(i)<=D(i+1);

endloop;

light(7)<=D(0);

when"010"=>

foriin0to5loop

light(i)<=D(i+2);

endloop;

light(6)<=D(0);

light(7)<=D

(1);

when"011"=>

foriin0to4loop

light(i)<=D(i+3);

endloop;

light(5)<=D(0);

light(6)<=D

(1);

light(7)<=D

(2);

when"100"=>

foriin0to3loop

light(i)<=D(i+4);

endloop;

light(7downto4)<=D(3downto0);

when"101"=>

foriin0to2loop

light(i)<=D(i+5);

endloop;

light(7downto3)<=D(4downto0);

when"110"=>

light(0)<=D(6);

light

(1)<=D(7);

light(7downto2)<=D(5downto0);

when"111"=>

light(0)<=D(7);

light(7downto1)<=D(6downto0);

whenothers=>light<=D;

endcase;

elsif(kind="00")then

caseNis

when"001"=>

foriin0to6loop

light(i)<=D(i+1);

endloop;

light(7)<=D(7);

when"010"=>

foriin0to5loop

light(i)<=D(i+2);

endloop;

light(6)<=D(7);

light(7)<=D(7);

when"011"=>

foriin0to4loop

light(i)<=D(i+3);

endloop;

light(5)<=D(7);

light(6)<=D(7);

light(7)<=D(7);

when"100"=>

foriin0to3loop

light(i)<=D(i+4);

endloop;

light(4)<=D(7);

light(5)<=D(7);

light(6)<=D(7);

light(7)<=D(7);

when"101"=>

foriin0to2loop

light(i)<=D(i+5);

endloop;

foriin3to7loop

light(i)<=D(7);

endloop;

when"110"=>

light(0)<=D(6);

light

(1)<=D(7);

foriin2to7loop

light(i)<=D(7);

endloop;

when"111"=>

light(0)<=D(7);

foriin1to7loop

light(i)<=D(7);

endloop;

whenothers=>light<="XXXXXXXX";

endcase;

elsif(kind="01")then

caseNis

when"001"=>

foriin0to6loop

light(i)<=D(i+1);

endloop;

light(7)<='0';

when"010"=>

foriin0to5loop

light(i)<=D(i+2);

endloop;

light(6)<='0';

light(7)<='0';

when"011"=>

foriin0to4loop

light(i)<=D(i+3);

endloop;

light(5)<='0';

light(6)<='0';

light(7)<='0';

when"100"=>

foriin0to3loop

light(i)<=D(i+4);

endloop;

light(4)<='0';

light(5)<='0';

light(6)<='0';

light(7)<='0';

when"101"=>

foriin0to2loop

light(i)<=D(i+5);

endloop;

foriin3to7loop

light(i)<='0';

endloop;

when"110"=>

light(0)<=D(6);

light

(1)<=D(7);

foriin2to7loop

light(i)<='0';

endloop;

when"111"=>

light(0)<=D(7);

foriin1to7loop

light(i)<='0';

endloop;

whenothers=>light<=D;

endcase;

endif;

endif;

endif;

endprocess;

endrtl;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 开放式CPU 运算器部件实验 移位器 开放式 CPU 运算器 部件 实验 移位

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx