简单数字频率计的设计与制作.docx

简单数字频率计的设计与制作.docx

- 文档编号:30715037

- 上传时间:2023-08-19

- 格式:DOCX

- 页数:28

- 大小:818.06KB

简单数字频率计的设计与制作.docx

《简单数字频率计的设计与制作.docx》由会员分享,可在线阅读,更多相关《简单数字频率计的设计与制作.docx(28页珍藏版)》请在冰豆网上搜索。

简单数字频率计的设计与制作

简单数字频率计的设计与制作

1结构设计与方案选择

1.1设计要求

(1)要求用直接测量法测量输入信号的频率

(2)输入信号的频率为1~9999HZ

1.2设计原理及方案

数字频率计是直接用十进制的数字来显示被测信号频率的一种测量装置。

它不仅可以测量正弦波、方波、三角波和尖脉冲信号的频率,而且还可以测量它们的周期。

所谓频率就是在单位时间(1s)内周期信号的变化次数。

若在一定时间间隔T内测得周期信号的重复变化次数为N,则其频率为f=N/T(1-1)

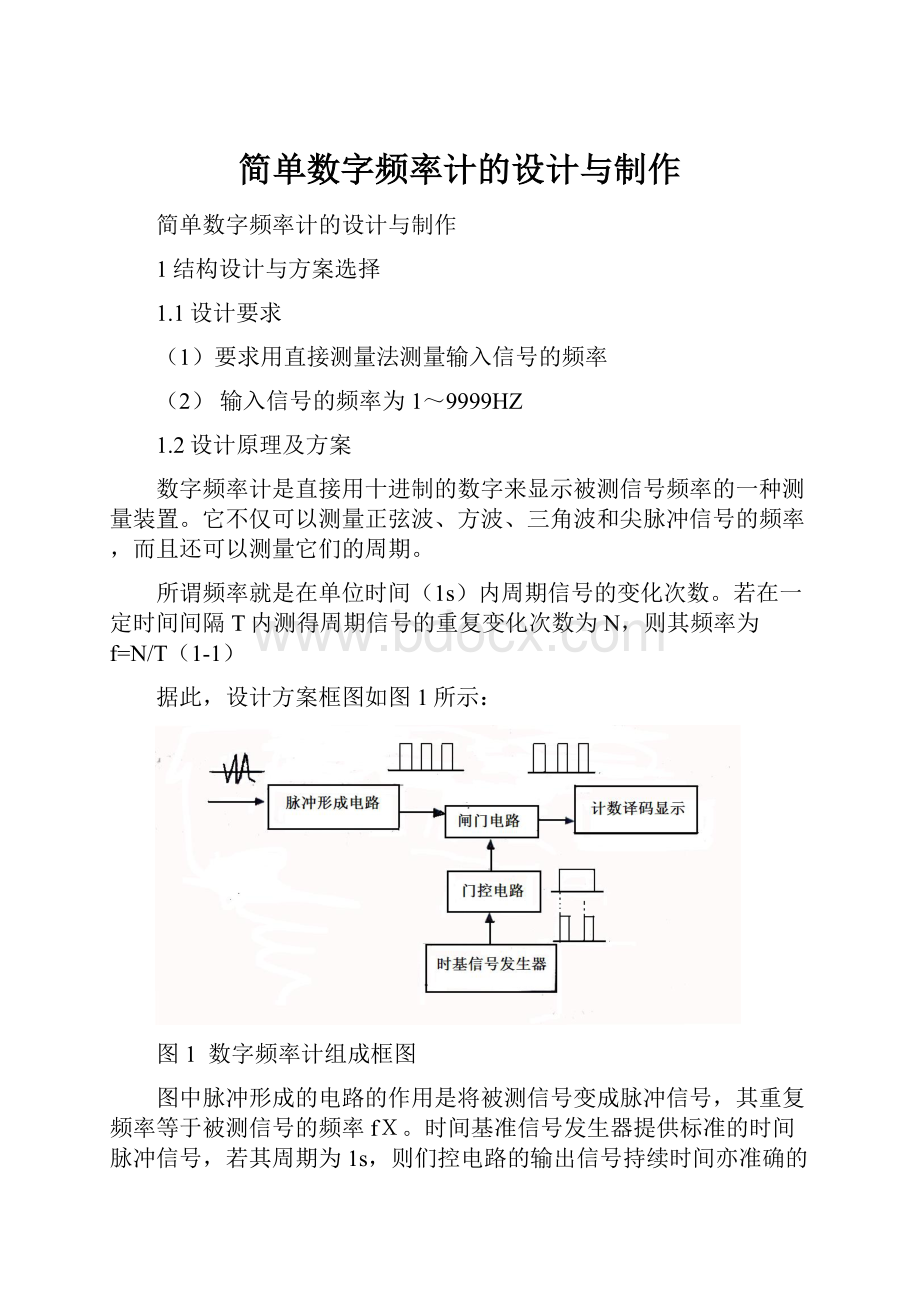

据此,设计方案框图如图1所示:

图1数字频率计组成框图

图中脉冲形成的电路的作用是将被测信号变成脉冲信号,其重复频率等于被测信号的频率fX。

时间基准信号发生器提供标准的时间脉冲信号,若其周期为1s,则们控电路的输出信号持续时间亦准确的等于1s。

闸门电路由标准秒信号进行控制当秒信号来到时,闸门开通,被测脉冲信号通过闸门送到计数器译码显示电路。

秒信号结束时闸门关闭,技计数器得的脉冲数N是在1秒时间内的累计数,所以被测频率fX=NHz。

被测信号fX经整形电路变成计数器所要求的脉冲信号

,其频率与被测信号的频率相同。

时基电路提供标准时间基准信号

,其高电平持续时间t1=1秒,当l秒信号来到时,闸门开通,被测脉冲信号通过闸门,计数器开始计数,直到l秒信号结束时闸门关闭,停止计数。

若在闸门时间1s内计数器计得的脉冲个数为N,则被测信号频率f=NHz,如图2(a)所示,即为数字频率计的组成框图。

图2(a)数字频率计的组成框图

图2(b)数字频率计的工作时序波形

逻辑控制单元的作用有两个:

其一,产生清零脉冲④,使计数器每次从零开始计数;

其二,产生所存信号⑤,是显示器上的数字稳定不变。

这些信号之间的时序关系如图2(b)所示数字频率计由脉冲形成电路、时基电路、闸门电路、计数锁存和清零电路、译码显示电路组成。

1.3数字频率计的主要技术指标

1.3.1频率准确度:

一般用相对误差来表示,本文设计的频率准确度并没有要求。

即:

1.3.2频率测量范围:

在输入电压符合规定要求值时,能够正常进行测量的频率区间称为频率测量范围。

频率测量范围主要由放大整形电路的频率响应决定。

本设计的频率测量范围为:

1Hz—9999Hz。

1.3.3数字显示位数:

频率计的数字显示位数决定了频率计的分辨率。

位数越多,分辨率越高。

本设计的显示位数为:

四位LED数码管显示。

1.3.4测量时间:

频率计完成一次测量所需要的时间,包括准备、计数、锁存和复位时间。

本设计的一次测量时间大约为:

1.25S。

2单元电路的设计

2.1脉冲信号的形成电路

脉冲信号形成电路的作用是将待测信号fx(如正弦波、三角波或者其他呈周期性变化的波形)整形为计数器所要求的脉冲信号,其周期不变。

将其他波形变换成脉冲波的电路有多种,如施密特触发器、单稳态触发器、比较器等。

其中施密特触发器的应用较多。

我在这里设计的电路形式是采用555定时器构成的施密特触发器,电路原理如图3(a)所示。

图3(a)脉冲信号形成电路

图中R7与R8的作用是将被测信号进行电平移动,因为555构成的施密特触发器的上触发电平UT+=2/3Ucc,下触发电平UT=1/3Ucc,如图3(b)所示。

图3(b)脉冲信号形成

输入信号的直流电平Uxo从C3左侧输入

应该满足下列关系1/3Ucc 输入信号的幅度Uxm与直流电平Uxo和回差△UT有关,一般说来,△UT越小,对输入信号的幅值Uxm要求越小,如果需要减小回差,可以在555的控制端CO接入一个正电压。 如果取+Ucc=+5V,回差△UT=1.67V。 对于图4(b)所示的波形图,若取Uxo=1/3Ucc+1/2△UT=2.5V,则输入信号幅度为Uxm>1/2△UT=0.83V.为使Uxo=2.5V,对于图4(a)所示电路,则取R7=R8=10KΩ。 2.2时基电路和闸门电路 如图2(a)所示,闸门电路是控制计数器计数的标准时间信号,决定了被测信号的脉冲通过闸门进入计数器进行计数的计数个数,其精度很大程度上决定了频率计的频率测测量精度。 当要求频率测量精度高时,应使用晶体振荡器通过分频获得。 在此简单数字频率计的中,时基信号采用由555定时器构成的多谐振荡器电路,当标准时间信号(1s高电平)来到时,闸门开通,被测信号的脉冲通过闸门进入计数器计数;标准时间脉冲结束时(为低电平),闸门关闭,计数器无时钟脉冲输入。 例如,时基信号的作用时间为1s,闸门电路将打开1s,若在这段时间内通过闸门电路的脉冲数目为1000个,则被测信号的频率就是1000Hz。 设标准时基为1s的脉冲是由555定时器构成的多谐振荡器电路产生的,由555定时器构成的多谐振荡气的周期计算公式为: 周期计算公式: t=t1+t2=0.693(R1+2R2)C; 占空比为: D=t2/(t1+t2)=R2/(R1+2R2)<50%, t1为正方波的宽度,t2为负方波的宽度; 若取振荡器的频率f0=1/(t1+t2)=0.8HZ,则振荡器的输出波形如图4(b)所示,其中t1=1s,t2=0.25s。 图4(a)标准脉冲产生的闸门电路 图4(b)闸门电路各波形特点 2.3计数电路 计数器用4个74LS190同步十进制可逆计数器构成。 作用是对放大整形电路输出的频率信号进行计数,并将输出的数值输入到锁存器。 如图5所示。 图5计数电路图 U14的INA接外来信号,U11、12、13、14的INB均接相应的QA。 U14的QD接U13的INA,U13的QD接U12的INA,U12的QD接U11的INA。 四个芯片的R01、R02均接地,R91、R92连在一起接时基信号的反向信号。 当R91、R92同为高电平时,四位十进制计数器同时清零。 当R91。 R92同为低电平时,四位十进制计数器正常计数。 2.4锁存电路、译码电路和显示电路 图6锁存、译码、显示电路 锁存器可选用2个8D锁存器74LS273构成。 锁存器的作用是将计数器在1s结束时所计得的数进行锁存,使显示器上能稳定地显示此时计数器的值。 因为计数器在一秒内要计算成千个输入脉冲,若不加锁存器,显示器上的数字将随机数器的输出变化而变化,不便于读数。 当时钟脉冲CP的上升沿到来时,锁存器的输出等于输入,即Q=D。 从而将4个十进制计数器即个位、十位、百位、千位的输出值送到锁存器的输出端。 正脉冲结束后,无论输入端D为何值,输出端Q的状态仍然保持原来的状态。 译码器采用4个74LS48共阴极显示译码器构成。 译码/驱动器74LS48的作用是将输入的高低电平信号转化为数码管需要的高低电平信号,并控制数码灯的亮灭。 具体连接方式见图6。 3整体电路的设计 3.1总电路分析 如图7所示,被测信号(三角波、正弦波、方波)输入由555定时器组成的施密特触发器整形成与输入信号同频率的矩形脉冲。 将该脉冲输入由74LS90组成的十进制计数器用作时钟信号。 另一片555定时器接成的多谐振荡器输出的高电平时间为1S,低电平时间为0.25S的矩形脉冲信号通过闸门,再通过74LS04反向后,输给74LS273,做锁存的时钟信号,同时输给计数器74LS90的R01、R02控制计数器的计数和清零。 当取反后的时基信号来个上升沿时,锁存器锁存0000。 高电平阶段计数器清零,锁存器一直显示0000不变。 低电平时,计数器开始计数,锁存器清零。 当再来个上升沿时锁存器锁存刚才1S内计数器所计的数据,高电平时,计数器清零,锁存器数据保持不变。 低电平时,锁存器清零,计数器计数。 如此循环工作。 若在闸门时间1s内计数器计得的脉冲个数为N,则被测信号频率为f=NHz。 本电路可实现直接测量输入信号的频率,输入的频率范围1~9999HZ。 3.2总电路图 在上述子模块电路的基础上,画出整个电路的总电路图。 如图7所示: 图7整体电路图 4电路的调测与分析 4.1计数电路的调测 图8计数电路调测 如图8所示,连接好电路。 开始仿真,计数器开始计数,计数器可从1计数到9999。 4.2计数、显示电路的调测 如图9所示,连接好电路后。 开始仿真,计数器开始计数,并将相应的计的数通过74LS48芯片译码给七段译码显示器进行显示所计的数。 4.3调试电路的注意事项 在通电调试前,一定要认真检查电路是否有错接、漏接等。 因此要用万用表欧姆档,测量芯片各引脚和各个元器件之间的连接是否正常,测量各个元器件之间的连接是否正常。 用电压表把各个芯片所用的电压调整到规定的数值。 检查各个芯片的接地是否连接牢固。 检查无误,方可通电调试。 4.4测试数据与理论的对比 如图7连接好电路,输入不同频率的被测信号,测其频率。 测试结果如表1所示。 由表1可知,所测频率的误差在允许的范围。 即在误差允许的范围内,所进行设计的电路是符合任务书要求的。 这次课程设计是正确可行的。 图9计数、显示电路调测 表1结果 fx的值(Hz) 数码管显示(Hz) 误差(△fx) 10 9 10.00% 50 48 4.00% 100 93 7.00% 500 518 3.60% 1000 975 2.50% 2000 2110 5.50% 6000 6214 3.57% 7000 6902 1.40% 8000 8189 2.36% 9000 9220 2.44% 9500 9617 1.23% 4.5电路的改进 如图10所示 图10电路改进图 芯片CD40110------十进制加减计数器/锁存/七段 简要说明: 40110为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状态锁存,七段显示译码输出等功能。 40110有2个计数时钟输入端CPU和CPD分别用作加计数时钟输入和减计数时钟输入。 由于电路内部有一个时钟信号预处理逻辑,因此当一个时钟输入端计数工作时,另一个时钟输入端可以是任意状态。 40110的进位输出CO和借位输出BO一般为高电平,当计数器从0~9时, BO输出负脉冲;从9~0时CO输出负脉冲。 在多片级联时,只需要将CO和BO 分别接至下级40110的CPU和CPD端,就可组成多位计数器。 引出端符号: BO皆为输出端 图11CD40110芯片 CO进位输出端CPD减计数器时钟输入端 CPU加计数器时钟输入端CR清除端 /CT计数允许端/LE锁存器预置端 VDD正电源Vss地 Ya~6g锁存译码输出端推荐工作条件: CD40110可功能强大,可简化电路。 做实物时,运用的是此方案。 5所用芯片及其它器件说明 本次设计选用的器件有74LS90,74LS48,74LS273,555定时电路,数码管,共阴极七段LED数码管74LS48等,下面为大家介绍主要器件在这次频率计数器的应用及原理。 5.1555定时器 555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。 但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。 此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。 由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图12所示。 图12555集成电路内部结构 555集成电路是8脚封装,双列直插型,如图13(A)所示,按输入输出的排列可看成如图13(B)所示。 其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。 图13555定时器 5.1.1555构成的施密特触发器 图14555定时器构成的施密特触发器 4.UI再增大时,对电路的输出状态没有影响。 (a)上升过程 (b)下降过程 5.1.2555构成的多谐振荡器 由555定时器构成的多谐振荡器如图15所示,其工作波形见图4(b)所示。 接通电源后,电源VDD通过R1和R2对电容C充电,当Uc2C,由电容C放电时间决定;TH=0.7(R1+R2)C,由电容C充电时间决定,脉冲周期T≈TH+TL。 图15555构成多谐振荡器 上面仅讨论了由555定时器在本次数字频率计课程设计中的应用及原理。 实际上,由于555定时器灵敏度高,功能灵活,因而在电子电路中获得广泛应用。 5.274LS273锁存器 74LS273作为一种带清除端的触发器,在电路中的主要作用是将计数器在1s结束时所计的数进行锁存,使显示器上能稳定地显示此时计数器的值。 由74LS273的功能表(表2)可知,当时钟脉冲CP的正跳变来到时,锁存器的输出等于输入,即Q=D。 从而将计数器的输出值送到锁存器的输出端,正脉冲结束后,无论D为何值,输出端Q的状态仍保持原来的状态Qn不变,所以在计数期间内,计数器的输出不会送到译码显示器.其引脚功能如图16所示。 表274LS273功能表 输入 输出Q 清除 时钟 D L X X L H H H H L L H L X Q0 注: Q0=稳态输入条件建立之前Q的电平 图1674LS273引脚图 5.374LS90计数器 集成十进制异步计数器的型号有: 74LS90、74196、74S196,74LS196、74290、74LS290等,它们都是按照8421BCD码进行加法计数的电路(如图17),本设计采用的是74LS90计数器。 图178421BCD码加法计数状态图 74LS90是TTL系列的十进制计数器,其内部由四个主从触发器和一些附加门电路组成,以提供一个2分频计数器和一个三级的二进制计数器。 其引脚排列如图7所示;逻辑功能示意图如图18所示。 图1874LS90的引出端排列图 此芯片有门控置“0”输入端及还有门控置“9”输入端。 为了使用其最大计数长度,须将Q0输出端连到B输入端。 计数输入脉冲加到输入端A上,则输出为BCD计数(见表3)。 若把Q3连接到输入端A上,输出则为二五混合进制(见表4)。 这时输入脉冲加在B端,在Q0的输出上可以得到一个十分频的方波。 74LS90复位/计数功能表(见表5)。 图1974LS90的逻辑功能示意图 表3BCD计数时序表4二五混合进制 由于本次课程设计的技术指标为1Hz—9999Hz,因此就要求四个计数器级联,图20是由74LS90利用输出Q3控制高一位的CP端构成的加计数级联图。 表574LS90复位/计数功能表 图20异步计数器级联方案 5.4数码译码显示器 5.4.1七段译码管 一个LED数码管可用来显示一位0~9十进制数和一个小数点。 小型数码管(0.5寸和0.36寸)每段发光二极管的正向压降,随显示光(通常为红、绿、黄、橙色)的颜色不同略有差别,通常约为2~2.5V,每个发光二极管的点亮电流在5~10mA。 LED数码管要显示BCD码所表示的十进制数字就需要有一个专门的译码器,该译码器不但要完成译码功能,还要有相当的驱动能力。 LED数码管是目前最常用的数字显示器,按连接方式不同,七段显示数码管分为共阴极和共阳极两种。 图21(a)、(b)为共阴管和共阳管的电路,(c)为两种不同出线形式的引出脚功能图。 (d)为7段LED显示器显示的字形。 图21(a)共阴连接(“1”电平驱动)图21(b)共阳连接(“0”电平驱动) 图21(c)符号及引脚功能 图21(d)7段LED显示器的字形 5.4.2BCD码七段译码驱动器 此类译码器型号有74LS47(共阳),74LS48(共阴),CC4511(共阴)等,本设计采用74LS48BCD码七段译码/驱动器,并驱动共阴极LED数码管。 图22为74LS48引脚排列图;图23为74LS48内部功能原理图。 图2274LS48引脚排列图 图2374LS48的内部功能原理图 其中: 1、2、6、7—BCD码输入端;a、b、c、d、e、f、g—译码输出端,输出“1”有效,用来驱动共阴极LED数码管。 16脚为电源端,接5V电源。 三个控制输入端 、 、 都是低电平有效。 其中: 是输入输出共用一个端口,只有输入4位数据为0时,并且 =0时,该端口为输出状态,输出为低电平。 功能见表6。 表674LS48功能表 三个控制输入端 、 、 各自的功能如下: --灯测试输入端,用来检查数码管七段是否都能正常工作。 当 =0且 =1时,不管其他输入状态如何,a--g均输出有效的逻辑“1”,数码管七段均应点亮。 当 =1时,译码器方可进行译码工作。 --灭零输入端,可用来熄灭无意义的“0”显示,如整数前的“0”和小数点后的“0”。 --熄灭输入端/灭零输出端。 当 =0时,不管其他输入状态如何,数码管七段均熄灭。 当 =1时,译码器正常工作。 当输入数据DCBA=0000 时,灭“0”端 =0时,为灭0状态, 变为输出端,输出为低电平。 同时由于74LS48内部有升压电阻而无需外部电阻。 结束语 这次课程设计对我个人而言,确实是一项艰巨而富有挑战性的任务。 刚开始拿到这个题目,我头都是大的,摸不清头脑,不知道怎样下手去做。 不过第二天,我就开始大量查资料。 从网上XX,去图书馆借相应的书籍。 后来终于在查阅大量网络和图书资料后构出了自己的原理图。 并用Multisim11进行了仿真。 在为期两周的课程设计期间,我投入了自己的热情和精力,从开始设计电路图,选择元器件,到使用Multisim11仿真电路等等。 在共同做实物的过程中出现了不少的问题,我们组的成员没有气馁,没有退缩,积极向老师和同学请教,并且一遍又一遍的重复实践,直到得到我们组所期望的结果。 事实也证明我们组的努力没有白费,认真严谨的态度给我们带来了成功的喜悦! 我们组在规定的时间内设计出的电路能够满足任务书上的两个设计要求。 并且实现了对被测信号的整形和测频率后的清零功能。 这短短两周的课程设计,我感觉到自己在课本上学到的理论知识和实践仍有一定的差距。 这次课程设计其实是对我是一次检验,通过它的检验,我明白了以前所学过的只是书本上的一些理论基础知识,缺乏实践应用这一环节。 我在具体电路的设计中,理论和实践方面的联系有很多欠缺的地方,比如说对某些芯片的一些功能端缺乏足够深入的了解,不能将其运用的自如。 在焊接板子时,在板子上布局方面刚开始时没有考虑合理,把线跳得很规律。 但在最后,我们组均把这些遇到的问题一一克服了。 我通过查资料知道,数字频率计关键的地方就是计数器计数、锁存器锁存、以及译码器译码、显示器显示。 弄懂这些后,再弄明白在实际的电路搭接过程中各个芯片的各管脚功能端的连接,电路功能就很容易实现了。 在单元电路的计算方面,主要就是多频振荡器1秒脉冲频率的计算方法。 通过这次课程设计,我认识到实践的重要性,它加深了我对数字电路的认识。 它使我掌握了设计一个数字电路的基本方法和基本步骤,增强了我在实际设计中寻找问题,解决问题的能力。 此次课程设计的成功不仅帮助我更好地掌握了书本知识,还增强了我的自信,培养了我独立思考、自主学习和动手能力。 不过,在这次课程设计的过程中,我还是发现了自己的不足。 如运用Multisim11仿真电路,开始时我的操作不是很熟练,经常找不到所需的元件,仿真频频失败。 同时对Protel99se了解的不是很深,没法将其强大的功能用的课设中去,我觉得对我来说是一种遗憾。 从现在开始,我要制定好对像Multisim11、Protel99se、protus等软件的学习计划,方便以后的学习和工作。 总的来说,电路设计的成功其中包含了老师和同学热心的帮助。 同时我在数字电路方面的实践水平如电路设计、元件的布局、以及制图方面的水平都得到了很大的提高。 我受益匪浅。 致谢 两周的课程设计结束了,在此,我衷心的感谢翁老师对我们的关心和指导,特别在检查实物时,耐心帮我们找需要的直流电源和信号发生器。 一点点改变信号发生器的频率,来检验我们实物是否实现了所要求的功能。 在设计过程中,我遇到了不少问题和困难,我没有放弃。 最后所取得的成绩不仅凝结着自己的汗水和心血,更离不开翁老师和同学的鼓励与帮助。 在此,我向他们表示感谢。 通过这次课设,我的自主学习能力、思考能力和动手能力都得到了提升,感觉自己收获蛮大的。 参考文献 [1]康华光.电子技术基础数字部分(第五版).高等教育出版社.2006.1 [2]陈惠民.数字逻辑电路分析与设计学习指导及题解.清华大学出版社.2007.5 [3]梁宗善.电子技术基础课程设计第1版.武昌: 华中理工大学出版社.1995.1 [4]王松武.于鑫.武思军.电子创新设计与实践第1版.国防工业出版社.2005.1 [5]毛期俭.数字电路与逻辑设计实验及应用.人民邮电出版社,2005 [6]潘明.基于复杂可编程逻辑器件的数字频率计设计[J].电子世界,2001.1 [7]阎石.数字电子技术基础.高等教育出版社.2006.5 附录 元件清单列表 序号 名称 代号 规格型号 数量 1 七段数码管 U5-U8 SEVEN_SEG_COM_K_GREEN 4 2 排阻 R1-R4 2*8DIP 4 3 集成芯片 U1-U4 74LS48N 4 4 集成芯片 U10,U15 74LS273N 2 5 集成芯片 U11-U14 74LS90D 4 6 集成芯片 U9、U17 LM555CN 2 7 集成芯片 U16A 7404N 1 8 电阻 R5 36K 1 9 电阻 R6 107K 1 10 电阻 R7 10K 1 11 电阻 R8 10K 1 10 电容 C1 0.01uF 1 11 电容 C2 10uF 1 12 电容 C3 1uF 1 13 电容 C4 0.01uF 1 12 直流电源 VCC +5V 1

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 简单 数字频率计 设计 制作

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#2机组现场施工用电布置措施.docx

#2机组现场施工用电布置措施.docx