可编程逻辑实验报告.docx

可编程逻辑实验报告.docx

- 文档编号:8013338

- 上传时间:2023-01-27

- 格式:DOCX

- 页数:32

- 大小:248.89KB

可编程逻辑实验报告.docx

《可编程逻辑实验报告.docx》由会员分享,可在线阅读,更多相关《可编程逻辑实验报告.docx(32页珍藏版)》请在冰豆网上搜索。

可编程逻辑实验报告

西安邮电学院

可编程逻辑实验报告

班级

:

班内序号

:

学生姓名

:

学号

:

时间

:

实验一:

用原理图输入法设计门电路

一:

实验目的:

1通过一个简单的反相器实现,初步了解CPLD开发的全过程;

2学会利用软件和硬件实现对数字电路的逻辑功能进行验证和分析;

3能够通过CPLD开发实现具有反相器功能的数字电路。

二:

实验所用仪表及主要器材:

MAX+plusⅡ软件

三:

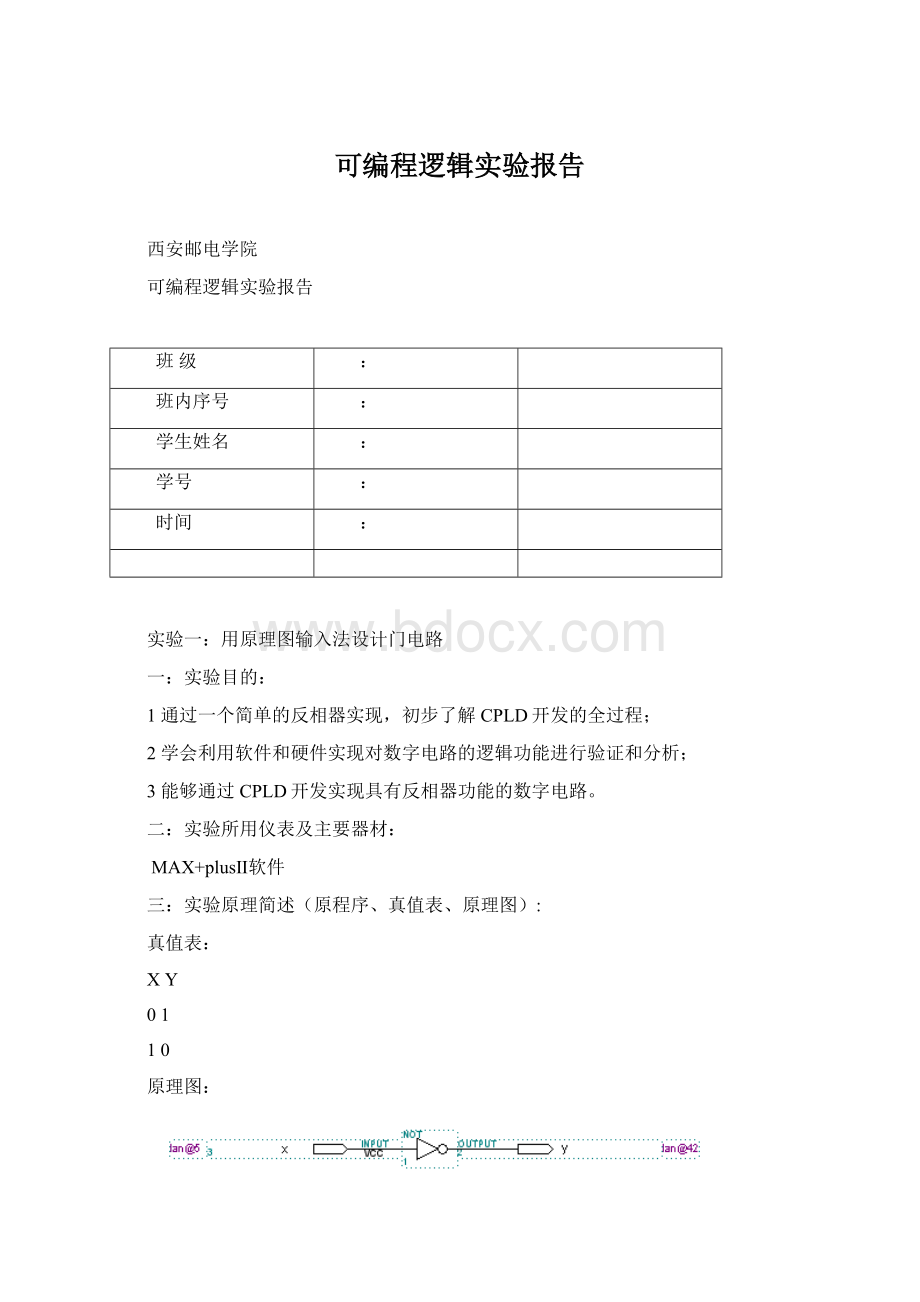

实验原理简述(原程序、真值表、原理图):

真值表:

XY

01

10

原理图:

四:

实验测量记录(数据、仿真波形图及分析、原程序分析、硬件测试实分析):

仿真波形图:

五:

实验心得(实验中问题的解决方法等):

经过第一次实验,初步了解了CPLD开发的全过程,在实验时由于是第一次接触MAX+plusⅡ软件,所以有些不适应,实验过程中也遇到了很多麻烦,但在严格按照书上的步骤进行试验后,掌握了一定的基础。

实验二用文本输入法设计门电路

一:

实验目的

1通过各种常见电路的实现,进一步熟悉CPLD开发的全过程;

2认识各种常见门电路,并掌握它们的逻辑功能。

3能够通过CPLD的开发实现具有门电路的数字电路。

二:

实验所用仪表及主要器材

MAX+plusⅡ软件

三:

实验原理简述(原程序、真值表、原理图)

1与门:

1)原程序:

Libraryieee

Useieee.std_logic_1164.all

Entityand2is

Port(a,b:

instd_logic

y:

outstd_logic)

End;

Architecturerel_1ofand2is

Begin

Y<=axorb;

2)真值表:

aby

000

010

100

111

2或门:

1)原程序:

Libraryieee

Useieee.std_logic_1164.all

Entityor2is

Port(a,b:

instd_logic

y:

outstd_logic)

End;

Architecturerel_1ofor2is

Begin

Y<=axorb;

2)真值表:

aby

000

011

101

111

3与非门:

1)原程序:

Libraryieee

Useieee.std_logic_1164.all

Entitynand2is

Port(a,b:

instd_logic

y:

outstd_logic)

End;

Architecturerel_1ofnand2is

Begin

Y<=axorb;

2)真值表:

aby

001

011

101

110

4或非门:

1)原程序:

Libraryieee

Useieee.std_logic_1164.all

Entitynor2is

Port(a,b:

instd_logic

y:

outstd_logic)

End;

Architecturerel_1ofnor2is

Begin

Y<=axorb;

2)真值表:

aby

001

010

100

110

5异或门:

1)原程序:

Libraryieee

Useieee.std_logic_1164.all

Entityxor2is

Port(a,b:

instd_logic

y:

outstd_logic)

End;

Architecturerel_1ofxor2is

Begin

Y<=axorb;

2)真值表:

aby

000

011

101

110

6同或门:

1)原程序:

Libraryieee

Useieee.std_logic_1164.all

Entityxnor2is

Port(a,b:

instd_logic

y:

outstd_logic)

End;

Architecturerel_1ofxnor2is

Begin

Y<=axorb;

2)真值表:

aby

001

010

100

111

四:

实验测量记录(数据、仿真波形图及分析、原程序分析、硬件测试实分析)

仿真波形图:

1与门:

2或门:

3与非门:

4或非门:

5异或门:

6同或门:

五:

实验心得(实验中问题的解决方法等):

经过本次实验已经可以熟练的使用MAX+plus开发实验具有门电路的数字电路,并且可以通过文本输入法设计常见的门电路,我们通过本次实验,了解了门电路的编程。

实验三组合逻辑电路设

(一)

一.实验目的

(1)熟练掌握组合逻辑电路的VHDL描述方法。

(2)掌握利用CPLD器件实现组合逻辑数字电路的方法和过程。

(3)熟练掌握“case”语句与“if…else…”语句的用法。

二.实验器材

PC,可编程逻辑实验电路板,下载线,USB电源线,双踪示波器,数字万用表,导线若干。

三.实验原理及注意事项

可编程逻辑实验是建立在数字电路基础实验上的一个更高层次的设计性实验。

它是借助可编程逻辑器件(PLD),采用在系统可编程技术(ISP),利用电子设计自动化软件(EDA),在计算机(PC)平台上进行的。

这与以往的基于独立元器件的实验方法、实验手段和实验仪器上都有很大不同,要求操作者具有一定的计算机软件操作基础。

四.实验内容

(2)输入为8421BCD码,输出为余三码,如表所示:

数字

输入

(8421BCD码)

X3X2X1X0

输出

(余3码)

Y3Y2Y1Y0

数字

输入

(8421BCD码)

X3X2X1X0

输出

(余3码)

Y3Y2Y1Y0

0

1

2

3

4

0000

0001

0010

0011

0100

0011

0100

0101

0110

0111

5

6

7

8

9

0101

0110

0111

1000

1001

1000

1001

1010

1011

1100

(2)8421BCD码转换成余3码的VHDL代码如下:

libraryieee;

useieee.std_logic_1164.all;

entityyu3is

port(a:

instd_logic_vector(3downto0);

y:

outstd_logic_vector(3downto0));

endyu3;

architecturemblofyu3is

begin

process(a)

begin

caseais

when"0000"=>y<="0011";

when"0001"=>y<="0100";

when"0010"=>y<="0101";

when"0011"=>y<="0110";

when"0100"=>y<="0111";

when"0101"=>y<="1000";

when"0110"=>y<="1001";

when"0111"=>y<="1010";

when"1000"=>y<="1011";

when"1001"=>y<="1100";

whenothers=>y<="ZZZZ";

endcase;

endprocess;

end;

MAX+plusII仿真波形如下:

五.实验总结及分析

在使用MAX+plusII进行仿真时由于软件使用老出现bug,在设计VHDL语言时一定要注意,语法错误的检查,调试仿真波形时,也要注意有时候源程序可能已经没有问题了,但是由于CLK脉冲可能没给好或者是输入信号的脉冲信号没有设置好时间间隔会导致结果输出出现一段“0”、“1”都存在的情形,这时要最好能将输入波形跟CLK波形使用2、3倍的时间间隔。

实验四组合逻辑电路设计

(二)

一:

实验目的

1.掌握设计组合逻辑电路的方法。

2.通过开发CPLD来实现组合逻辑电路的功能。

二:

实验所用仪表及主要器材

计算机,鼠标,键盘,显示器,MAX+PLUSII软件

三:

实验原理简述(源程序、真值表、原理图)

(1)二个2位二进制数相乘

源程序:

Libraryieee;

Useieee.std_logic_1164.all;

Entitye4_1_xiangchen2is

Port(a:

instd_logic_vector(3downto0);

y:

outstd_logic_vector(3downto0));

End;

Architecturertlofe4_1_xiangchen2is

Begin

Process(a)

Begin

Caseais

When"0000"=>y<="0000";

When"0001"=>y<="0000";

When"0010"=>y<="0000";

When"0011"=>y<="0000";

When"0100"=>y<="0000";

When"0101"=>y<="0001";

When"0110"=>y<="0010";

When"0111"=>y<="0011";

When"1000"=>y<="0000";

When"1001"=>y<="0010";

When"1010"=>y<="0100";

When"1011"=>y<="0110";

When"1100"=>y<="0000";

When"1101"=>y<="0011";

When"1110"=>y<="0110";

When"1111"=>y<="1001";

Whenothers=>y<="ZZZZ";

Endcase;

Endprocess;

End;

真值表:

a

Y

0000

0000

0001

0000

0010

0000

0011

0000

0100

0000

0101

0001

0110

0010

0111

0011

1000

0000

1001

0010

1010

0100

1011

0110

1100

0000

1101

0011

1110

0110

1111

1001

(2)二进制全减器

Libraryieee;

Useieee.std_logic_1164.all;

Useieee.std_logic_unsigned.all;

Entitye4_2_jian2is

Port(a,b,ci:

instd_logic;

f,co:

outstd_logic);

End;

Architecturerel_1ofe4_2_jian2is

Begin

Process(a,b,ci)

Begin

If(a='0'andb='0'andci='0')then

F<='0';co<='0';

elsif(a='0'andb='0'andci='1')then

F<='1';co<='1';

elsif(a='0'andb='1'andci='0')then

F<='1';co<='1';

elsif(a='0'andb='1'andci='1')then

F<='0';co<='1';

elsif(a='1'andb='0'andci='0')then

F<='1';co<='0';

elsif(a=’1’andb=’0’andci=’1’)then

F<=’0’;co<=’0’;

elsif(a=’1’andb=’1’andci=’0’)then

F<=’0’;co<=’0’;

else

F<=’1’;

Co<=’1’;

Endif;

Endprocess;

End;

真值表:

a

b

ci

f

co

0

0

0

0

0

0

0

1

1

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

(3)开关控制电路

源程序:

Libraryieee;

Useieee.std_logic_1164.all;

entitye4_3_switcheris

port(a,b,c:

instd_logic;

f:

outstd_logic);

end;

architecturebhvofe4_3_switcheris

begin

process(a,b,c)

begin

if(a='0'andb='0'andc='0')then

f<='0';

elsif(a='0'andb='0'andc='1')then

f<='1';

elsif(a='0'andb='1'andc='0')then

f<='1';

elsif(a='0'andb='1'andc='1')then

f<='0';

elsif(a='1'andb='0'andc='0')then

f<='1';

elsif(a='1'andb='0'andc='1')then

f<='0';

elsif(a='1'andb='1'andc='0')then

f<='0';

elsif(a='1'andb='1'andc='1')then

f<='0';

else

f<='1';

endif;

endprocess;

end;

真值表:

a

b

c

f

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

0

0

1

1

0

1

0

1

1

0

0

1

1

1

0

四:

实验测量记录(数据、仿真波形图及分析、原程序分析、硬件测试实分析)

(1)二个2位二进制数相乘的波形图:

(2)二进制全减器的波形图:

(3)开关控制电路的波形图:

五:

实验心得(实验中问题的解决方法等)

通过本次实验,我进一步熟悉了Max+PLUSII软件的使用,并进一步学习了一些基本的VHDL语法知识,并利用VHDL对较为复杂的组合电路进行描述和仿真。

本次实验除了学习了VHDL的相关知识外,还复习了数字电路的知识,相信对于以后的学习和工作都有很大的好处。

实验五显示驱动电路设计

一:

实验目的

1:

了解八段数码管的工作原理,

2:

设计一个数码管驱动电路,显示0-F之间的数字,以备以后调用。

二:

实验所用仪表及主要器材

MAX+plusII软件

三:

实验原理简述(原程序、真值表、原理图)

源程序:

libraryieee;

useieee.std_logic_1164.all;

entityqiduanis

port(a:

instd_logic_vector(3downto0);

y:

outstd_logic_vector(6downto0));

end;

architecturertlofqiduanis

begin

process(a)

begin

caseais

when"0000"=>y<="1111110";

when"0001"=>y<="0110000";

when"0010"=>y<="1101101";

when"0011"=>y<="1111001";

when"0100"=>y<="0110011";

when"0101"=>y<="1011011";

when"0110"=>y<="1011111";

when"0111"=>y<="1110000";

when"1000"=>y<="1111111";

when"1001"=>y<="1111011";

when"1010"=>y<="1110111";

when"1011"=>y<="0011111";

when"1100"=>y<="1001110";

when"1101"=>y<="0111101";

when"1110"=>y<="1001111";

when"1111"=>y<="1000111";

whenothers=>y<="ZZZZZZZ";

endcase;

endprocess;

end;

真值表:

输入输出

数字A3A2A1A0YaYbYcYdYeYfYg字型

0000011111100

1000101100001

2001011011012

3001111110013

4010001100114

5010110110115

6011010111116

7011111100007

8100011111118

9100111110119

1010101110111A

1110110011111B

1211001001110C

1311010111101D

1411101001111E

1511111000111F

四:

实验测量记录(数据、仿真波形图及分析、原程序分析、硬件测试实分析)

实验波形图

五:

实验心得(实验中问题的解决方法等)

经过做这个实验使我们更进一步的了解了数码管的工作原理。

开始的时候对共阴极数码管和共阳极数码管的认识不是很清楚,通过查阅资料了解数码管的封装,然后来对应它的管脚。

实验六触发器设计

一:

实验目的

1:

认识RS触发器,JK触发器,D触发器和T触发器;

2:

掌握RS触发器,JK触发器,D触发器和T触发器的逻辑功能和动作特点。

二:

实验原理简述

源程序:

1,钟控RS触发器

Libraryieee;

Useieee.std_logic_1164.all;

Entityrsff_1is

Port(r,s:

bit;

cp:

instd_logic;

q,qb:

bufferbit);

End;

Architecturertlofrsff_1is

Begin

process(cp,r,s)

Begin

if(cp='1')then

qb<=snorq;

q<=rnorqb;

endif;

endprocess;

end;

真值表:

CLKRSQ’

100Q

1011

1100

111X

0XXQ

2,JK触发器

Libraryieee;

Useieee.std_logic_1164.all;

Entitytest10is

Port(pset,clr,clk,j,k:

instd_logic;

q,qb:

outstd_logic);

Endtest10;

Architecturertloftest10is

Signalq_s,qb_s:

std_logic;

Begin

Process(pset,clr,clk,j,k)

Begin

IF(pset='0')and(clr='1')then

q_s<='1';

qb_s<='0';

ELSIF(pset='1')and(clr='0')then

q_s<='0';

qb_s<='1';

ELSIF(clk'EVENTandclk='1')then

IF(j='0')and(k='1')then

q_s<='1';

qb_s<='0';

ELSIF(j='1')and(k='0')then

q_s<='0';

qb_s<='1';

ELSIF(j='1')and(k='1')then

q_s<=NOTq_s;

qb_s<=NOTqb_s;

ENDIF;

ENDIF;

q<=NOTq_s;

qb<=NOTqb_s;

ENDProcess;

ENDrtl

真值表:

PRNCLRNCPJKQ

10XXX1

01XXX0

11XXX1

00↑;00hold

00↑101

00↑010

00↑11Toggle

3,D触发器

Libraryieee;

Useieee.std_logic_1164.all;

Entitytest11is

Port(pset,clr,clk,d:

instd_logic;

q,qb:

outstd_logic);

End;

Architecturertloftest11is

Signalq_s,qb_s:

std_logic;

Begin

Process(pset,clr,clk,d)

Begin

IF(pset='0')and(clr='1')then

q_s<='1';

qb_s<='0';

ELSIF(pset='1')and(clr='0')then

q_s<='0';

qb_s<='1';

ELSIF(clk'EVENTandclk='1')then

IF(d='0')then

q_s<='1';

qb_s<='0';

ELSIF(d='1')then

q_s<='0';

qb_s<='1';

ENDIF;

ENDIF;

q<=NOTq_s;

qb<=NOTqb_s;

ENDProcess;

ENDrtl;

真值表:

PRNCLRNCLKDQ

10XX1

01XX0

11XX1

00↑11

00↑00

000Xhold

三、实验测量记录

1:

RS触发器波形图:

2:

JK触发器波形图:

3:

D触发器波形图:

四、实验分析

通过这次实验,我认识RS触发器,JK触发

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 可编程 逻辑 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx