AXI4功能.docx

AXI4功能.docx

- 文档编号:8364998

- 上传时间:2023-01-30

- 格式:DOCX

- 页数:14

- 大小:387.21KB

AXI4功能.docx

《AXI4功能.docx》由会员分享,可在线阅读,更多相关《AXI4功能.docx(14页珍藏版)》请在冰豆网上搜索。

AXI4功能

AXI4功能

AXI4协议基于猝发式传输机制。

在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。

在主设备和从设备之间所传输的数据分别使用到从设备的写数据通道和到主设备的读数据通道。

在从主设备到从设备的写数据交易中,AXI有一个额外的写响应通道,从设备通过该通道向主设备发出信号表示完成写交易。

所有的AXI4包含了5个不同的通道:

l读地址通道(Readaddresschannel,AR);

写地址通道(Writeaddresschannel,AW);l

l读数据通道(Readdatachannel,R);

写数据通道(Writedatachannel,W);l

写响应通道(Writelresponsechannel,B);

每个通道由一个信号集构成,并且使用双向的VALID和READY握手信号机制。

信息源使用VALID信号,表示在通道上存在可用的有效数据或者控制信息;而信息接收源使用READY信号,表示可以接收数据。

读数据通道和写数据通道也包含LAST信号,该信号用来表示在一个交易发生时,最后一个传输的数据项。

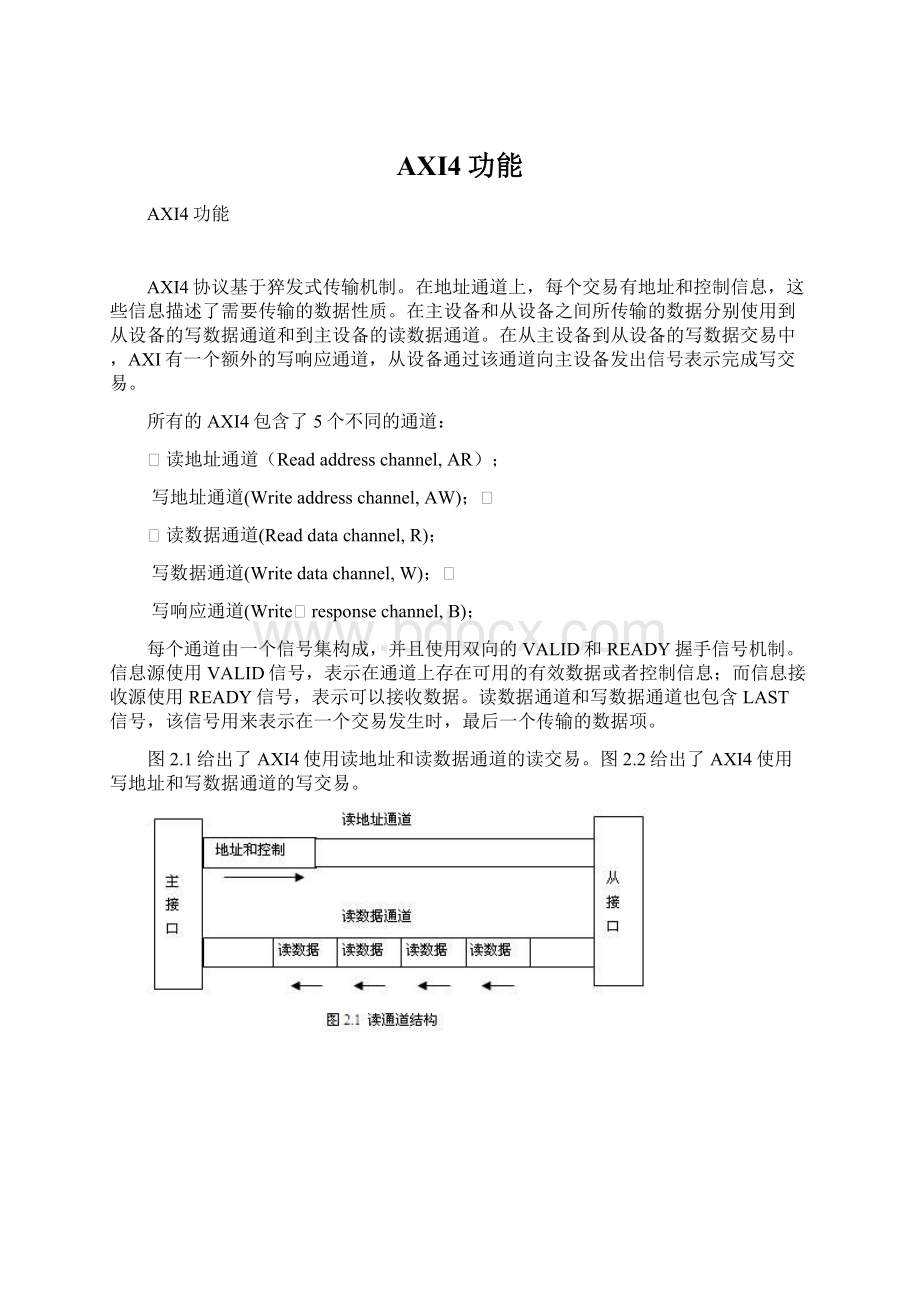

图2.1给出了AXI4使用读地址和读数据通道的读交易。

图2.2给出了AXI4使用写地址和写数据通道的写交易。

2.2.1AXI4全局信号

表2.1给出了AXI4的全局信号。

2.2.2低功耗接口信号

表2.2给出了AXI4的低功耗接口信号。

2.2.3AXI4通道及信号

读和写交易有各自的地址通道。

地址通道上给出交易所要求的地址和控制信息。

AXI4读和写地址通道包括下面的机制:

l可变长度的猝发操作,每次猝发操作包含1-256数据;

提供服务质量(QoS)信号l

支持多个区域接口;l

l猝发传输不能超过4k边界;

包裹、递增和非递增猝发;l

使用互斥和锁的原子操作;l

系统级缓存和缓冲控制;l

l安全和特权访问。

1.读和写地址通道

读和写交易有各自的地址通道。

地址通道加载交易所有要求的地址和控制信息,

表2.3给出了写地址通道信号及信号定义。

表2.4给出了读地址通道信号及信号的定义。

2.读数据通道

读数据通道传送所有来自从设备到主设备的读数据及读相应信息。

表2.5给出了读数据通道信号及其信号定义。

读数据通道包括:

l数据总线宽度:

8、16、32、64、128、256、512和1024位宽度;

读响应表示读交易完成的状态l

3.写数据通道

写数据通道传送所有从主设备到从设备的写数据。

表2.6给出了写数据通道信号及信号定义。

写数据通道包括:

l数据总线宽度:

8、16、32、64、128、256、512和1024位宽度;

每8位有一个字节通道选通,用来表示数据总线上的哪个字节是有效的;l

4.写响应通道

写响应通道提供了一种方法,用于从设备响应写交易。

所有的写信号使用完成信号。

每个响应用于一次猝发的完成,而不是用于每个交易的数据。

读交易和写交易可以通过下面的交易例子进行说明:

1)读猝发交易

2)重叠猝发交易

3)写猝发交易

表2.7给出了写响应通道信号及信号定义。

图2.3给出了读猝发交易过程中典型信号的交互过程。

图2.4给出了写交易过程中典型信号的交互过程。

2.2.4AXI4交易通道的握手信号关系

为了避免死锁条件,必须考虑握手信号之间存在的依赖关系。

在任何交易中:

lAXI互联中的VALID信号不依赖于交易中其它元件的READY信号;

lREADY信号能等待VALID信号的确认;

2.2.4.1AXI4读交易的握手信号关系

图2.5给出了读交易中握手之间的依赖关系。

在读交易中:

在确认ARREADY信号前,从设备能等待确认ARVALID信号;l

l在从设备通过确认RVALID信号开始返回数据前,必须等待确认所有的ARVALID和ARREADY信号;

2.2.4.2AXI4写交易的握手信号关系

图2.6给出了写交易中握手之间的依赖关系。

在写交易中:

l在确认AWVALID和WVALID信号前,主设备不需要等待从设备确认AWREADY或者WREADY信号;

l在确认AWREADY前,从设备能等待AWVALID或WVALID信号,或者全部这两个信号;

l在确认WREADY前,从设备能等待AWVALID或WVALID信号,或者全部这两个信号;

从设备在确认BVALID前,从设备必须等待确认所有的AWVALID和AWREADY信号;l

l在确认BVALID前,从设备不需要等待主设备确认BREADY信号。

l在确认BREADY前,主设备能等待BVALID信号;

2.2.5AXI4猝发类型及地址计算

2.2.5.1AXI4猝发类型

AXI协议中定义了三种猝发类型:

固定猝发(Fixedburst);l

l递增猝发(Incrementingburst);

包裹猝发(Wrappinglburst)

表2.8给出了ARBURST和AWBURST信号所选择的猝发类型:

对于包裹式的猝发方式,有两个限制:

开始地址必须对齐传输大小;l

l猝发的长度必须是2,4,8或16。

大于16拍的猝发传输只支持INCR类型。

WRAP和FIXED类型只限于小于16拍的猝发传输。

2.2.5.2AXI4猝发地址

为了说明猝发交易过程中地址的计算方法,首先给出计算过程中,所需要使用的一些术语:

lStart_Address:

主设备给出的开始地址;

Number_Bytes:

每次数据传输过程中最大的字节个数;l

lData_Bus_Bytes:

数据总线上的字节通道的个数;

Aligned_Address:

开始地址的对齐版本;l

lBurst_Length:

在一个猝发中数据传输的总个数;

Address_N:

在一个猝发中传输N个的地址;l

Wrap_Boundary:

l在一个包裹猝发方式的低地址;

Lower_Byte_Lane:

一个传输最低寻址字节的字节通道;l

Upper_Byte_Lane:

l一个传输中最高寻址字节的字节通道;

INT(x):

x取整操作;l

给上面的术语进行如下的赋值操作:

lStart_Address=ADDR;

Number_Bytes=2SIZE;l

Burst_Length=LEN+1;l

lAligned_Address=(INT(Start_Address/Number_Byte))xNumber_Bytes;

在一个猝发中,第一个传输的地址表示为:

lAddress_1=Start_Address;

在一个猝发中,传输N个数据后的地址表示为:

lAddress_N=Aligned_Address+(N-1)xNumber_Bytes;

对于WARP的猝发方式,其边界由下式确定为:

lWrap_Boundary=(Int(Start_Address/(Number_BytesxBurst_Length)))x

(Number_BytesxBurst_Length);

如果Address_N=Wrap_Boundary+(Number_BytesxBurst_Length).则使用这个等式:

Address_N=Wrap_Addressl

在边界后,使用这个等式:

lAddress_N=Start_Address+((N–1)xNumber_Bytes)-(Number_BytesxBurst_Length);

使用下面的等式确定第一个传输中使用哪个字节通道:

Lower_Byte_Lane=Start_Addressl-(INT(Start_Address/Data_Bus_Bytes))

xData_Bus_Bytes

Upper_Byte_Lanel=Aligned_Address+(Number_Bytes-1)-

(INT(Start_Address/Data_Bus_Bytes))xData_Bus_Bytes;

使用下面的等式确定在一个猝发中第一个传输后用于所有传输中使用哪个字节通道:

lLower_Byte_Lane=Address_N–(INT(Address_N/Data_Bus_Bytes))xData_Bus_Bytes;

Upper_Byte_Lane=Lower_Byte_Lane+Number_Bytes–l1;

传输数据的范围在:

DATA[(8xUpper_Byte_Lane)+7:

(8xlLower_Byte_Lane)];

2.2.6AWCACHE和ARCACHE属性

下面详细介绍了AXI4中AWCACHE和ARCACHE信号的属性。

2.2.6.1AWCACHE[3:

2]和ARCACHE[3:

2]

AWCACHE[2]和ARCACHE[2]为读分配位。

AWCACHE[3]和ARCACHE[3]为写分配位。

对于读交易,写分配位表示:

l由于一个写交易,位置能预先在高速缓存Cache中进行分配;

l由于其它主设备的行为,位置能预先在高速缓存Cache中进行分配;

对于写交易,读分配位表示:

l由于一个读交易,位置能预先在高速缓存Cache中进行分配;

l由于其它主设备的行为,位置能预先在高速缓存Cache中进行分配;

2.2.6.2AWCACHE[1]和ARCACHE[1]

AWCACHE[1]和ARCACHE[1]在AXI4中表示可修改位。

该位为1时,表示交易是可修改的,否则交易时不可修改的。

1.不可修改的交易

不可修改交易不能分割成多个交易或者与其它交易合并。

交易不可修改时,下面的参数是不可修改的:

传输地址(AWADDR,ARADDR,AWREGION,ARREGION)、猝发大小(AWSIZE,ARSIZE)、猝发长度(AWLEN,ARLEN)、猝发类型(AWBURST.ARBURST)、锁类型(AWLOCK,ARLOCK)、保护类型(AWPROT,ARPROT)。

不可修改交易中,交易ID和QoS值是可修改的。

对于猝发长度大于16的不可修改的交易,允许分割成多个交易。

每个产生的交易都满足上面的要求,但减少猝发长度,所产生的猝发地址也相应的修改。

2.可修改的交易

可修改的交易可以通过下面的方法进行操作:

l交易能分割成多个交易;

多个交易能合并成一个交易;l

读交易能取出比要求多的数据;l

l写交易能访问比要求更大的地址范围,使用写选通信号来保证只更新合理的位置;

可以修改每个产生交易的传输地址(AWADDR,lARADDR)、猝发大小(AWSIZE,ARSIZE)、猝发长度(AWLEN,ARLEN)、猝发类型(AWBURST.ARBURST)

但是不能修改锁类型(AWLOCK,ARLOCK)、保护类型(AWPROT,ARPROT)。

可修改交易中,交易ID和QoS值是可修改的。

2.2.6.3AWCACHE[0]和ARCACHE[0]

AWCACHE[0]和ARCACHE[0]表示可缓冲,当为低,AWCACHE[0]表示写响应由终端设备发出,否则可以有中间设备发出。

ARCACHE[0]表示读数据由终端设备发出或者由写的是最终目的地发出。

2.2.7AXI互联结构模型

其互联结构模型包括:

直通模式;只转换模式;N-1互联模式;1-N互联模式;N-M互联模式。

下面对这几种互联结构模型进行介绍:

1)直通模式

如图2.7所示,当只有一个主设备和一个从设备和AXI互联时,AXI互联不执行任何

转换或流水线功能,AXI互联结构退化成直接的线连接。

在这种模式下,没有延迟存在,同时不消耗逻辑资源。

2)只转换模式

如图2.8所示,当连接一个主设备和一个从设备时,AXI互联能执行不同的转换和流水线功能。

这些功能主要包括:

数据宽度转换;时钟速率转化;AXI4-Lite从适应;AXI-3从适应;流水线(例如一个寄存器Slice或者数据通道FIFO)。

在只转换模式下,AXI互联不包含仲裁、解码或布线逻辑,但是可能产生延迟。

3)N-1互联模式

如图2.9所示,AXI互联的一个普通的退化配置模式是,多个主设备访问一个从设备。

典型的情况是,一个存储器控制器,很显然需要仲裁逻辑。

这种情况下,AXI互联不需要地址译码逻辑(除非需要确认地址的有效范围)。

在这个配置中,也执行数据宽度和时钟速率的转换。

4)1-N互联模式

如图2.10所示,另一个AXI互联退化的结构是,一个主设备,典型的处理器,访问多个存储器映射的从外设。

在这种模式下,AXI互联不执行仲裁(在地址和写数据通道)。

5)N-M互联模式

AXI互联提供了一种共享地址多数据流(SAMD)拓扑结构,这种结构中包含稀疏的数

据交叉开关连接,单线程写和读地址仲裁。

如图2.11所示,给出了一种共享写和读地址仲裁的N-M的AXI互联结构。

图2.12给出一种稀疏互联开关写和读数据通路。

2.2.8用户信号

通常情况下,不推荐使用用户信号,因为在AXI4协议中没有定义它们的功能,这样两个元件在不兼容行为下使用相同的用户信号,可能导致互操作性问题。

下面给出每个AXI4通道的用户信号名字:

lAWUSER:

写地址通道用户信号;

ARUSER:

读地址通道用户信号;l

WUSER:

写数据通道用户信号;l

lRUSER:

读数据通道用户信号;

lBUSER:

写响应通道用户信号;

当实现用户信号时,并不要求所有通道支持用户信号。

此外,不希望在一个通用的主设备和从设备元件接口支持用户信号。

推荐,包含支持用户信号的互联元件允许这些信号在主设备和从设备之间进行传递。

用户信号的宽度在实现时定义,在每个通道的宽度可以不同。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- AXI4 功能

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx