电子创新实验室doc.docx

电子创新实验室doc.docx

- 文档编号:8805446

- 上传时间:2023-02-01

- 格式:DOCX

- 页数:36

- 大小:29.80KB

电子创新实验室doc.docx

《电子创新实验室doc.docx》由会员分享,可在线阅读,更多相关《电子创新实验室doc.docx(36页珍藏版)》请在冰豆网上搜索。

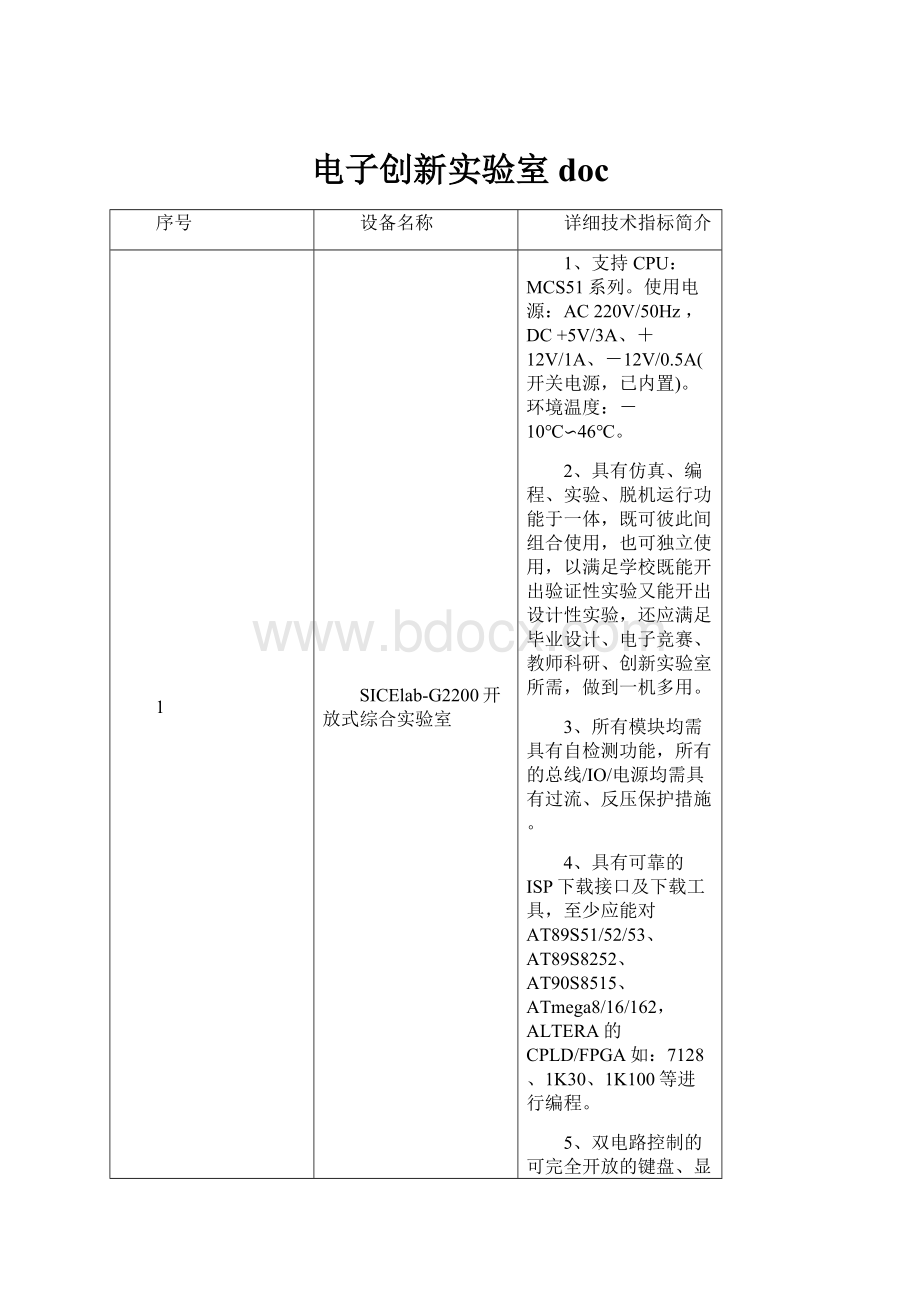

电子创新实验室doc

序号

设备名称

详细技术指标简介

1

SICElab-G2200开放式综合实验室

1、支持CPU:

MCS51系列。

使用电源:

AC220V/50Hz,DC+5V/3A、+12V/1A、-12V/0.5A(开关电源,已内置)。

环境温度:

-10℃∽46℃。

2、具有仿真、编程、实验、脱机运行功能于一体,既可彼此间组合使用,也可独立使用,以满足学校既能开出验证性实验又能开出设计性实验,还应满足毕业设计、电子竞赛、教师科研、创新实验室所需,做到一机多用。

3、所有模块均需具有自检测功能,所有的总线/IO/电源均需具有过流、反压保护措施。

4、具有可靠的ISP下载接口及下载工具,至少应能对AT89S51/52/53、AT89S8252、AT90S8515、ATmega8/16/162,ALTERA的CPLD/FPGA如:

7128、1K30、1K100等进行编程。

5、双电路控制的可完全开放的键盘、显示电路,既可满足实验过程中的输入数据、输出显示需要,又可满足由8155、8255、8279、ZLG7290等芯片控制键盘显示实验所需;

6、CPU所有管脚以自锁进插孔引出,设计有“自由实验”模块组,可进行芯片级的完全接线式实验,板上模块、扩展模块、“自由实验”模块之间可进行灵活的组合同时又能成为一个独立的应用系统。

7、集成以下新型实用模块:

1路USB1.0驱动电路和接口,16×16点阵LED广告屏,128×64点阵LCD模块,16X2字符式液晶模块,串行E2PROM24C02,串行时钟DS1302,串行模数转换TLC549,串行数模转换TLC5615,电机闭环控制电路,RS485通讯模块,接触式IC卡模块,

8、集成以下传感器模块:

温度传感器、压力传感器、霍尔开关传感器、红外线发射接收

9、集成以下传统实验模块:

AD0809并行AD;DAC0832并行DA;步进电机;直流电机;8255扩展;音频驱动电路;74LS138译码器;74LS373锁存电路;8个拔动开关;8个LED发光二极管;4×6键盘,矩阵方式也可接成直读方式,行扫描、列扫描开放;6个8段数码管,段码口、位码口开放;可2路电位器电压调节电路;信号发生器、信号分频器、逻辑笔。

10、集成以下接口电路:

RS232/RS485接口、通用打印机接口、128×64点阵LCD接口、16×2字符LCD接口、USB接口、2组供自检测使用的接口

11、提供详尽的使用手册、实验手册;提供配套的实验例程源程序(ASM51、C51);

提供波特率计算软件、汉字取模软件、串口监听软件、USB监听软件等各种工具软件;提供产品维护手册;提供产品各模块的原理图;提供免费培训服务。

仿真器:

1、具有完全自主版权的硬件和软件。

USB通信接口。

支持至少40个厂家的MCS51核单片机的仿真开发,包括增强的A/D、D/A、EXTRAM、EEPROM、I2C、SPI、PCA、ISP、PWM、双UART、双DPTR看门狗、CAN、USB、Lin和P4、P5、…、Pn功能。

2、保护措施完善,设计技术成熟,能保证仿真器长时间运行稳定可靠。

3、自动识别用户CPU,自动检测用户板工作电压。

4、可程控时钟,频率范围2K-100MHZ。

5、内置仿真头,仿真接口与真实芯片大小相等。

仿真频率50MHZ。

6、“双CPU”架构方式设计,无条件任意硬件断点,无限止夭折处理功能,完全不占用户资源。

支持P0,P2口的IO口方式和总线方式且可时分复用。

7、提供基于WINDOWS95/98/2000/XP/ME系统下的具有自主版权的一体化集成环境,同时可无缝支持KeilUv2/Uv3C51的仿真调试。

支持ASM、C语言及多模块混合源程序调试。

8、具有对包括T0、T1、INT0、INT1、TXD/RXD、P0-P3在内CPU级的模拟调试能力。

扩展模板:

1、常用电路模板:

可进行555实验、PWM实验;提供2组与门、非门、或门电路;提供LM324四运放,可搭建各种运放电路。

2、CAN总线与以太网模板:

CAN总线采用PHLIPSSJA1000,提供独立接口;以太网采用RTL8019AS,提供带变压器的接口。

3、语音录放/VF/FV转换模板:

语音录放采用ISD1420,带麦克风和喇叭;VF/FV采用LM331。

4、12位模数转换模板:

转换芯片采用AD574,提供8路通道。

2

KX-DN8电子创新实验系统平台

自从1994年的第一届全国大学生电子设计竞赛至今,参赛的学校的数量、竞赛的规模、竞赛形式类型以及受重视的程度都在不断扩大和提高。

这与大学生的培养目标、人才市场的需求和就业形势等因素是密切相关的。

显然,电子系统设计技能的提高不是一个抽象的概念,培养卓越工程师也不是一句空话,它必须与当前电子产品市场需求和人才市场需求这两个因素紧密相连。

这就是说,电子设计技能培训的内容应该与这两个因素挂钩,而不是仅仅通过学学焊接、画画PCB板,或用单片机及74系列器件设计某个功能模块来提高所谓的“动手能力”。

能为学生的就业与深造提供强大资本的电子设计能力及自主创新能力必须来自合理实验内容的安排和符合现代电子技术发展的技能培训。

它们必须包含这样的内容:

具有培养自主创新精神和拥有自主知识产权系统设计能力训练。

例如用一个传统单片机完成一项设计、用一个现成的蓝牙完成一项应用设计、用一个USB器件完成一项数据通信设计、利用ARM完成一项系统设计等等。

尽管这些系统设计的技能也重要,但是都是基于现成电路器件完成的,设计者只能说是被动应用了别人知识产权来完成设计,是一种非自主性设计。

至少,这类设计谈不上拥有自主知识产权。

因而仅这些技能在个人的可持续发展及就业口径上就有了先天的限制。

从传统的非自主性系统设计能力向自主性设计能力培养转化和发展十分重要。

从最近几届电子设计竞赛的赛题中也能看到这种转向。

诸如EDA、单片机、DSP、SOPC等传统实验平台多数是整体结构型的,虽也可完成多种类型实验,但由于整体结构不可变动,故实验项目和类型是预先设定的、固定的,很难有自主发挥的余地;学生的创新思想与创新设计如果与实验系统的结构不吻合,便无法在此平台上获得验证;同样,教师若有新的联系教学实际的实验项目,也无法融入固定结构的实验系统供学生实验。

因此,此类实验平台不具备可持续发展的潜力,没有自我更新和随需要升级的能力,用几年后只能被淘汰。

模块自由组合型创新设计综合实验开发系统很好地解决了这些问题,因此成为高校目前十分流行的实践平台,特点有:

◆由于系统的各实验功能模块可自由组合、增减,故不仅可实现的实验项目多,类型广,更重要的是很容易实现形式多样的创新设计;

◆由于各类实验模块功能集中,结构经典,接口灵活,对于任何一项具体实验设计都能给学生独立系统设计的体验,包括脱离系统平台;

◆面对不同的专业特点,不同的实践要求和不同的教学对象,教师,甚至学生自己可以动手为此平台开发增加新的实验和创新设计模块;

◆由于系统上的各接口,以及插件模块的接口都是统一标准的,康芯提供所有接口电路,因此此系统可以通过增加相应的模块而随时升级;

康芯的KX-DN型模块化综合创新实验开发系统的课程/实验设计类型有以下9类:

EDA技术系列实验。

配套教材2、4。

如教材1含60多个经典和创新实验与设计项目,多数含源程序演示示例。

SOPC技术系列实验。

配套教材7。

含基于CycloneIII等FPGA的SOPC实验,包括源程序演示示例。

单片机技术系列实验。

配套教材3。

可完成许多传统和现代的单片机实验,特别包括与FPGA接口的实用系统设计实验项目。

基于单片机IP核的SOC片上系统设计系列实验。

配套教材3。

基于FPGA硬件平台的8051核系统设计,含源程序演示示例。

数字电路系列实验。

配套教材5。

含数十相关实验,特别是基于QuartusII原理图和FPGA的数字电路实验。

基于DSPBuilder和MATLAB的DSP系列实验。

配套教材2。

数十个基于DSPBuilder和MATLAB的硬件DSP系列实验设计项目。

计算机组成与设计系列实验。

配套教材1。

基于配备的大规模FPGA和各类接口设备,成为计算机组成与设计创新实验的最好选择。

微机原理与接口技术系列实验。

配套教材6。

基于大规模FPGA和各类接口设备,在一单片中能完成微机接口所有创新实验。

电子设计竞赛系列项目开发训练。

作为电子设计训练平台,以其极大的灵活性和实用性,比传统固定结构的实验系统更能胜任此项任务。

(1)KX-DN8型

特色与优势:

该实验开发系统的最大特色是,由针对不同实验开发目标的各类功能模块组成。

每一个模块可以在实验系统上完成各类设计,也可脱离实验系统单独完成功能,使实验者能从中体会和获得实际工程开发完整经历。

可以根据实验需要和电子设计训练科目分别完成各功能模块的实验与自主开发、也可将不同模块组合成一个大系统进行综合设计开发,培养学生的自主性综合实验开发能力,以及拥有自主知识产权的系统和片上系统设计开发能力。

本系统提供的专业CPUIP核、各类功能IP核以及基于大规模FPGA(CycloneIII系列)的可自主配置重构型DDS函数信号发生器是培养自主创新设计能力的重要电子系统设计训练平台。

KX_DN8系统包含的实验开发模块如下:

模块1:

MCS-51单片机模块。

可对AT89S51、AT89S52、AT89S8253等单片机进行实验开发,可对不同模块进行编程控制(配STC89S51)。

模块2:

FPGA模块可运行单片机IP核的FPGA模块。

CycloneIIIEP3C55F484(484脚BGA封装),内部资源极其丰富:

5万6千个逻辑宏单元、240万RAMbit;其他内部资源和技术指标好于EP3C40;接口器件有32MBSDRAM、1GB并行Flash、2M串行Flash16M配置Flash、1/2GBSD卡;此系统能运行完整的8086微机SOC片上系统,其内部SRAM能放下BIOS启动ROM、显示缓存、PS2缓存等,能启动MS-DOS操作系统,在VGA显示器上用PS2键盘能完成MS-DOS命令和WINDOWS及运行传统软件,如TURBOC,QBASIC等等。

为SOC片上系统的学习与创新设计提供了绝好的平台。

提供多种IP核:

32位NiosII核、20MHz有源晶振等。

包含8051/52IP核。

提供商业级全兼容MCS-51单片机IP核。

利用此核,实验者可以实现传统单片机实验系统无法达到的SOC(片上系统)设计。

即将单片机CPU、RAM、ROM以及其它各类接口电路模块设计在同一片FPGA中。

此类技术对于对于面向高新技术企业的就业十分必要。

8088、8086CPUIP核。

8255AIP核模块;8255AIP核(I/O接口);8253/8254IP核(定时器);8250IP核(UART串行通信);8237IP核(DMA控制器);8259IP核(可编程中断控制器),以及基于FPGA的RAM/ROM核、锁相环核等。

这些IP核与8088CPU核相结合就能在单片FPGA中构成一个微机系统,从而学习到实用的SOC设计工程技术。

FPGA中的8088核与MCS-31单片机核及其中的各种模块和核都能与以下各模块结合,实现不同类型的实验开发。

模块3:

点阵型液晶显示屏。

128X64液晶显示屏,含清华大学学生在此系统上利用FPGA中的IP核及液晶显示屏完成的自主设计实验演示项目(俄罗斯方块游戏),或用单片机控制液晶显示实验。

此模块有两个输入端口,一个端口可以直接与FPGA相接,通过这种方式可以学习数字逻辑直接控制点阵液晶的显示,这有一定的挑战性;另一端口是FPGA通过一片单片机控制液晶(此模块含义单片机),可以通过这个接口完成一些实验,还能通过这个接口显示计算机组成原理设计项目的一些实验结果。

模块4:

字符型液晶显示屏。

4行X20字液晶显示屏幕,此液晶显示屏可作为实验模块,同时兼实验系统上的DDS函数信号发生器工作显示屏。

模块5:

A/D与D/A模块。

A/D是0809、D/A是双通道DAC0832,故能实现移相信号发生器、里萨如图形信号发生器、存储示波器、逻辑分析仪等电路模型的设计实验。

模块6:

SD+PS2+RS232+VGA显示接口模块。

含VGA显示接口、PS/2鼠标键盘接口、RS232串行通信接口、SD卡接口。

可用FPGA进行图像设计和通信

模块7:

电机模块。

含直流电机和步进电机,控制电路,红外转速计数电路等,可完成PWM控制转速等实验。

模块8:

无线遥控编码收发+数字温度测控模块。

无线编码收发,可键控或单片机控制,2272和2262系列器件担任编译码,315MFSK调制,PT2272编码接受,PT2267编码发射,不同天线对应不同通信距离,单片机或FPGA可控进行编码实验。

数字温度传感器是DS18B20。

模块9:

4个数码管扫描、7段控制显示,加语音采样、处理和立体声输出模块。

模块10:

串行静态显示模块。

7数码管串行静态显示模块,可用于串行显示的实验。

模块11:

HEX译码显示模块。

6位16进制译码数码显示。

适合于基于FPGA的CPU实验。

模块12:

4X4键盘和单脉冲8键键盘模块,学习用单片机对键盘扫描实验,或FPGA对单脉冲按键实验,完成消抖动实验。

模块13:

USB通信实验开发模块,可对PC机和FPGA通信。

模块14:

继电器+CAN总线+RS485串口模块

模块15:

SRAM+EPROM实验模块

模块16:

双串行存储器+逻辑笔设计模块

模块17:

看门狗定时器+时钟日历模块

模块18:

4X4键盘,可作为一般实验用,也可作为配套的DDS函数信号发生器使用。

模块19:

DDS模块。

含isp单片机AT89S8253,MCS51兼容单片机,12KBisp可编程FlashROM,2KBispEEPROM,10万次烧写周期;2.7-5.5V工作电压;0-24MHz工作时钟;可编程看门狗;增强型SPI串口,9个中断源等;EP1C3T144FPGA、EPCS1配置Flash、超高速DAC5651(上限180MHz)、260MHz超高速运放等。

此模块可以DDS函数信号发生器主控模块,也可作为一个独立的自主设计模块,使用高速DAC和运放等器件完成各种不同自主创新型设计实验。

既可用作功能强大的全数字型DDS函数信号发生器,同时也可作为EDA/DSP系统及专业级DDS函数信号发生器设计开发板。

作为DDS函数发生器的功能主要包括:

等精度频率计,扫频信号源,移相信号发生,里萨如图信号发生,方波/三角波/锯齿波和任意波形发生器,以及AM/PM/FM/FSK/ASK/FPK等各类调制信号发生器。

模块20:

以太网口模块。

在以上KX_DN5的基础上增加如下模块:

模块21ProGinSR879600GPS实验开发模块。

可用普通单片机控制显示,也可用FPGA中的单片机IP核,或8088核进行控制。

模块22超高速A/D、D/A模块。

含180MHz转换时钟率双路高速10位DAC、50MHz单通道高速8位ADC、300MHz高速运放等。

模块23800X480数字TFT彩屏。

模块2416位高分辨率ADCADS110016模块,高分辨率ADC模块。

含ADS110016位高分辨率ADC,低功耗、自动校正功能,I2C串行接口。

模块25高速12位SPI串行ADCTLV2541模块,高速12位SPI串行ADCTLV2541模块,200ksps,SPI接口;体积小功耗低,无需高压电源。

FPGA和单片机都能将其作为接口扩展器件。

模块26双通道10位QSPI/SPI/DSP串行接口高速DACTLV5637模块,DACTLV5637,双通道10位QSPI/SPI/DSP串行接口高速DAC,片内可编程参考电压,可编程转换速率控制。

此模块更适用于基于FPGA的DSP模块设计开发。

模块2732位二进制译码显示模块,即含8个数码管,分别译码显示8个16进制(包括BCD码)输入数据。

模块2832位二进制数输出/显示数控模块,即含8个数码管,分别显示输入FPGA的32位数据。

KX_DN8系统还包含如下工具性功能模块:

KX_USB-Blaster2型双功能编程器:

(1)USB-Blaster编程下载功能(支持AS、PS、JTAG模式):

1、对FPGA/CPLD进行配置或编程;2、对配置器件EPCSx编程;3、访问和编辑FPGA内部RAM;4、调试Nios2,完成SOPC设计;5、支持SignalTapII嵌入式逻辑分析仪。

(2)USB到UART串行通信转换:

1、通过USB与FPGA串行通信,实现PC与FPGA的串行通信,且无需RS232电平转换;2、通过USB与单片机的串行通信,实现PC与通用单片机的UART串行通信;3、通过USB对STC等系列单片机进行直接编程开发,无需电平转换。

ByteBlasterMV编程器一个(可对isp单片机编程)。

5功能智能逻辑笔:

可显示高电平、低电平、中电平、高阻态、脉冲信号。

注意有“高阻态”测试功能。

独立的标准时钟频率20个。

20MHZ-0.5HZ。

电源有自动保护的+5V,+12V、-12V、、+3.3V、2.5V+、1.2V。

8个LED放光二级管,8个乒乓开关。

KX_DN系统部分实验

一针对HDL设计的EDA基本实验与设计

实验1-1.计数器设计实验4-2.多路选择器设计

实验1-3.8位全加器设计实验4-4.原理图输入法设计频率计

实验1-5.十六进制7段数码显示译码器设计

实验1-6数码扫描显示电路设计

实验1-7半整数与奇数分频器设计

实验1-8模可控计数器设计

实验1-9VGA彩条信号显示控制电路设计

实验1-10移位相加型8位硬件乘法器设计

实验1-11移位寄存器设计

实验1-12串行静态显示控制电路设计

1.2针对LPM宏模块应用的EDA实验与设计

实验1-13.查表式硬件运算器设计

实验1-14.正弦信号发生器设计

实验1-15.八位数码显示频率计设计

实验1-16.简易逻辑分析仪设计

实验1-17.DDS正弦信号发生器设计

实验1-18.移相信号发生器设计

实验1-19.4X4阵列键盘键信号检测电路设计

实验1-20.VGA简单图像显示控制模块设计

实验1-21SPWM脉宽调制控制系统设计

实验1-22基于DES数据加密标准的加解密系统设计

实验1-23线性反馈移位寄存器设计

实验1-24步进电机细分控制电路设计

实验1-25基于FT245BM的USB通信控制模块设计

实验1-26直流电机综合测控系统设计

实验1-27VGA动画图像显示控制电路设计

实验1-28AM幅度调制信号发生器设计

1.3针对状态机应用的EDA实验与设计

实验1-29序列检测器设计

实验1-30ADC采样控制电路设计

实验1-31数据采集模块设计

实验1-32五功能智能逻辑笔设计

实验1-33比较器加DAC器件实现ADC转换功能电路设计

实验1-34通用异步收发器UART设计

实验1-35点阵型与字符型液晶显示器驱动控制电路设计

实验1-36串行ADC/DAC控制电路设计

实验1-37硬件消抖动电路设计

实验1-38数字彩色液晶显示控制电路设计

实验1-39状态机控制串/并转换8数码静态显示电路设计

实验1-40基于CPLD的FPGAPS模式编程配置控制电路设计

实验1-41基于FPGA的红外双向通信电路设计

1.4EDA综合实验与设计

实验1-42乐曲硬件演奏电路设计

实验1-43正交幅度调制与解调系统实现

实验1-44基于UART串口控制的模型电子琴设计

实验1-45基于M9KRAM型LPM移位寄存器设计

实验1-46单片全数字型DDS函数信号发生器综合设计

实验1-47乒乓球游戏电路设计

实验1-48PS2键盘控制模型电子琴电路设计

实验1-49GPS应用的通信电路设计

实验1-50在ModelSim上进行4位计数器仿真

实验1-51在ModelSim上进行16位累加器设计仿真

二SOPC实验与设计

实验2-1基于SOPC的多功能数字钟设计

实验2-2彩色液晶显示控制电路设计

实验2-3基于NiosII的直流电机控制

实验2-4自定制硬件乘法器

实验2-5硬件乐曲演播系统设计

实验2-6基于UART的I2C总线传输

实验2-7基于NiosII的等精度频率计设计

三单片机系统综合实验

3.1单片机基本实验

实验3-1.存储器块清零程序设计

实验3-2二进制到BCD转换程序设计

实验3-3十六进制到ASCII码转换程序设计

实验3-4存储块移动程序设计

实验3-5多分支程序

实验3-6数据排序程序设计

实验3-7P1口输入、输出实验

实验3-8交通灯控制(软件延时法)

实验3-9交通灯控制(定时器延时法).

实验3-10计数器应用实验

实验3-11外部中断实验

实验3-12定时器实验1(P1口状态取反)

实验3-13定时器输出PWM实验

实验3-14外部中断实验

3.2单片机扩展和接口实验与设计

实验3-15单片机串口扩展

实验3-16键盘与液晶显示控制

实验3-17单片机串行通信和红外双向通信

实验3-18单片机扩展X5045看门狗器件

实验3-19单片机扩展DS1302时钟/日历器件

实验3-20SPI串行DACTLV5637与单片机的接口

实验3-21串行精密ADC器件ADS1100与单片机的接口

实验3-22串行高速ADC器件ADS7816与单片机的接口

实验3-23高速微功耗串行ADC器件TLV2541与单片机的接口

实验3-24双通道A/D转换芯片ADC0832与单片机的接口

实验3-25高速同步10位串行A/D转换器与单片机的接口

四单片机扩展FPGA综合实验与设计

实验4-1单片机串行扩展FPGA系统设计

实验4-2单片机数据交换FPGA扩展电路设计

实验4-3扩展外部数据存储器的单片机与FPGA扩展系统设计

实验4-4四通道PWM信号发生器及其单片机控制系统设计

实验4-5移相信号发生器的FPGA与单片机扩展系统设计.

实验4-6里萨如图波形发生器的单片机与FPGA扩展系统设计.

实验4-7数字电压表FPGA单片机的系统设计

实验4-8数字频率计与单片机串行通信接口功能设计

实验4-9直流电机测控单片机与FPGA扩展系统设计

实验4-10等精度频率/脉宽/占空比/相位多功能测试仪设计

五基于单片机IP核的FPGA片上系统SOC设计..

实验5-1.单片机串口扩展FPGA片上系统SOC设计

实验5-2.扩展外部数据存储器的FPGA单片系统设计

实验5-3.四通道PWM信号发生器及单片系统设计

实验5-4.移相信号发生器的FPGA片上系统SOC设计

实验5-5.里萨如图波形发生器的FPGA片上系统设计

实验5-6.数字电压表FPGA单片系统SOC设计

实验5-7.数字频率计与单片机串行通信接口功能设计

实验5-8.直流电机测控FPGA单片系统设计

实验5-9.等精度频率计FPGA单片系统设计

实验5-10.基于FPGA的红外双向通信单片系统设计

3

GW-PK-2AS-EDA/SOPC开发实验系统

一、主系统GW48-PK2技术指标:

1.含USB-BlasterJTAG编程下载器,和ByteblasterⅡ与ByteblasterMV编程下载器,对6大FPGA/C

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 电子 创新 实验室 doc

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

1212中级汽车维修工考试试题三.docx

1212中级汽车维修工考试试题三.docx