0101110序列检测器仿真Word格式.docx

0101110序列检测器仿真Word格式.docx

- 文档编号:21912746

- 上传时间:2023-02-01

- 格式:DOCX

- 页数:11

- 大小:687.97KB

0101110序列检测器仿真Word格式.docx

《0101110序列检测器仿真Word格式.docx》由会员分享,可在线阅读,更多相关《0101110序列检测器仿真Word格式.docx(11页珍藏版)》请在冰豆网上搜索。

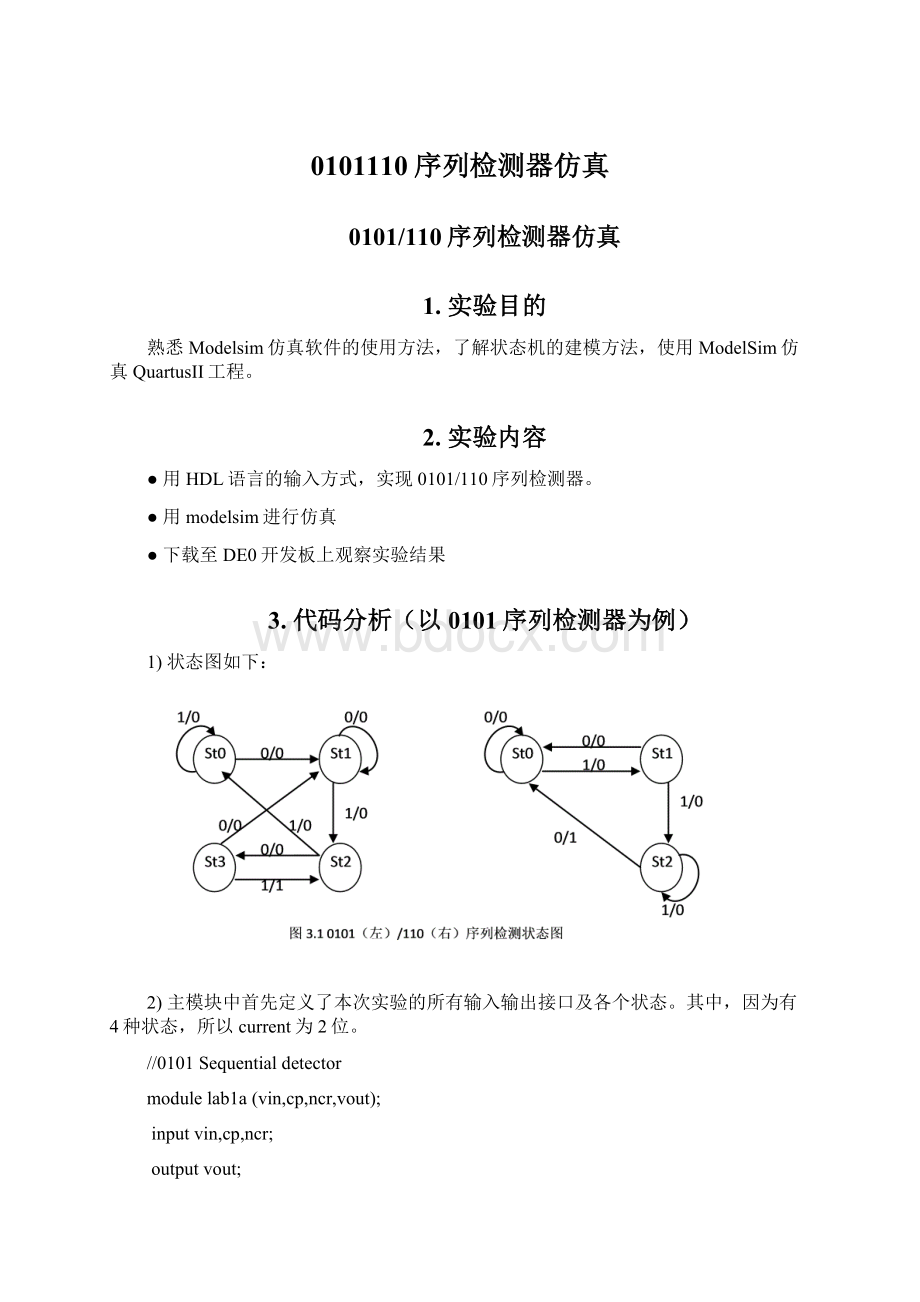

2)主模块中首先定义了本次实验的所有输入输出接口及各个状态。

其中,因为有4种状态,所以current为2位。

//0101Sequentialdetector

modulelab1a(vin,cp,ncr,vout);

inputvin,cp,ncr;

outputvout;

regvout;

reg[1:

0]current,next;

parameters0=2'

b00,s1=2'

b01,s2=2'

b10,s3=2'

b11;

3)然后设置异步清零,在cp上升沿则沿触发器状态翻转。

always@(posedgecpornegedgencr)

begin

if(~ncr)

current<

=s0;

else

=next;

end

4)接着编写组合逻辑部分,设定下一状态产生和输出的信号。

always@(currentorvin)

next=2'

bxx;

case(current)

s0:

beginnext=(vin==1)?

s0:

s1;

s1:

s2:

s2:

s3;

s3:

endcase

5)最后为输出部分,本程序中设置让输出信号经过一个寄存器再输出,可以消除vout信号中的毛刺。

if(~ncr)vout=1'

b0;

else

vout=1'

s0,s1,s2:

vout=1'

if(vin==1)vout=1'

b1;

elsevout=1'

endmodule

6)测试模块中同样先定义了各个变量,并将它们与主模块一一对应后进行初始化。

moduletest();

regcp,clr,en;

wireq;

lab1ad(.cp(cp),

.ncr(clr),

.vin(en),

.vout(q));

initial

cp=0;

clr=0;

en=0;

7)接着设置各信号波形:

clr在20个单位时间后变为1,en的数据变为有效,cp,,en则分别在每10个和16个单位时间翻转一次。

在420个单位时间后仿真停止。

#20clr=1;

#400$stop;

always#10cp=~cp;

always#16en=~en;

4.实验步骤

1)打开Modelsim,出现欢迎界面

点击Jumpstart

点击CreateaProject新建一个工程

设置好工程名和路径后点击OK

点击CreateNewFile

选择文件类型为Verilog

双击文件名,写好程序后用右键单击文件,选择CompileAll

成功后,文件名右边的Status会变为打钩

2)选择Simulate=>

StartSimulation

选择所需的的测试文件

点击OK后如下图

点击View=>

Wave

在Object中添加信号

然后点击RunAll开始仿真

5.实验结果的测试和分析

0101序列检测器的仿真图形如下:

110序列检测器的仿真图形如下:

检验后结果正确。

6.实验总结

通过这次试验,我明白了序列检测器的原理以及Modelsim的基本使用方法。

7.参考文献

1)源代码:

《VerilogHDL与数字ASIC设计基础》华中科技大学出版社

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 0101110 序列 检测器 仿真

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx