指导书EDA实验.docx

指导书EDA实验.docx

- 文档编号:8822802

- 上传时间:2023-02-01

- 格式:DOCX

- 页数:24

- 大小:112.90KB

指导书EDA实验.docx

《指导书EDA实验.docx》由会员分享,可在线阅读,更多相关《指导书EDA实验.docx(24页珍藏版)》请在冰豆网上搜索。

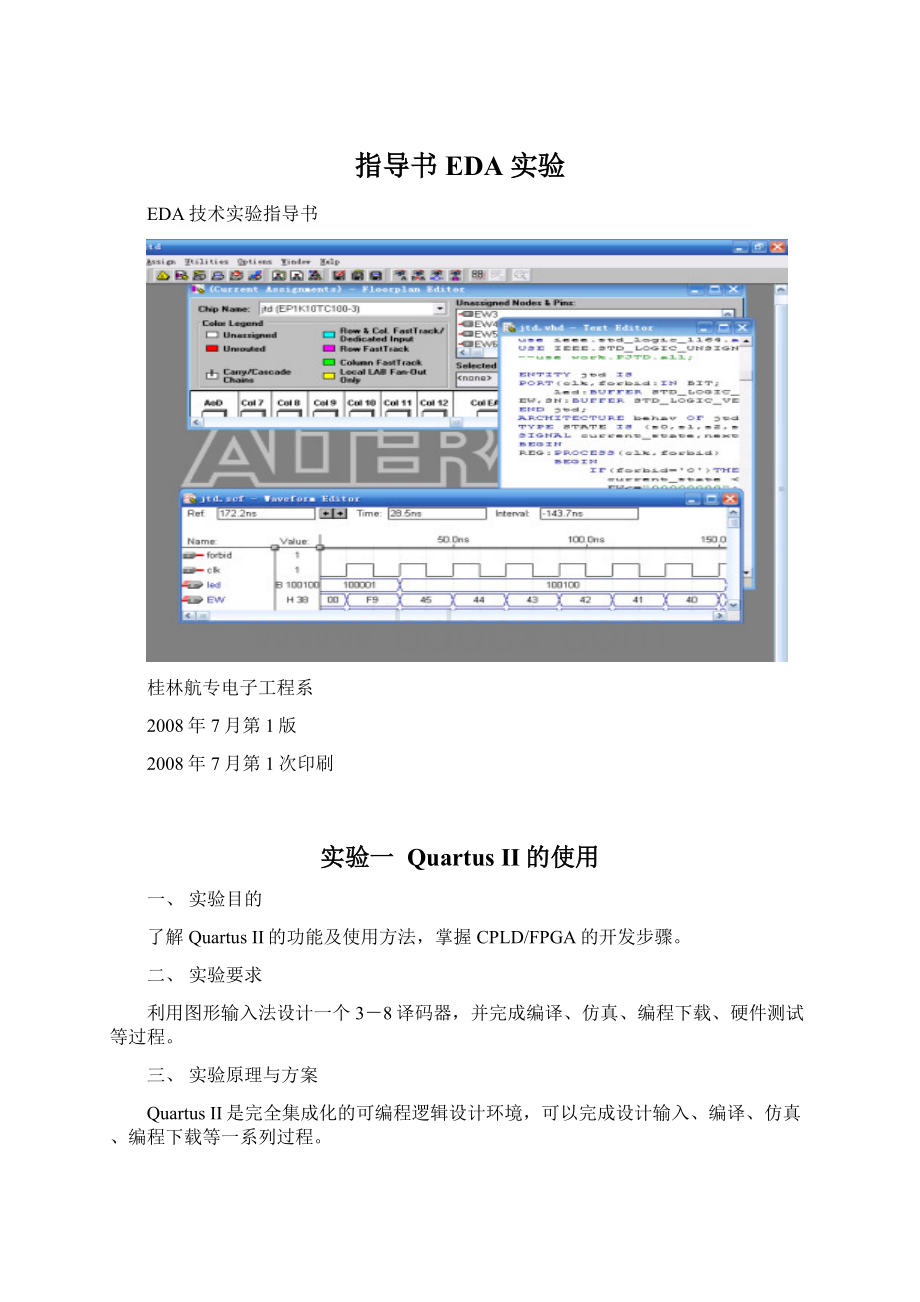

指导书EDA实验

EDA技术实验指导书

桂林航专电子工程系

2008年7月第1版

2008年7月第1次印刷

实验一QuartusII的使用

一、实验目的

了解QuartusII的功能及使用方法,掌握CPLD/FPGA的开发步骤。

二、实验要求

利用图形输入法设计一个3-8译码器,并完成编译、仿真、编程下载、硬件测试等过程。

三、实验原理与方案

QuartusII是完全集成化的可编程逻辑设计环境,可以完成设计输入、编译、仿真、编程下载等一系列过程。

在QuartusII中可采用原理图输入法进行设计,即先为工程建立一个文件夹,然后在原理图输入窗口调入所用元件,连线后得到正确的设计原理图,然后再进行编译、排错、仿真、下载等操作。

在建立文件夹时注意名字不能使用中文,且不可含有空格。

在调用元件时要用到三个元件库,位于\maxplus2\max2lib路径下。

其中prim库为基本逻辑元件库,包含基本门电路、输入输出符号等;mf为宏功能元件库,主要包含74系列门电路等;mega_lpm为参数可变的兆功能元件库,含有计数器等逻辑部件。

在编译时要先将设计文件设置成“工程”(setprojecttocurrentfile),还要选择目标器件,本实验中使用的器件为ACEX系列的ACEX-EP1K10TC100-3。

QuartusII的编译器(compiler)包含了一般EDA流程中的多个功能部分,编译器窗口中各功能模块的含义如下:

compilernetlistextractor:

是编译器网表文件提取器,能将输入的原理图文件或HDL文件转换成网表文件,并检查其中可能的错误。

该模块还负责连接顶层设计中的多层次设计文件,另外还包含一个内置的、用于接受外部标准网表文件的阅读器。

Databasebuilder:

是基本编译文件建立器,能将含有任何设计层次的设计网表文件转换成一个单一层次的网表文件,以便进行逻辑综合。

Logicsynthesizer:

是逻辑综合器,对设计项目进行逻辑化简、逻辑优化和检查逻辑错误。

综合后输出的网表文件表达了设计项目中底层逻辑元件最基本的连接方式和逻辑关系。

逻辑综合器的工作方式和优化方案可以通过一些选项来实现,具体方法请查阅相关书籍。

Partitioner:

是逻辑分割器,如果选定的目标器件资源太小,容纳不下设计项目,该分割器则自动将设计项目进行分割,使得它们能够在多个器件中实现。

Fitter:

是适配器,或者说是结构综合器或布局布线器,它将逻辑综合所得的网表文件,即底层逻辑元件的基本连接关系,在选定的目标器件中具体实现。

对于布局布线器的策略和优化方式也可以通过设置一些选项来改变和实现。

Timingsnfextractor:

是时序仿真网表文件提取器,该功能块从适配器输出的文件中提取时序仿真网表文件,以对设计项目进行仿真测试用。

对于大的设计项目,一般先进行功能仿真,方法是在compiler窗口下选择processing项中的functionsnfextractor选项。

仿真网表文件(snf)是仿真时的必需文件,除此以外在仿真前还要设计一个仿真通道文件(scf),用以确定要观察的输入输出信号。

设计仿真通道文件要在file菜单的new选项中选择waveformeditorfile。

Assembler:

是装配器,能将适配器输出的文件,根据不同的目标器件、不同的配置ROM产生多种格式的编程/配置文件,如用于CPLD或配置ROM用的POF编程文件,用于对FPGA直接配置的SOF文件,用于单片机对FPGA配置的Hex文件等。

编译通过的设计项目是否能完成预期的逻辑功能,可以通过仿真来验证,主要步骤如下:

(1)建立仿真通道文件(SCF)。

(2)输入信号节点。

(3)设置仿真参数。

一般首先选择菜单option\snaptogrid取消前面的“√”,以便能任意设置输入电平或设置输入时钟信号的周期。

(4)设定仿真时间。

(5)设置输入信号波形。

(6)保存波形文件。

(7)运行仿真器。

选择主菜单QuartusII\simulator,单击start按钮。

(8)观察波形。

(9)延时精确测量。

若要精确测量电路的输入与输出的延时,可选择主菜单QuartusII\timinganalyzer。

在仿真通过后,可以对器件进行编程和硬件测试。

在编程前要完成目标芯片的引脚锁定,并重新编译。

引脚锁定的方法是选择菜单assign\pin\location/chip。

编程时要用下载电缆线把计算机并行口(打印口)与目标板(实验板)连接起来,选择主菜单QuartusII\programmer,再选择菜单options\hardwaresetup,选择byteblaster(mv)编程方式。

在编程器窗口中单击configure按钮,如果没有故障会出现配置完成的信息提示,表明编程(配置)完毕,之后就可以进行硬件测试了。

本实验的电路方案可参考下图:

四、实验内容、步骤与结果

1、建立文件夹:

E:

\2005045101XX。

2、启动QuartusII,打开图形编辑器输入设计并存盘。

3、项目编译

1)将设计文件设成项目。

2)选择目标器件:

ACEX-EP1K10TC100-3。

3)参数设置:

取默认值。

4)编译。

4、时序仿真

1)建立波形文件:

*.SCF。

2)参数设置。

3)打开仿真窗口并”START”。

4)查看仿真结果

请记录仿真波形,并添加到实验报告中。

5、器件编程

1)连好电缆,锁定引脚并重新编译。

2)打开“PROGRAMER”窗口。

3)选择编程/配置目标文件(*.POF/SOF)。

4)点击“PROGRAM”或”CONFIGURE”。

6、硬件测试。

请说明测试方法并记录测试结果,在实验报告中写出。

五、实验结果分析与结论

1、QuartusII的基本功能和一般操作步骤。

2、原理图文件的建立方法。

3、仿真的方法。

4、其它。

实验二组合电路设计

一、实验目的

了解VHDL程序的一般结构及组合电路的设计方法。

二、实验要求

利用VHDL设计一个3-8译码器,并完成设计输入、编译、仿真、硬件测试等过程。

三、实验原理与方案

VHDL程序通常包含库(Library)、程序包(Package)、实体(Entity)、结构体(Architecture)、配置(Configuration)5个组成部分,其中实体和结构体是VHDL程序不可缺少的最基本的2个组成部分。

在QuartusII环境下,VHDL程序可以通过文本编辑器(TextEditor)编辑,方法是打开QuartusII,选择菜单file\new,选中texteditorfile选项,进入文本编辑器界面,在其中进行录入编辑等。

编辑完毕后要保存文件,保存文件时要注意存放路径必须是事先建立好的用于存放工程(Project)的文件夹,VHDL程序的文件名必须与实体名相同,扩展名必须为.vhd,例如decode38.vhd。

对采用VHDL描述的电路设计除了设计输入方式与原理图描述不同外,其余的设计步骤均相同。

组合电路的特点是电路任一时刻的输出仅与当时的输入有关,而与以前的状态无关,或者说只要输入变化,输出就变化。

组合电路的设计只需注意如果采用条件语句,一定要采用完整的条件语句,如下面的参考程序中的IF_THEN_ELSE程序结构。

对于本实验,下面的程序可供参考:

libraryieee;

useieee.std_logic_1164.all;

entitydecode38is

port(g1,g2a,g2b:

instd_logic;

a,b,c:

instd_logic;

y:

outstd_logic_vector(7downto0));

enddecode38;

architecturebehaveofdecode38is

signalindata:

std_logic_vector(2downto0);

begin

indata<=c&b&a;

process(indata,g1,g2a,g2b)

begin

if(g1=’1’andg2a=’0’andg2b=’0’)then

caseindatais

when“000”=>y<=”11111110”;

when“001”=>y<=”11111101”;

when“010”=>y<=”11111011”;

when“011”=>y<=”11110111”;

when“100”=>y<=”11101111”;

when“101”=>y<=”11011111”;

when“110”=>y<=”10111111”;

when“111”=>y<=”01111111”;

whenothers=>y<=”XXXXXXXX”;

endcase;

else

y<=”11111111”;

endif;

endprocess;

endbehave;

四、实验内容、步骤与结果

1、建立文件夹:

E:

\2005045101XX。

2、启动QuartusII,打开文本编辑器输入设计并存盘。

3、项目编译

1)将设计文件设成项目。

2)选择目标器件:

ACEX-EP1K10TC100-3。

3)参数设置:

取默认值。

4)编译。

4、时序仿真

1)建立波形文件:

*.SCF。

2)参数设置。

3)打开仿真窗口并”START”。

4)查看仿真结果

请记录仿真波形,并添加到实验报告中。

5、器件编程

1)连好电缆,锁定引脚并重新编译。

2)打开“PROGRAMER”窗口。

3)选择编程/配置目标文件(*.POF/SOF)。

4)点击“PROGRAM”或”CONFIGURE”。

6、硬件测试

请说明测试方法并记录测试结果,在实验报告中写出。

五、实验结果分析与实验结论

1、根据仿真及硬件测试结果说明是否达到了设计要求。

2、VHDL程序的基本结构。

3、组合电路的设计方法。

4、其它。

实验三VHDL的并行语句

一、实验目的

掌握VHDL中并行语句的特点、功能和使用方法;进一步熟悉MAXPLUSII的使用方法。

二、实验要求

用选择信号赋值语句或条件信号赋值语句设计一个2线-4线译码器,并完成设计输入、编译、仿真等过程。

三、实验原理与方案

VHDL的基本描述语句分成顺序语句和并行语句两大类。

顺序语句只能包含在进程中,并行语句直接出现在结构体中。

在结构体中的并行语句的执行是同步的,与书写顺序无关。

选择信号赋值语句和条件信号赋值语句属于并行语句,它们的格式如下:

选择信号赋值语句:

WITH选择表达式SELECT

赋值目标信号<=表达式1WHEN选择值1,

表达式2WHEN选择值2,

…

表达式nWHEN选择值n;

选择信号赋值语句不能在进程中应用,但其功能与进程中的CASE语句相似。

选择信号语句中也有敏感量,即关键词WITH后的选择表达式,每当选择表达式的值发生变化时,就将自动对各子句的选择值进行测试对比,并将满足条件的子句对应的表达式的值赋给目标信号。

选择信号赋值语句对各子句中选择值的测试具有同期性,因此,不允许有条件重叠或条件覆盖不全的情况。

条件信号赋值语句:

赋值目标信号<=表达式1WHEN赋值条件1ELSE

表达式2WHEN赋值条件2ELSE

…

表达式n;

在结构体中的条件信号赋值语句的功能类似进程中的IF语句,在执行条件信号语句时,每一赋值条件是按书写的先后关系逐项测定的,一旦发现赋值条件为真,立即将对应的表达式的值赋给目标信号。

由此可知,条件信号语句的赋值条件允许有重叠现象,这与CASE语句有很大的不同。

注意选择信号赋值语句的每一子句结尾都是逗号,最后一句是分号;而条件赋值语句每一子句的结尾没有任何标点,只有最后一句有分号。

2线-4线译码器是2个输入、4个输出的组合电路,假设输入信号为b、a,输出信号为y0-y3,则其真值表如表3-1所示:

表3-12线-4线译码器的真值表

ba

y0y1y2y3

00

0111

01

1011

10

1101

11

1110

下面是使用选择信号赋值语句的示例程序,可供实验参考。

libraryieee;

useieee.std_logic_1164.all;

entitydecode24is

port(a,b:

instd_logic;

y:

outstd_logic_vector(0to3));

enddecode24;

architecturertlofdecode24is

signalindata:

std_logic_vector(1downto0);

begin

indata<=b&a;

WITHindataSELECT

y<=”0111”when“00”,

”1011”when“01”,

”1101”when“10”,

”1110”when“11”,

”XXXX”whenothers;

endrtl;

四、实验内容、步骤与结果

(一)使用选择信号赋值语句实现实验要求

1、建立文件夹:

E:

\2005045101XX。

2、启动QuartusII,打开文本编辑器输入设计并存盘。

3、项目编译

1)将设计文件设成项目。

2)选择目标器件:

ACEX-EP1K10TC100-3。

3)参数设置:

取默认值。

4)编译。

4、时序仿真

1)建立波形文件:

*.SCF。

2)参数设置。

3)打开仿真窗口并”START”。

4)查看仿真结果

请记录仿真波形,并添加到实验报告中。

5、器件编程

1)锁定引脚并重新编译。

2)打开“PROGRAMER”窗口。

3)选择编程/配置目标文件(*.POF/SOF)。

4)点击“PROGRAM”或”CONFIGURE”。

6、硬件测试

请说明测试方法并记录测试结果,在实验报告中写出。

(二)使用条件信号赋值语句实现实验要求

步骤同上。

五、实验结果分析与实验结论

1、根据仿真及硬件测试结果说明实验是否达到了要求。

2、并行语句的特点。

3、选择信号赋值语句和条件信号赋值语句的异同。

4、其它。

实验四计数器及时序电路设计

一、实验目的

掌握时序电路的设计方法,进一步熟悉MAXPLUSII的使用方法。

二、实验要求

1、设计一个4位二进制计数器,并完成设计输入、编译、仿真、硬件测试等过程;

2、变成通用计数器;

3、利用元件例化语句实现6位计数器。

三、实验原理与方案

时序电路含有记忆元件(例如触发器),电路状态的变化一般只发生在时钟信号的特定时刻(例如上升沿),而其它时刻保持原有状态不变。

时序电路一般只能利用进程中的顺序语句来建立,最主要的途径是利用不完整的条件语句描述。

时序电路中两个关键信号是时钟信号和复位信号,在对时钟信号边沿检测的描述方法中,最常用的表达式是CLK’EVENTANDCLK=’1’。

典型的4位二进制加法计数器的功能表如下,其中CLR为异步清零输入端,CLK为时钟脉冲输入端,Q3Q2Q1Q0为计数状态输出端,如表4-1所示。

表4-1计数器功能表

CLR

CLK

Q3Q2Q1Q0

1

X

0000

0

上升沿

计数值加1

0

其它

保持不变

下面是实现该功能的示例程序,可供实验中参考。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcounter4IS

PORT(clk,clr:

INSTD_LOGIC;

q:

BUFFERSTD_LOGIC_VECTOR(3DOWNTO0));

ENDcounter4;

ARCHITECTUREbehavOFcounter4IS

BEGIN

PROCESS(clk,clr)

BEGIN

IF(clr=’1’)THEN

q<=(others=>’0’);

ELSIF(clk’EVENTANDclk=’1’)THEN

q<=q+1;

ENDIF;

ENDPROCESS;

ENDbehav;

若要建立一个位数可变的、具有典型结构的通用计数器,需要在实体说明中将位数定义成类属参数。

类属说明语句的一般格式如下:

GENERIC(参量名:

数据类型[:

=设定值]);

例如,若将4位二进制计数器的VHDL描述变成通用计数器,实体说明部分可以改写如下:

ENTITYcounternIS

GENERIC(n:

INTEGER:

=4);

PORT(clk,clr:

INSTD_LOGIC;

q:

BUFFERSTD_LOGIC_VECTOR((n-1)DOWNTO0));

ENDcountern;

对于含有类属参数的通用计数器,可以通过元件例化语句中的类属参数映射变成生成具体位数的计数器。

例如,利用通用计数器生成一个6位计数器的元件例化语句示例如下:

u1:

counternGENERICMAP(n=>6)PORTMAP(clk,clr,q);。

四、实验内容、步骤与结果

1、建立文件夹:

E:

\2005045101XX。

2、启动QuartusII,打开文本编辑器输入设计并存盘。

3、项目编译

1)将设计文件设成项目。

2)选择目标器件:

ACEX-EP1K10TC100-3。

3)参数设置:

取默认值。

4)编译。

4、时序仿真

1)建立波形文件:

*.SCF。

2)参数设置。

3)打开仿真窗口并”START”。

4)查看仿真结果

请记录仿真波形,并添加到实验报告中。

5、器件编程

1)锁定引脚并重新编译。

2)打开“PROGRAMER”窗口。

3)选择编程/配置目标文件(*.POF/SOF)。

4)点击“PROGRAM”或”CONFIGURE”。

6、硬件测试

请说明测试方法并记录测试结果,在实验报告中写出。

五、实验结果分析与实验结论

1、分析仿真及硬件测试结果说明实验是否达到了要求。

2、时序电路设计的一般方法。

3、其它。

实验五交通灯控制器的设计

一、实验目的

了解状态机的典型结构及编写方法。

二、实验要求

使用状态机设计一个交通灯控制器,该控制器用于控制十字路口的信号灯和倒计时显示器。

在东西和南北两个方向上均有一组红、黄、绿灯和倒计时显示器,假设各灯交替点亮的时间为;红灯45秒,绿灯40秒,黄灯5秒,同时用数码管指示当前状态的剩余时间。

另外设置一个禁止通行控制输入信号端,当该信号为低电平时,两个方向都禁止通行,红灯点亮,计时器不显示时间。

完成设计输入、编译、仿真、硬件测试等过程。

三、实验原理与方案

根据实验要求,两个方向灯的点亮状态共有红绿、红黄、绿红、黄红四种组合,如表5-1所示。

表5-1交通灯的状态变化表

状态

东西方向

南北方向

点亮时间(秒)

红黄绿

绿黄红

S1

100

100

40

S2

100

010

5

S3

001

001

40

S4

010

001

5

从表中可以看出,交通灯的有效状态共有4种,某一状态的定时时间到,则转向下一个状态。

在采用状态机设计时可以考虑定义一个状态变量,取值范围为s1、s2、s3、s4,另外对应禁止通行的特殊状态还可设置一个状态S0。

为了实现各状态的定时,设置两个计数定时器EW、SN,分别用于对东西、南北方向的各状态定时。

典型的状态机结构包括说明部分、主控时序进程、主控组合进程。

说明部分中使用TYPE语句将状态变量定义为新的数据类型,主控时序进程在时钟脉冲的驱动下实现状态转换,主控组合进程控制下一状态的走向和电路的输出。

下面的程序可供参考:

packagepjtdis

typestateis(s0,s1,s2,s3,s4);

endpjtd;

libraryieee;

useieee.std_logic_1164.all;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

usework.pjtd.all;

ENTITYjtdIS

PORT(clk,forbid:

INBIT;

led:

BUFFERSTD_LOGIC_VECTOR(5DOWNTO0);

EW,SN:

BUFFERSTD_LOGIC_VECTOR(7DOWNTO0));

ENDjtd;

ARCHITECTUREbehavOFjtdIS

TYPESTATEIS(s0,s1,s2,s3,s4);

SIGNALcurrent_state,next_state:

STATE;

BEGIN

REG:

PROCESS(clk,forbid)

BEGIN

IF(forbid='0')THEN

current_state<=s0;

EW<="00000000";

SN<="00000000";

ELSIF(clk'EVENTANDclk='1')THEN

IFEW>"01000110"ORSN>"01000110"THEN

EW<="01000101";

SN<="01000000";

current_state<=S1;

ELSIFEW="00000110"ANDSN="00000001"THEN

EW<="00000101";

SN<="00000101";

current_state<=s2;

ELSIFEW="00000001"ANDSN="00000001"

ANDcurrent_state=S2THEN

EW<="01000000";

SN<="01000101";

current_state<=s3;

ELSIFEW="00000001"ANDSN="00000110"THEN

EW<="00000101";

SN<="00000101";

current_state<=s4;

ELSIFEW="00000001"ANDSN="00000001"

ANDcurrent_state=S4THEN

EW<="01000101";

SN<="01000000";

current_state<=s1;

ELSIFEW(3DOWNTO0)="0000"THEN

EW<=EW-7;

SN<=SN-1;

ELSIFSN(3DOWNTO0)="0000"THEN

EW<=EW-1;

SN<=SN-7;

ELSE

EW<=EW-1;

SN<=SN-1;

ENDIF;

ENDIF;

ENDPROCESS;

COM:

PROCESS(current_state)

BEGIN

CASEcurrent_stateI

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 指导书 EDA 实验

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx