数字集成电路考题(2012)Word下载.doc

数字集成电路考题(2012)Word下载.doc

- 文档编号:14180704

- 上传时间:2022-10-19

- 格式:DOC

- 页数:11

- 大小:619.47KB

数字集成电路考题(2012)Word下载.doc

《数字集成电路考题(2012)Word下载.doc》由会员分享,可在线阅读,更多相关《数字集成电路考题(2012)Word下载.doc(11页珍藏版)》请在冰豆网上搜索。

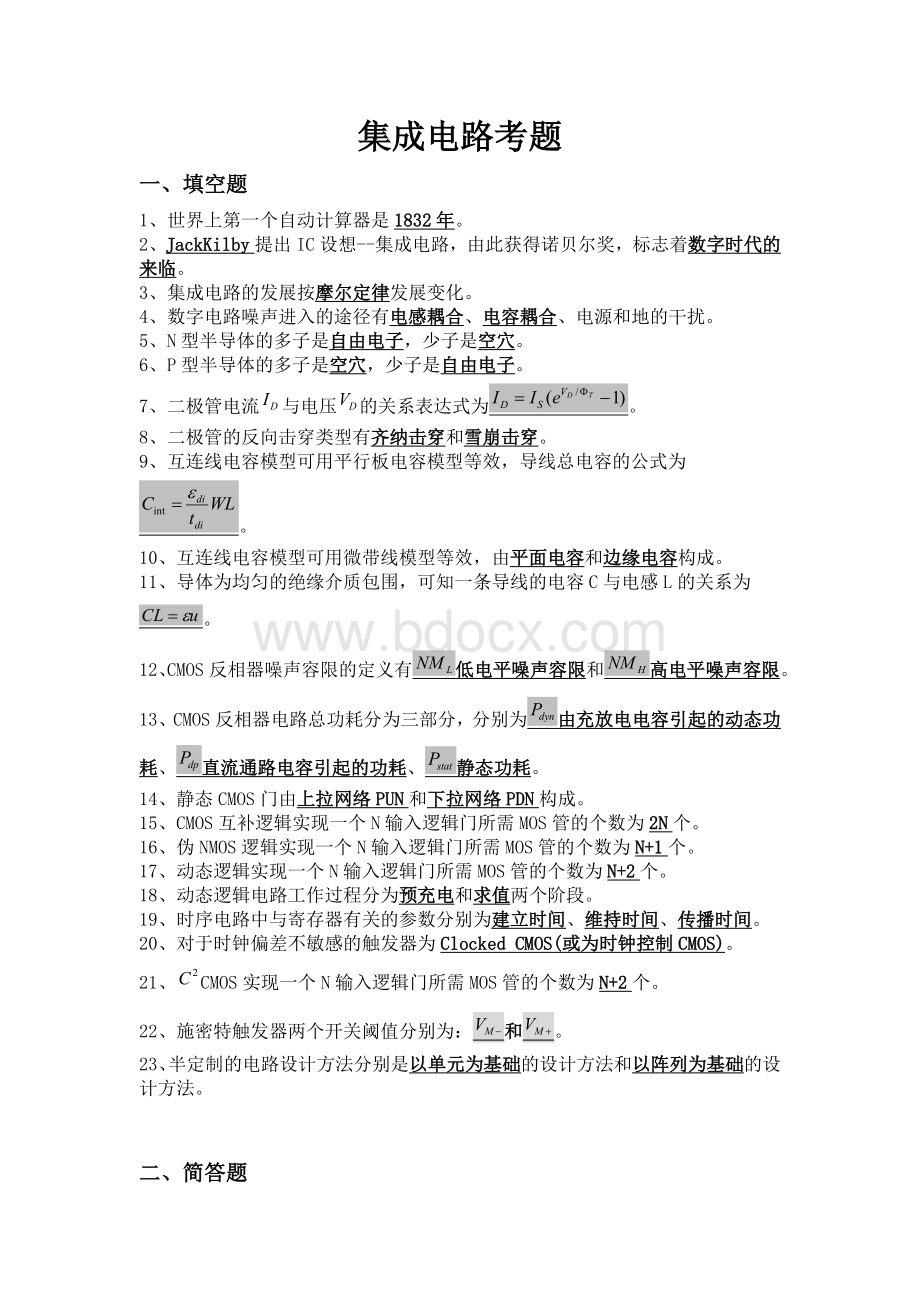

19、时序电路中与寄存器有关的参数分别为建立时间、维持时间、传播时间。

20、对于时钟偏差不敏感的触发器为ClockedCMOS(或为时钟控制CMOS)。

21、CMOS实现一个N输入逻辑门所需MOS管的个数为N+2个。

22、施密特触发器两个开关阈值分别为:

和。

23、半定制的电路设计方法分别是以单元为基础的设计方法和以阵列为基础的设计方法。

二、简答题

1、画出双阱CMOS电路工艺顺序简化图。

(P31)

2、二极管的电流受工作温度的双重影响。

(P60)

(1)出现在电流方程的ΦT与温度呈线性关系,ΦT的增加会使电流下降。

(2)饱和电流IS也与温度有关,热平衡时载流子浓度会随温度增加。

理论上,每上升5°

C饱和电流增加一倍,实测是反向电流每8°

C增加一倍。

3、如果考虑导线的寄生电容和电感,写出简化规则和步骤(P99)

(1)如果电阻很大----例如界面很小的长铝导线情形或者外加信号的上升和下降沿很慢,电感可以忽略

(2)当导线很短,截面积很大或者互连材料电阻率很低时,可以用只含电容的模型。

(3)若导线间距很大,或者导线只在一段很短的距离上靠近一起的时候,导线相互间电容可以忽略,并且所有的寄生电容都可以模拟成接地电容。

4、简述理想导线和集总模型。

(P109)

(1)理想导线:

一般电路上,导线是没有任何附加参数和寄生参数的简单连线。

这样的导线对电路的特性没有任何影响。

(2)集总模型:

导线的电路寄生参数一般是沿着它的长度分布的,不能集中在一点。

当然,当只有一个寄生元件支配时,把其它寄生参数影响小的元件的各个不同部分集总成单个电路元件,这就是集总模型。

5、简述集总RC模型(P110)

把每段导线的总导线电阻集总成一个电阻R,把电容集总成一个电容C,这个简单模型就是集总RC模型。

6、简述静态CMOS反相器的特性。

(130)

(1)输出高低电平分别为VDD和GND;

(2)逻辑电平与器件的相对尺寸无关,所以晶体管可以采用最小尺寸。

(3)稳态时在输出和VDD和GND总存在一条具有有线电阻的通路。

(4)CMOS反相器输入阻抗高,MOS管栅极实际上是一个绝缘体。

(5)稳态工作下,电源和地线之间没有通路。

7、简述CMOS反相器噪声容限的定义。

(P136)

所谓噪声容限,是指电路在噪声干扰下,逻辑关系发生偏离(误动作)的最大允许值。

若输入信号中混入了干扰,当干扰大过反相器输入电压阈值时,则使原本应该是高电平的输出信号翻转为低电平,或使原本应该是低电平的输出信号翻转为高电平。

8、密勒效应的定义。

(P141)

一个在其两端大小相同相位相反的电压摆幅的电容可以用一个两倍于该电容值的接地电容代替。

9、互补CMOS是一种实现逻辑门的有效电路,但复杂的逻辑电路存在两个问题,原因有两点。

(P180)

问题:

(1)实现N输入逻辑门,需要2N个MOS管,加大实现面积。

(2)互补CMOS门传播延时随扇入数迅速增加。

原因:

(1)MOS管数目多(2N),增加了门的总电容;

(2)门的PUN或PDN中,MOS串联会使门的速度进一步减慢。

10、降低大扇入延时的方法。

(P181-182)

(1)调整MOS管尺寸:

加大MOS管尺寸,能降低

串联期间的电阻,减小时间常数。

(2)逐级增大MOS管尺寸:

即MOS管尺寸,M1>

M2>

M3>

M4,可以使R1<

R2<

R3<

R4,

这样降低了其主要作用的电阻。

(3)重新安排输入:

找到关键信号,决定关键路径

(4)重组逻辑结构

11、简述传输管逻辑的特性。

(P196)

基本概念

通过允许原始输入驱动栅端和漏-源端来减少实现逻辑功能所需MOS管数目的方法,称为传输管逻辑。

功能分析

若B输入高,M1导通,A直接到输出F,若B为低M2导通,并使0直接输出到F。

这一方法可以减少四个MOS管,降低电容。

12、简述动态逻辑门的特性(P208-209)

(1)逻辑门由NMOS下拉网络实现,PDN的构成过程与静态CMOS完全一样。

(2)MOS管数目比静态减少,数目为N+2,非2N。

(3)是无比逻辑门。

(4)动态逻辑门只有动态功耗,理想情况VDD和GND之间从不存在任何静态电流路径。

(5)动态逻辑门具有较快的开关速度。

13、简述时序逻辑电路中与寄存器有关的参数。

(P237)

(1)建立时间tsu:

在时钟翻转(正沿触发为0-1翻转)之前数据输入(D)必须有效的时间。

(2)维持时间thold:

在时钟边沿之后输入数据必须仍然有效的时间。

(3)传播延时tc-q:

相对于时钟最坏情况的延时。

指的是输入数据(D)送到输出端Q的时间。

14、简述施密特触发器的特性。

(P208-209)

(1)对于一个输入变化很慢的信号,输出端可以有一个快速翻转的响应。

(可用于脉冲整形)

(2)有两个不同方向的开关阈值VM+、VM-。

15、简述数字处理器的构成(四个模块)(P277)

(1)数据通路:

处理器核心部分,完成所有处理运算工作的场所。

(2)控制模块:

协调各个部分正常工作的关键部分,让处理器等在指定时间完成相应的工作,可以看成一个有限状态机(FSM)。

(3)存储模块:

整个处理器中用来存储数据的区域,可以有只读、读写等多个种类。

(4)输入输出(互连):

处理器与外界连接的主要媒介,可以用来连接外接信号,也可以连接多个处理器。

16、简述半定制的设计流程。

(289)

(1)设计获取,使设计进入到ASIC设计系统中。

(2)逻辑综合,把HDL语言描述模块转换成网表(netlist)。

(3)版图前模拟和验证,检查设计是否正确。

(4)版图规划,对芯片面积总体规划。

(5)布局,确定各单元精确位置。

(6)布线,完成各单元和功能块之间连线。

(7)提取模型参数,完成芯片模型的创建。

(8)版图后模拟和验证,检验性能,发现不足改进和优化。

(9)记带。

17、简述克服串扰的方法。

(P327)

(1)尽量避免浮空节点。

(2)敏感节点应当很好地与全摆幅信号隔离。

(3)在满足时序约束的范围内尽可能加大上升(下降)时间。

(4)在敏感的低摆幅布线网络中采用差分信号传输方法。

(5)不要使两条信号线之间的电容太大。

(6)必要时可在两个信号之间增加一条屏蔽线--GND或。

(7)不同层上信号之间的线间电容可以通过增加额外的布线层来进一步减少。

三、计算题

1、设计计算题(P64例3.5公式3.19)

例3.5:

PMOS晶体管的阈值电压

一个PMOS晶体管的阈值电压VT0为-0.4V,而体效应系数等于-0.4。

试计算VSB=-2.5V,2ΦF=0.6V时的阈值电压。

解:

由阈值公式

得

可以看到,-0.4V是零偏置条件下阈值的2倍。

2、(P104)例4.1金属导线电容

总电容=平面电容+边缘电容

平面电容计算公式:

电容计算公式:

平面电容:

边缘电容:

总电容:

拓展:

假设两条导线,第二条在第一条旁边,间距只相隔最小允许距离10cm,与第一条耦合电容为

几乎与总的对地电容一样大。

3、RC的树形网络。

(P111)

写出网络的性质,路径电阻的计算,共享电阻的计算

性质:

(1)电路仅有一个输入节点。

(2)所有电容都在每个节点和地之间。

(3)电路没有任何电阻回路。

路径电阻:

源节点S和电路内任何节点i之间存在一条惟一电阻路径,用Rii表示。

上图,源节点s和节点4之间的路径电阻为R44:

共享电阻:

Rik代表的路径电阻为源节点s至节点k和节点i这两条路径的电阻

上图所示电路

4、(P136)例5.2CMOS反相器的电压传输特性和噪声容限

设计一个通用0.25umCMOS工艺反相器,PMOS对NMOS的比为3.4,其中NMOS的最小尺寸(W=0.375um,L=0.25um,W/L=1.5),计算VM=1.25处的增益。

首先应用公式

求得

再应用

由此得到如下

5、(P146)例5.5一个0.25umCMOS反相器延时

利用前面推导公式,计算tpHL和tpLH

根据表3.3,VDD=2.5V时,可得Reqn=13K,Reqp=31K,CL(H→L)=6.1,CL(L→H)=6.0,

NMOS的W/L=1.5,PMOS的W/L=4.5,代入两个公式可得:

6、(P174)对PDN、PUN以及综合的们进行详细的分析。

例6.2CMOS复合门的综合

利用互补CMOS逻辑合成功能为的逻辑门电路。

(1)实现PDN:

根据NMOS“串与并或”,PMOS“串或并与”,将PDN网络拆成子电路较小的网络(称为PDN的子集)。

首先,括号内B+C的PDN表示为两个NMOS管并联,其次A(B+C)的PDN可以用一个NMOS管和(B+C)的PDN串联构成,最后,D+A(B+C)的PDN可以由一个NMOS管和A(B+C)的PDN构成。

如图a所示:

(a)PDN(b)PUN

由于PUN为PDN的对偶网络括号内B+C的PUN表示为两个PMOS管串联,其次A(B+C)的PUN可以用一个PMOS管和(B+C)的PUN并联构成,最后D+A(B+C)的PUN可以由一个PMOS管和A(B+C)的PUN串联构成。

如图b所示:

综合一起,可以得到的逻辑电路如右图:

7、(P178)画出两输入NAND门的等效RC模型

8、(P186)例6.6确定组合逻辑延时最小的尺寸。

如图6.19所示,它代表一个复杂逻辑电路的关键路径,

输出负载是一个电容,为第一级输入电容的5倍,所以路径

等效扇出F=CL/Cg1=5

路径逻辑努力G为:

路径没有分支,路径分支努力B=1,总路径努力H=GFB=125/9。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字集成电路 考题 2012

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls