单元12 门电路Word下载.docx

单元12 门电路Word下载.docx

- 文档编号:22271850

- 上传时间:2023-02-03

- 格式:DOCX

- 页数:18

- 大小:163.61KB

单元12 门电路Word下载.docx

《单元12 门电路Word下载.docx》由会员分享,可在线阅读,更多相关《单元12 门电路Word下载.docx(18页珍藏版)》请在冰豆网上搜索。

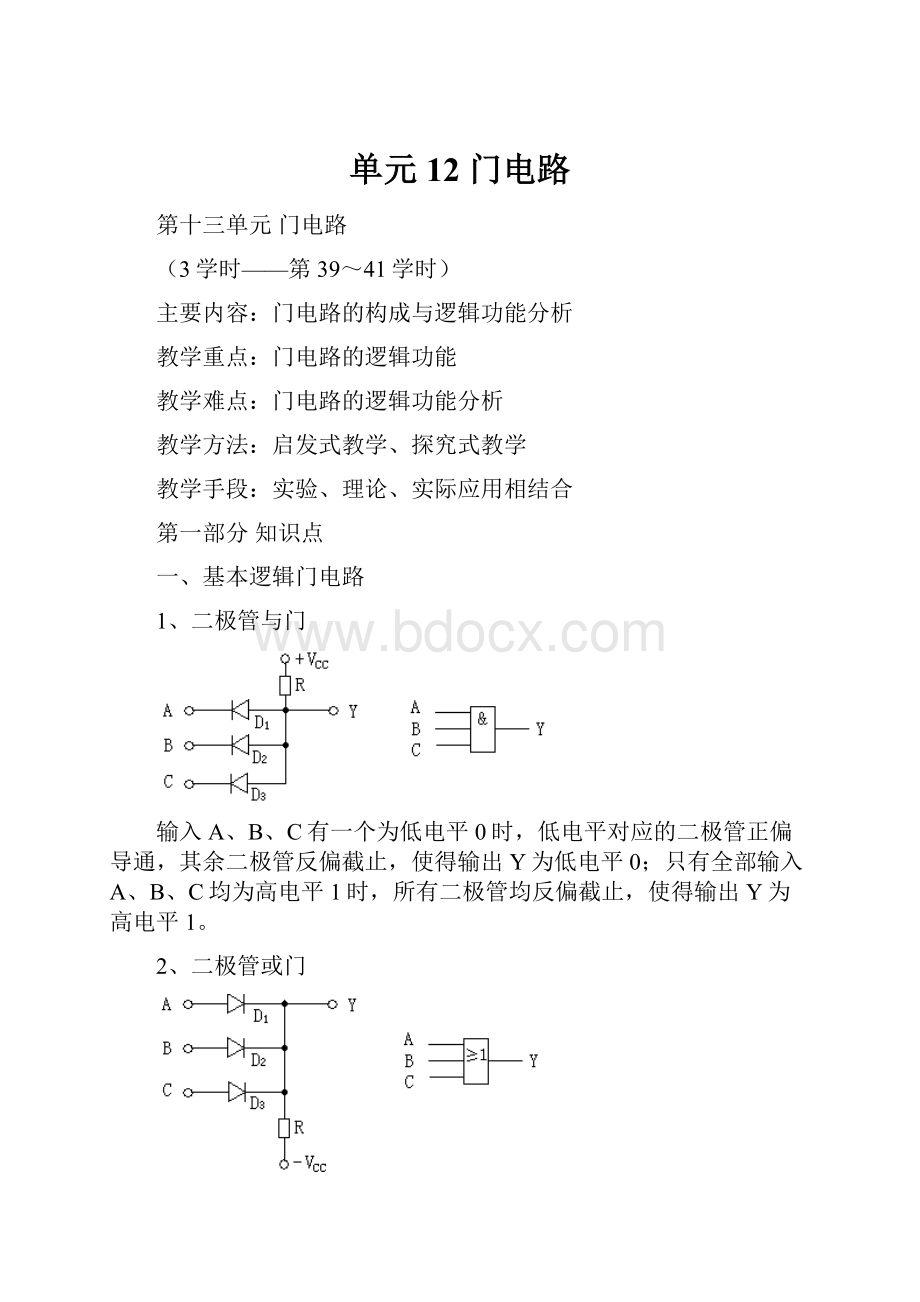

输入A为低电平0时,三极管处于截止状态,输出Y为高电平1。

4、MOS管非门

输入A为低电平0时,栅源电压小于开启电压,场效应管处于截止状态,输出Y为高电平1;

输入A为高电平1时(高于开启电压),场效应管处于导通状态,输出Y为低电平0。

二、CMOS集成门电路

CMOS集成门由P沟道增强型MOS管和N沟道增强型MOS管互补对称构成。

1、CMOS反相器

(1)基本点路

反相器即非门。

假设MOS管开启电压UTN=-UTPN=2V。

输入A为低电平0V时,UGSN=0V<UTN、TN截止,UGSP=-10V<UTP、TP导通,输出Y为高电平1;

输入A为高电平10V时,UGSN=10V>UTN、TN导通,UGSP=0V>UTP、TP截止,输出Y为低电平0。

(2)带输入端保护功能点路

栅极与沟道之间的SiO2绝缘层厚度约为10-8米,容易受干扰影响(所以输入端不得悬空)、电压超标时容易击穿损坏。

为此加入保护电路。

R、D1、D2、D3构成抗干扰电路。

若输入高于VDD+UD或低于-UD时,相应二极管导通,使栅源电压控制在-UD~(UD+VDD)之间。

R、C1、C2构成积分电路,消除输入干扰信号。

(3)静态特性

①输入特性

输入端所加电压uI与输入电流iI之间的关系。

当A在-UD~(UD+VDD)时,iI≈0——MOS管输入电流为0;

当A>(UD+VDD)时,保护二级管D3导通,iI从输入端流入而流向VDD——相当于二级管正向导通特性;

当A<-UD时,保护二级管D1导通,iI自D1、R流出输入端。

输入电流关系实际上是保护网络的电流关系——近似为二级管的正向特性。

CMOS电路的输入端不得悬空,否则TN、TP无法工作而导致逻辑混乱。

②输出特性

输出端电压uo与输出电流io之间的关系。

当A=0时,输出为1,输出电流由门向外流向负载——此时负载为拉电流负载,反向器能输出的最大电流IOH称为“带拉电流负载的能力”;

当A=1时,输出为0,输出电流由负载向内流入门——此时负载为灌电流负载,反向器能灌入的最大电流IOL称为“带灌电流负载的能力”。

若VDD降低,导电沟道变窄,使得UOH下降、UOL上升,带负载能力变差。

③传输特性

输入端电压与输出端电压之间的关系及输入端电压与漏极电流(由VDD经TP、TN流向地的电流)之间的关系。

AB段:

uI<UTN,TN截止、TP导通,uO=VDD、iD=0;

BC段:

uI>UTN,TN开始导通,但导通电阻较大,uO略有下降、iD开始增加;

CD段:

uI在0.5VDD附近,TN、TP均导通,uO急剧下降、iD增至最大;

DE、EF段与AB、BC段相反。

uI=0.5VDD叫作反向器的转折电压或阈值电压,用UT表示。

(4)动态特性

①传输延迟时间

输入电压与输出电压之间的关系传输关系。

tPHL:

输出由高电平变为低电平的传输延迟时间;

tPLH:

输出由低电平变为高电平的传输延迟时间;

平均传输延迟时间:

。

②输出端状态转换时间

输入信号变化时,输出信号发生变化,输出电压高低转换时间称为输出端状态转换时间。

tTHL:

输出由高电平到低电平的转换时间;

tTLH:

输出由低电平到高电平的转换时间。

2、CMOS与门、或门、与非门、或非门

出逻辑功能外,其他性质类似非门。

3、CMOS传输门、三态门

(1)传输门

传输门是一种传送模拟信号的压控开关(可双向传送)。

靠控制信号

、

来控制传输情况:

(1)C=1、

=0,两MOS门均导通——传输门导通,uo=ui

(2)C=0、

=1,两MOS门均截止——传输门截至,输入与输出断开。

(2)三态门

三态门是一种具有使能控制端的逻辑门,具有高1、低0、高阻Z三种状态。

使能时电路具有正常逻辑功能,否则为高阻(相当于输出端悬空)。

低电平有效三态门具体逻辑功能如下:

,TP1、TN1导通,TP2、TN2构成反向器——

,TP1、TN1截止,TP2、TN2进一步也截止——

高电平有效三态门具体逻辑功能如下:

,

,

三态门分为三态非门(反向器)、三态与非门、三态缓冲门等。

(3)漏极开路门(OD门)

输出MOS管的漏极是开路的,使用时必须加上上拉电阻及电源(否则不能工作)。

OD门可以实现线与的逻辑门(但使用时必须加上上拉电阻及电源)。

4、CMOS集成逻辑门主要特点

(1)功耗极低(一般不超过100uW);

(2)电源电压范围宽(可达几V~十几V之间);

(3)高干扰能力强;

(4)逻辑电平差别大(低电平约为0V、高电平约为VDD)

(5)输入电阻极高(可达108Ω以上);

(6)扇出系数(可带同类门的数目)大(可达几十);

(7)集成度高;

(8)抗辐射能力强;

(9)成本低。

5、CMOS集成逻辑门使用注意事项

(1)输入端不可悬空;

(2)输入端接有电阻时,电阻可视为短路。

三、TTL与非门

1、TTL反向器(非门)

(1)电路构成

输入低电平0V时,T1基极电流流入发射极(电流自反向器输入端流出),使得IB2为0,则T2截止,进一步T4也截止,而T3和D饱和导通(因为流经R2的电流几乎全部流向T3),输出为高电平。

因为输出三极管T4截止,电路此时状态叫做截止状态(输入低电平、输出高电平);

输入高电平3.6V时,T1处于倒置状态(发射极和集电极颠倒),电流自反向器输入端流入,进而较大电流流入T2基极,使得T2饱和导通,进一步T4也导通,而T3基极电位较低,使得T3和D截止(因为流经R2的电流几乎全部流向T2),输出为低电平。

因为输出三极管T4导通,电路此时状态叫做导通状态(输入高电平、输出低电平);

由以上分析看出,电路为反向器(非门)。

(2)静态特性

输入伏安特性:

输入端电压和输入电流之间的关系。

当uI=0(0V)时,

,称为输入端短路电流,由反向器输入端流出的电流;

当uI=1(3.6V)时,iS=ISH≈0.01mA,称为输入端漏电流,又叫输入高电平电流,流入反向器输入端的电流。

输入端负载特性:

输入端电阻和电压之间的关系。

当Ri=∞时(输入端悬空),uO=UOL≤0.3V,反向器处于导通状态。

实际上,只需Ri≥2.5k,既可保证反向器处于导通状态(输出低电平),常将2.5k称作开门电阻,记作Ron

当Ri=0时,uO=UOH=3.6V,反向器处于截止状态或关断状态(输出高电平)。

实际上,只需Ri≤0.7k,既可保证反向器处于截止状态,常将0.7k称作关门电阻,记作Roff

若Roff≤Ri≤Ron,反向器处于不正常工作状态——逻辑混乱,要禁止。

②输出特性(输出伏安特性)

输出电压和输出电流之间的关系。

带灌电流负载特性(uI=1,uO=0):

此时电路处于导通状态——T4导通、T3和D截止。

负载外加电源形成电流,流向反向器内部(灌入电流)。

带灌负载能力IOL可达16mA。

带灌电流负载时,输出低平有所上升(串联分压所致)。

带拉电流负载特性(uI=0,uO=1):

此时电路处于截止状态——T4截止、T3和D导通。

在负载上形成电流,由反向器流向负载(拉出电流)。

带拉负载能力IOH一般为400uA。

当RL=0(输出短路)时,IOH可达33mA,IOS=33mA叫输出短路电流,但短路时间不得超过1s,否则烧坏器件。

带拉电流负载时,输出高电平有所下降(串联分压所致)。

③电压传输特性

输入电压和输出电压之间的关系。

uI<0.6V时,uB1<1.3V,T2、T4截止,T3、D导通,输出高电平3.6V——截止区。

uI>0.6V后,uB1升高,T2导通、T4处于放大状态,输出随uI增加而线性下降——线性区。

uI>1.4V,T2导通、T4也导通,使得输出急剧下降——转折区。

转折区中心对应的电压称作反向器的阈值电压或门槛电压,用Uth表示。

Uth=1.4V。

DE段:

uI>1.5V后,T2、T4导通,,T3、D截止,输出低电平0.3V——饱和区。

(3)动态特性

传输延迟时间

输出有高电平变为低电平的传输延迟时间;

输出有低电平变为高电平的传输延迟时间;

:

平均传输延迟时间

产品规定典型值:

tPHL=8ns、tPLH=12ns,最大值tPHL=15ns、tPLH=22ns

2、TTL与非门、或非门等

(1)TTL与非门

输入A、B有一个(或全部)为低电平时,T1基极电流流入发射极(电流自反向器输入端流出),使得IB2为0,则T2截止,进一步T4也截止,而T3和D饱和导通,输出为高电平。

输入A、B均为高电平时,T1处于倒置状态(发射极和集电极颠倒),电流自反向器输入端流入,进而较大电流流入T2基极,使得T2饱和导通,进一步T4也导通,而T3基极电位较低,使得T3和D截止,输出为低电平。

由以上分析看出,电路为与非逻辑。

(2)TTL或非门

略。

(3)TTL集电极开路门(OC门)

输出三极管T4集电极开路,使用时必须外接负载和直流电源。

OC门可实现线与。

(4)TTL三态门

三态门是一种具有使能控制端的非门。

使能时电路具有正常逻辑功能,否则为高阻(相当于输出端开路悬空)。

三态门分为三态与非门、三态非门(反向器)、三态缓冲门等。

三态门应用举例:

①用作多路开关

根据

的取值,让G0或G1工作,使得数据A0或A1反向后传输到输出端。

②用于信号双向传输

的取值,让G0或G1工作,使得数据

或

,实现数据双向传输。

③构成数据总线

工作时每次只传送一个数据。

为此只让某一个门Gi使能,使得数据Ai传送到数据总线上。

3、TTL集成逻辑门使用注意事项

(1)输入端可悬空,悬空时该输入端视为高电平(但一般不做悬空处理);

(2)输入端可接电阻,但所接电阻应该是大电阻——大于Ron(约2.5k)或小电阻——小于Roff(约0.7k)。

且:

某输入端所接电阻大于Ron(约2.5k)时,该电阻可视为无限大,或输入端视为悬空,输入端为高电平;

某输入端所接电阻小于Roff(约0.7k)时,,该电阻可视为0,该输入端视为短路,视为高电平;

输入端不可接中值,即若Roff≤Ri≤Ron,反向器处于不正常工作状态——逻辑混乱,要禁止。

第二部分题目分析

题1:

图中各电路均有TTL逻辑门构成,Ron=1k、Roff=0.7k。

分别写出各电路表达式;

若a、d是COMS门,再写出其表达式(西安电子科技大学2005年试题)

解:

TTL门:

(a)门1对应3k输入端相当于高电平1、门2对应0.3k输入端相当于低电平0,故

(b)C=0时,门1输出

、门2为高阻,仅有门1输出;

C=1时,门1为高阻、门2输出

,仅有门2输出。

故

(c)两个OC门线与,

(d)门2的3k输入端相当于悬空——高电平。

COMS门

(a)3k、0.3k对应输入端均为低电平。

(d)3k输入端相当于低电平。

要点:

TTL门输入端悬空或接大电阻(一般大于2.5k)相当于高电平;

解小电阻(小于0.7k)相当于短路;

COMS门接任意电阻均视为短路。

题2:

试问下列电路能否正常工作?

能正常工作者写出逻辑函数,不能正常工作者说明原因。

其中a、b为TTL门,c、d为COMS门。

(浙江大学2005年试题)

(a)OC门线与时必须有上拉电阻和电源,故该电路有误。

(b)TTL与非门不可线与,故该电路有误。

(c)电路为三态门和传输门的连接。

当E=1时,G1门和G3门为高阻,G1门为与非逻辑,故F3=Z;

当E=0时,G1门为与非逻辑,G2门为高阻,G3门导通,故

(d)当C=1时,F4=Z;

当E=0时,F4=A。

三态门、OC门、COMS门特性。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 单元12 门电路 单元 12

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《城市规划基本知识》深刻复习要点.docx

《城市规划基本知识》深刻复习要点.docx