电工电工综合实验2.docx

电工电工综合实验2.docx

- 文档编号:2258982

- 上传时间:2022-10-28

- 格式:DOCX

- 页数:26

- 大小:643.87KB

电工电工综合实验2.docx

《电工电工综合实验2.docx》由会员分享,可在线阅读,更多相关《电工电工综合实验2.docx(26页珍藏版)》请在冰豆网上搜索。

电工电工综合实验2

电气制图及CAD

实验报告

——数字计时器

07042100班

0704240132

张镝

1、电路原理

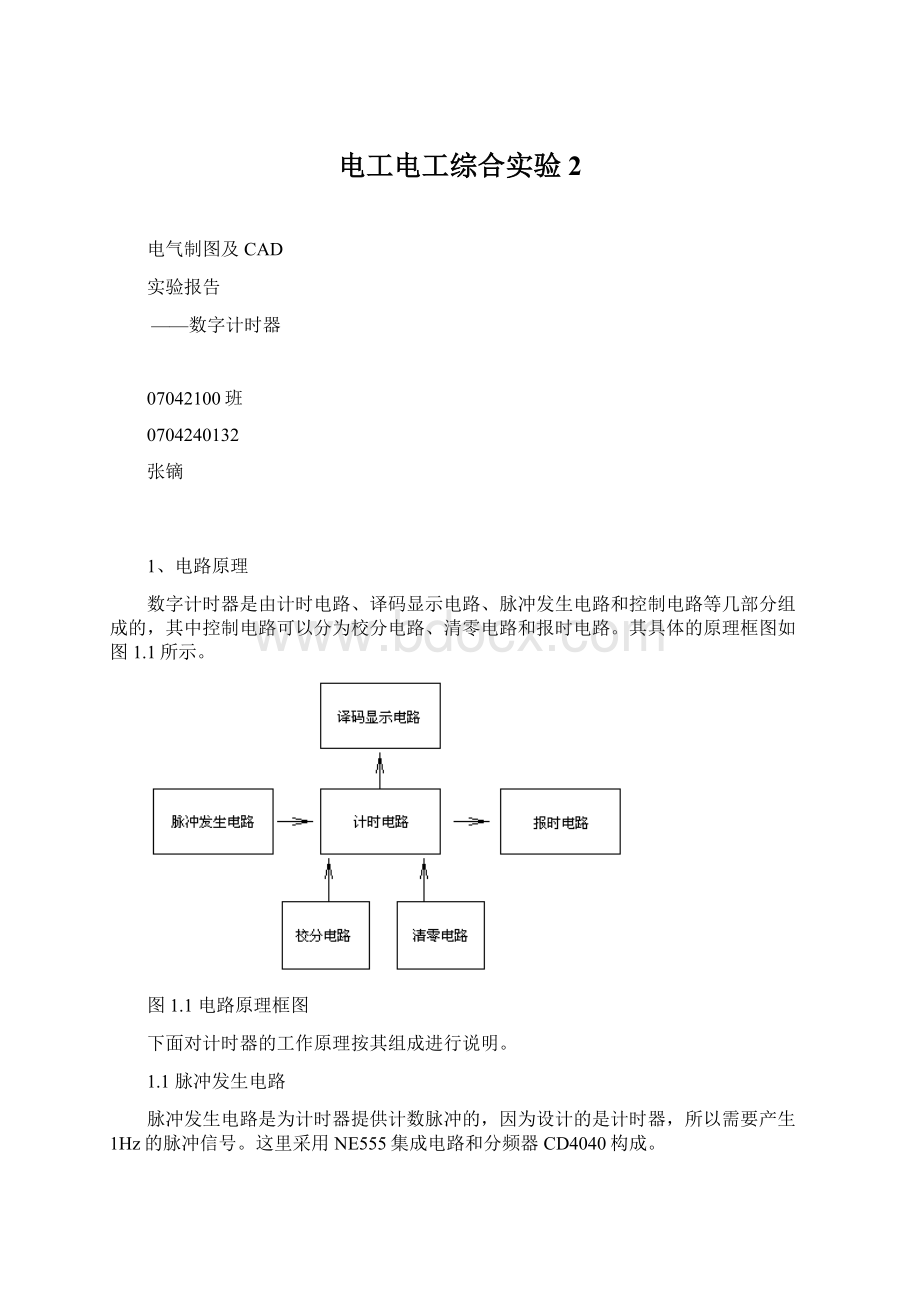

数字计时器是由计时电路、译码显示电路、脉冲发生电路和控制电路等几部分组成的,其中控制电路可以分为校分电路、清零电路和报时电路。

其具体的原理框图如图1.1所示。

图1.1电路原理框图

下面对计时器的工作原理按其组成进行说明。

1.1脉冲发生电路

脉冲发生电路是为计时器提供计数脉冲的,因为设计的是计时器,所以需要产生1Hz的脉冲信号。

这里采用NE555集成电路和分频器CD4040构成。

1.2计时电路

计时电路钟的计数器,可以采用二-十进制加法计数器CD4518实现。

60秒为1分,将分和秒的个位、十位分别在七段数码显示器上显示出来,从0分0秒到59分59秒,然后重新计数。

1.3译码显示电路

译码器可以采用CD4511通过330Ω电阻来驱动共阴极显示器。

1.4报时电路

电路每小时进行一次报时,从59分53秒开始报时,每隔一秒发一声,共三声低音、一声高音。

即59分53秒、59分55秒、59分57秒为低音,59分59秒为高音。

实际上,需要在某一时刻报时,就将该时刻输出为“1”的信号作为触发信号,选通报时脉冲信号,进行报时即可。

1.5校分电路

电路中存在一个开关,当开关打到“正常”档时,计数器正常计数;当开关打到“校分”档时,分计数器进行快速校分(即分计数器可以不受秒计数器的进位信号控制,而选通一个频率较快的校分信号进行校分),而秒计数器保持。

在任何时候,拨动校分开关,可以进行快速校分。

即令计时器分为快速计数,而秒位保持。

1.6清零电路

在任何时刻,拨动清零开关,可以进行计数器的清零。

2、实验器件参数及其所构成电路

电路中的器件有NE555集成电路1片、CD4040集成电路1片、CD4518集成电路2片、CD4511集成电路4片、74LS74集成电路1片、74LS00集成电路3片、74LS20集成电路1片、74LS21集成电路2片、双字数码管显示器2个、阻值为330Ω的电阻28只、阻值为1kΩ和3kΩ的电阻各1只,以及容值为0.047μF的电容1只。

下面分别介绍所用器件以及它们所构成的电路。

2.1NE555集成电路

NE555是在电子科技行业广为应用的一种集成电路,用途十分广泛。

在本电路中,构成时钟发生器,是整个电路的核心。

其内部结构如图2.1所示。

图2.1NE555内部结构电路

其中引脚1为接地端,引脚2和引脚6为输入端,引脚3为输出端,引脚4为复位清零端,引脚5为调整端(通常空置或通过一个电容接地),引脚7位放电端,引脚8为电源。

图2.2为NE555引脚图。

图2.2NE555引脚图

NE555功能如表2.1所示。

(引脚4)

Vi1(引脚6)

Vi2(引脚2)

VO(引脚3)

0

×

×

0

1

0

1

禁止

1

1

1

保持

表2.1NE555功能表

当将NE555连结成图2.3所示的自激多谐振荡电路时,输出端为周期矩形波。

图2.3周期矩形波发生电路

输出矩形波周期

将图2.3中电阻和电容的数值代入上式,可得T=0.228ms,即。

在经过CD4040的分频之后,即可得到频率大约为1Hz的时钟信号。

2.2CD4040集成电路

CD4040是一种常用的12分频集成电路。

当在输入端输入某一频率的方波信号时,其12个输出端的输出信号分别为该输入信号频率的2-1~2-12,在电路中利用其与NE555组合构成脉冲发生电路。

其内部结构图如图2.4所示

图2.4CD4040集成电路内部结构图

引脚图如图2.5所示。

图2.5CD4040引脚图

其中VDD为电源输入端,VSS为接地端,CP端为输入端,CR为清零端,Q1~Q12为输出端,其输出信号频率分别为输入信号频率的2-1~2-12。

将图2.3所示电路的输出端接至CD4040的输入端,则可以在Q12输出端得到频率大致为1Hz的方波信号。

可以利用其为电子钟的计时信号。

另外,在Q11、Q3、Q2三个输出端得到频率大致为2Hz、500Hz和1kHz的信号,这三个信号在后面介绍的电路中还要用到。

于是脉冲发生电路部分如图2.6所示。

图2.6脉冲发生电路

2.3CD4518集成电路

CD4518时一种常用的8421BCD码加法计数器。

每一片CD4518集成电路中集成了两个相互独立的计数器,每个计数器的内部结构图如图2.7所示。

图2.7CD4518内部结构图

引脚图如图2.8所示。

图2.8CD4518引脚图

CD4518逻辑功能如表2.2所示。

输入

输出

CR

CP

EN

Q3

Q2

Q1

Q0

清零

1

×

×

0

0

0

0

计数

0

↑

1

BCD码加法计数

保持

0

×

0

保持

计数

0

0

↓

BCD码加法计数

保持

0

1

×

保持

表2.2CD4518功能表

于是,当清零端输入1,EN端为1且CP端输入时钟信号或者EN端输入时钟信号且CP端为0时计数器进行计数。

其输出端Q3Q2Q1Q0输出从0000到1001的循环。

所以当使用其作为分和秒的个位进行计数时不需对其进行反馈清零,而用其进行分和秒的十位计数时,需要在Q3Q2Q1Q0输出0110时对其进行清零(因为CD4518是异步清零)。

下面以秒的计数器为例,说明其电路结构。

图2.9计时器秒位电路结构

图中两个集成电路即为1片CD4518所集成的两个计数器。

下方(U8B)为个位计数器,上方(U8A)为十位计数器。

引脚9始终接高电平,引脚10接由CD4040所输出的1Hz的时钟信号,每当时钟信号出现下降沿则计数器加1。

在此使用EN端为时钟信号控制端而不用CP端是因为在集成电路内部,CP端比EN端多通过一个非门(见图2.7所示),因此若通过CP端接入时钟信号则会因为此非门的存在而增加延时,从而出现误差。

接通时钟信号后,输出端引脚Q3Q2Q1Q0开始计数。

当输出为1001时需要对十位进位,也就是说,此时需要给控制十位计数的集成电路一个下降沿。

考虑Q3端当且仅当输出由1001变为0000时出现下降沿,于是直接将Q3端作为十位计数器的输入时钟信号。

在接收到第6个下降沿信号后,十位输出端将由0101变为0110。

此时,需要对其进行清零。

考虑电路清零模块,使用两个与非门(图中空置的输入端为清零输入端)。

当CD4518的4号引脚和5号引脚同时输出1或者清零端输入0时十为被清零。

这就使得其在短暂输出0110后立即被清零成0000。

同时考虑当且仅当十位输出由0101经过短暂的0110变为0000时Q2输出一个下降沿,于是利用其通过校分电路向分钟位进位。

2.4CD4511集成电路

CD4511是一种8421BCD码向8段数码管各引脚码的转换器。

当在其四个输入端输入8421BCD码时,其7个输出端可直接输出供7段数码管使用的信号。

其引脚图如图2.10所示。

图2.10CD4511引脚图

输入

输出

LE

D

C

B

A

g

f

e

d

c

b

a

字符

测灯

0

×

×

×

×

×

×

1

1

1

1

1

1

1

8

灭零

1

0

×

0

0

0

0

0

0

0

0

0

0

0

消隐

锁存

1

1

1

×

×

×

×

显示LE=0→1时数据

译码

1

1

0

0

0

0

0

0

1

1

1

1

1

1

0

1

1

0

0

0

0

1

0

0

0

0

1

1

0

1

1

1

0

0

0

1

0

1

0

1

1

0

1

1

2

1

1

0

0

0

1

1

1

0

0

1

1

1

1

3

1

1

0

0

1

0

0

1

1

0

0

1

1

0

4

1

1

0

0

1

0

1

1

1

0

1

1

0

1

5

1

1

0

0

1

1

0

1

1

1

1

1

0

0

6

1

1

0

0

1

1

1

0

0

0

0

1

1

1

7

1

1

0

1

0

0

0

1

1

1

1

1

1

1

8

1

1

0

1

0

0

1

1

1

0

0

1

1

1

9

表2.3CD4511逻辑功能表

根据CD4511的逻辑功能表可知,当输入为1而输入为0时其7个输出端分别输出一定的信号。

只需将这些信号接入8段数码管相对应的引脚即可使其显示我们所需要的数字。

然而实际上我们需要在每个CD4511的输出端和数码管相应的输入端之间接入一个阻值为330Ω的电阻以防电流过大使数码管烧毁。

显示部分电路如图2.11所示。

图2.11显示部分电路

图中左侧四个输入端分别连接CD4518的4个输出端。

这样8段数码管就可以正常显示计数器所记载的数字编码了。

由于电路的显示部分不会出现小数,故8端数码管的小数点引脚悬空。

2.574LS74集成电路

74LS74集成电路是一种D触发器。

其引脚图如图2.12所示:

图2.1274LS74引脚图

由图可见,每片74LS74中集成了两个D触发器。

由于电路中只需要用到一个D触发器,故假设用到74LS74中的1号触发器。

由其功能表可知,当CP端接入时钟,和端接入高电平,D端接入输入信号时,在每个时钟的下降沿时刻输出Q都输出与输入D相同的电平,而输出相反的电平。

输入

输出

CP

D

清零

×

0

1

×

0

1

置“1”

×

1

0

×

1

0

送“0”

↑

1

1

0

0

1

送“1”

↑

1

1

1

1

0

保持

0

1

1

×

保持

不允许

×

0

0

×

不确定

表2.474LS74功能表

由于D触发器的输出端只在时钟的上升沿变化,而其他时刻保持上一次的电平,故可以用其构成防颤抖电路,在校分电路中有其应用。

图2.13校分电路

其中输出端直接与分计时器的个位时钟端相连接。

正常计时状态下,开关连接高电平,此时Q端输出高电平,总输出端的信号与秒的十位进位信号相同。

当开关连接低电平时,Q端输出低电平,总输出端输出信号为2Hz的时钟信号。

此电路防颤抖的原理在于:

当开关在两种状态之间转换时,由于机械振动,在很短的时间中(常为几毫秒)会在高低电平之间来回波动,相应的产生几个上升沿。

如果直接将开关的输出端直接连接至分个位的时钟的话,这些上升沿将导致它瞬间跳变几个数值。

然而在加上D触发器之后,由于在没有时钟上升沿的时候,输出信号保持,而其时钟频率相对与颤抖频率是很小的,也就是说在开关颤抖过程中触发器的输出是不变的,从而避免了分计数器数值的跳变。

2.674LS00、74LS20、74LS21集成电路

47LS00是一种十分常见的集成电路,其中集成了4个与非门。

其引脚图如下:

图2.1474LS00引脚图

74LS20同样是一种与非门集成电路,与74LS00不同的是它的每个与非门有4个输入端。

其引脚图如下:

图2.1574LS20引脚图

74LS20是一种4输入与门集成电路,其引脚图如下:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 电工 综合 实验

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《巴黎圣母院》3000字读书心得范文.docx

《巴黎圣母院》3000字读书心得范文.docx

感恩于心-励志笃行--大学生感恩励志教育主题班会PPTPPT推荐.pptx

感恩于心-励志笃行--大学生感恩励志教育主题班会PPTPPT推荐.pptx