JK触发器的设计.docx

JK触发器的设计.docx

- 文档编号:23571373

- 上传时间:2023-05-18

- 格式:DOCX

- 页数:14

- 大小:1.27MB

JK触发器的设计.docx

《JK触发器的设计.docx》由会员分享,可在线阅读,更多相关《JK触发器的设计.docx(14页珍藏版)》请在冰豆网上搜索。

JK触发器的设计

JK触发器的设计

一、JK触发器的组成

在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态,把这种在时钟信号触发时才能动作的存储单元电路称为触发器。

触发器是边沿触发工作,即只有在上升沿或者是下降沿到来时才会改变内部与输出的电平。

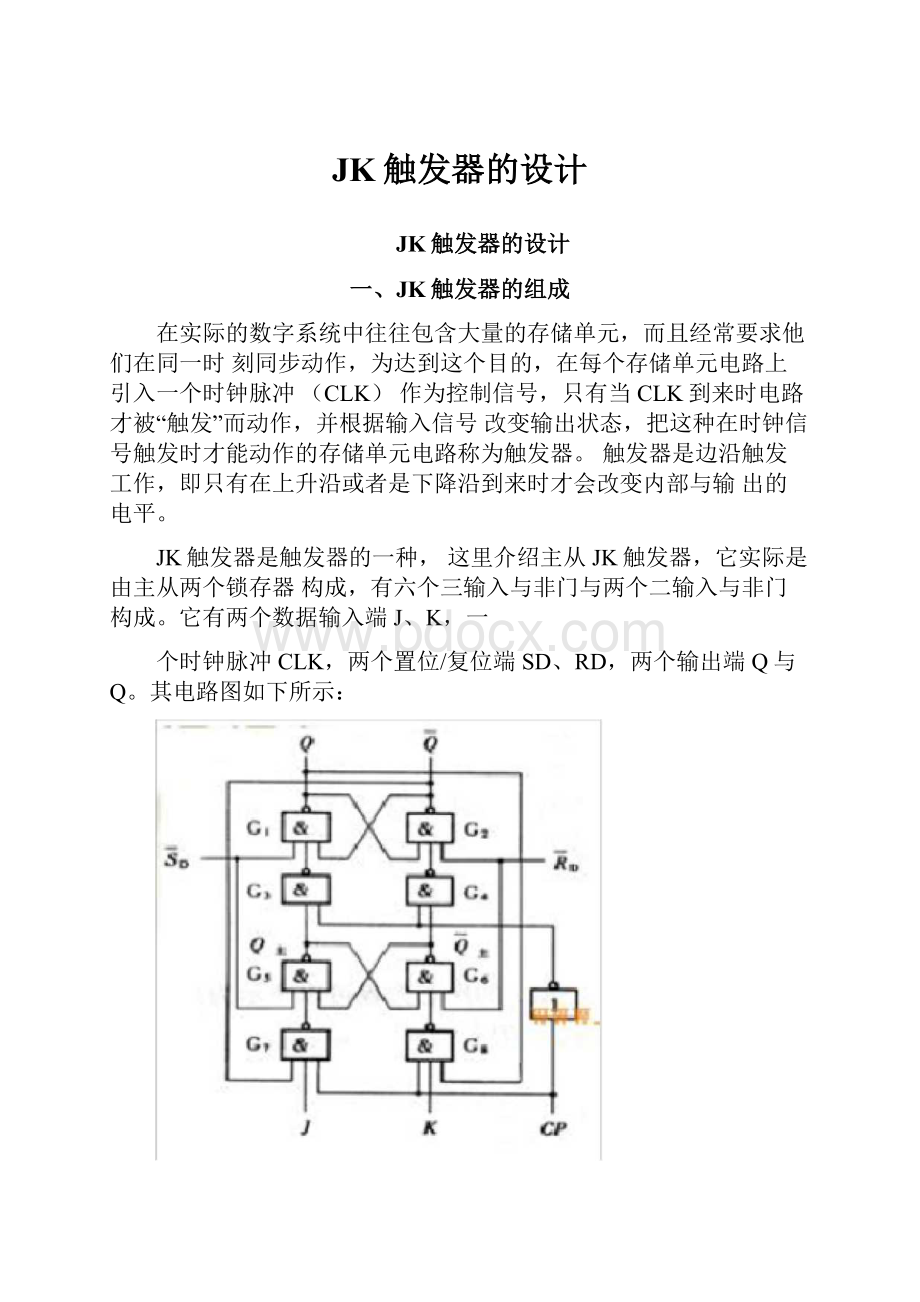

JK触发器是触发器的一种,这里介绍主从JK触发器,它实际是由主从两个锁存器构成,有六个三输入与非门与两个二输入与非门构成。

它有两个数据输入端J、K,一

个时钟脉冲CLK,两个置位/复位端SD、RD,两个输出端Q与Q。

其电路图如下所示:

JK触发器的特性方程为:

QJQ(o)KQ(o)

二、JK触发器的工作原理

如上原理图所示:

Rd与SD为置位/复位控制端,由于用的是与非门,置位

与复位控制端为低电平有效。

当SD=0,Rd=1时,置位端有效,Q1,Q0,输出置1;当SD=1,Rd=0时,复位端有效,Q0,Q1,输出端置1;当SD=1,Rd=1时,置位与复位端都不起作用,触发器正常工作。

CLK为时钟脉冲,主锁存器是高电平跳变,当CLK=1时,Q主随着输入信号JK的变化而变化,而当

CLK=0时,主锁存器被锁定,Q主的值不发生变化;从锁存器是低电平跳变,当

CLK=1时,从锁存器锁定,Q的值不发生变化,当CLK=O时,锁存器开启,Q

的值随着Q主值得变化而变化。

因此对于触发器来说,只有当CLK的值由高电平

变为低电平的时候(即CLK的下降沿),触发器被触发,Q的值会发生变化。

而

对于锁存器,当J=K=1时,锁存器发生翻转;当J=1,K=0时,锁存器置1;当

J=0,K=1时,锁存器置0;当J=K=0时,触发器的状态保持不变。

根据上述工作原理,我们可以列出JK触发器的真值表:

RD

CLK

J

K

Q(0)

Q(0)

Q

Q

0

1

X

X

X

X

X

1

0

1

0

X

X

X

X

X

0

1

1

1

0

0

0

1

r0

1

1

1

0

0

1

0

1

0

1

11

0

1

0

1

0

1

1

1

0

1

1

0

r0

1

1

1

1

0

0

1

1

0

1

1

1

0

1

0

r1

0

1

1

1

1

0

1

1

0

1

1

1

1

1

0

0

1

1

1

X

X

0

1

:

0

1

1

1

X

X

1

0

1

0

由以上真值表可以求得:

当置位/复位端都为1,时钟脉冲为下降沿时,QJQ(0)KQ(0);

当置位/复位端都为1,始终冒充为上升沿时,QQ(0)对真值表进行简化,如下:

SD

RD

CLK

J

K

Q

Q

功能

0

1

X

X

X

1

0

置1

1

0

X

X

X

0

1

置0

1

1

0

0

Q(0)

Q(0)

保持

1

1

0

1

0

1

置0

1

1

1

0

1

0

置1

1

1

1

1

Q(0)

Q(0)

翻转

1

1

T

X

X

Q(0)

Q(0)

保持

三、JK触发器的设计

由于该JK触发器由六个三输入与非门、两个二输入与非门和一个反相器组成,因此可以采取模块化设计方法,先创建三输入与非门、二输入与非门和反相器的原理图和版图,然后通过调用它们的原理图和版图来设计JK触发器。

1)JK触发器原理图的创建

首先来创建JK触发器的原理。

先创建三输入与非门的原理图与symbol,如下所示:

接着创建二输入与非门的原理图与symbol:

创建反相器的原理图与symbol:

然后通过调用反相器、二输入与非门和三输入与非门的symbol来创建JK触发器的原理图。

红色方框中为主锁存器,在CLK为高电平时跳变;蓝色方框中为从锁存器,由于其时钟脉冲前加了一个反相器,它是在CLK为低电平时跳变。

创建JK触发器的symbol,以便搭建仿真测试电路:

2)JK触发器版图的创建

JK触发器版图的创建与原理图创建一样,也采取模块化设计原则先创建三输入与非门的版图,如下左图所示:

aiezm

接着创建二输入与非门的版图,如上右图所示:

创建反相器的版图,如下所示:

JK触发

最后通过调用三输入与非门、二输入与非门和反相器的版图来生成器的版图,如下所示:

对JK触发器的版图进行DRC验证,结果如下:

vit?

!

—師国」:

・■;*,:

;rr^TFn•啊・俯L»JI

Hrp

BuUFiLerst^naw:

^ncAiitfl/tciiniiifZDlW/jcaiuGaljbca.dxc^3.J.±3neIbLderaSJiLyjyu=L£s>30%<£D%

对JK触发器的版图进行LVS验证,结果如下:

对JK触发器的版图进行PEX验证,结果如下:

3)JK触发器的仿真验证

对JK触发器的功能进行仿真验证。

首先创建一个仿真电路图,如下图所示

Jktriocsr

SOUCRE所接电源为5V直流信号,S_,D_,J,K,CLK所接电源分别为

周期为30us、40us、1us、7us、8us的0~5V的方波信号,设置好仿真环境,对

输入端S_、D_、J、K、CLK和输出端Q、Q_进行瞬态仿真。

仿真波形如下所示:

图中由上到下七个波形分别为S_、R_、CLK、J、K、Q、Q_,对图中波形进行分析。

对于S_与D_,S_=1,D_=1时,输出Q与QJ!

J、K信号的变化而变化;当S_=0,D_=1时,Q=1,Q_=0,直接置1,J、K信号无效;当S_=1,D_=0时,Q=0,Q_=1,直接置0,J、K信号无效;当S_=0,D_=0时,Q=1,Q_=1。

J、K无效,此时Q与Q_电位并不是相反。

除了S_、R_均为0的情况外,S_、R_端的功能与真值表中的描述完全一致,而由JK触发器的电路图可以退出S_、R_均为0时,Q与Q_的输出都为1。

将上图中中S_、R_均为1时,CLK、J、K、Q、Q_的图形进行放大可以得到下图。

由上图可以分析触发器中输入端J、K的作用,显然由上图分析可得,J=1,K=1时,实现翻转功能;J=1,K=0时,实现置位(置1)的功能;J=0,K=1时,实现复位(置0)的功能;J=0看,K=0时,则输出情况保持不变。

显然波形图与真值表中J、K的功能一致。

引入寄生参数,对JK触发器进行后仿真,结果如下

左侧为前仿真波形,右侧为后仿真波形,前后波形一致

将波形放大来观察前仿真与后仿真延迟时间的差别

r-aicui-riI#r.iii.-

盂i•底0宦应汀二

观察放大后的前后仿真波形图进行对比,前后仿真的延迟时间基本一致

kNil4ariT«iCfM-illkHTMHHH41

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- JK 触发器 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《酒店人力资源管理》教案.docx

《酒店人力资源管理》教案.docx