FPGA实验报告Word格式.docx

FPGA实验报告Word格式.docx

- 文档编号:14554425

- 上传时间:2022-10-23

- 格式:DOCX

- 页数:16

- 大小:198.86KB

FPGA实验报告Word格式.docx

《FPGA实验报告Word格式.docx》由会员分享,可在线阅读,更多相关《FPGA实验报告Word格式.docx(16页珍藏版)》请在冰豆网上搜索。

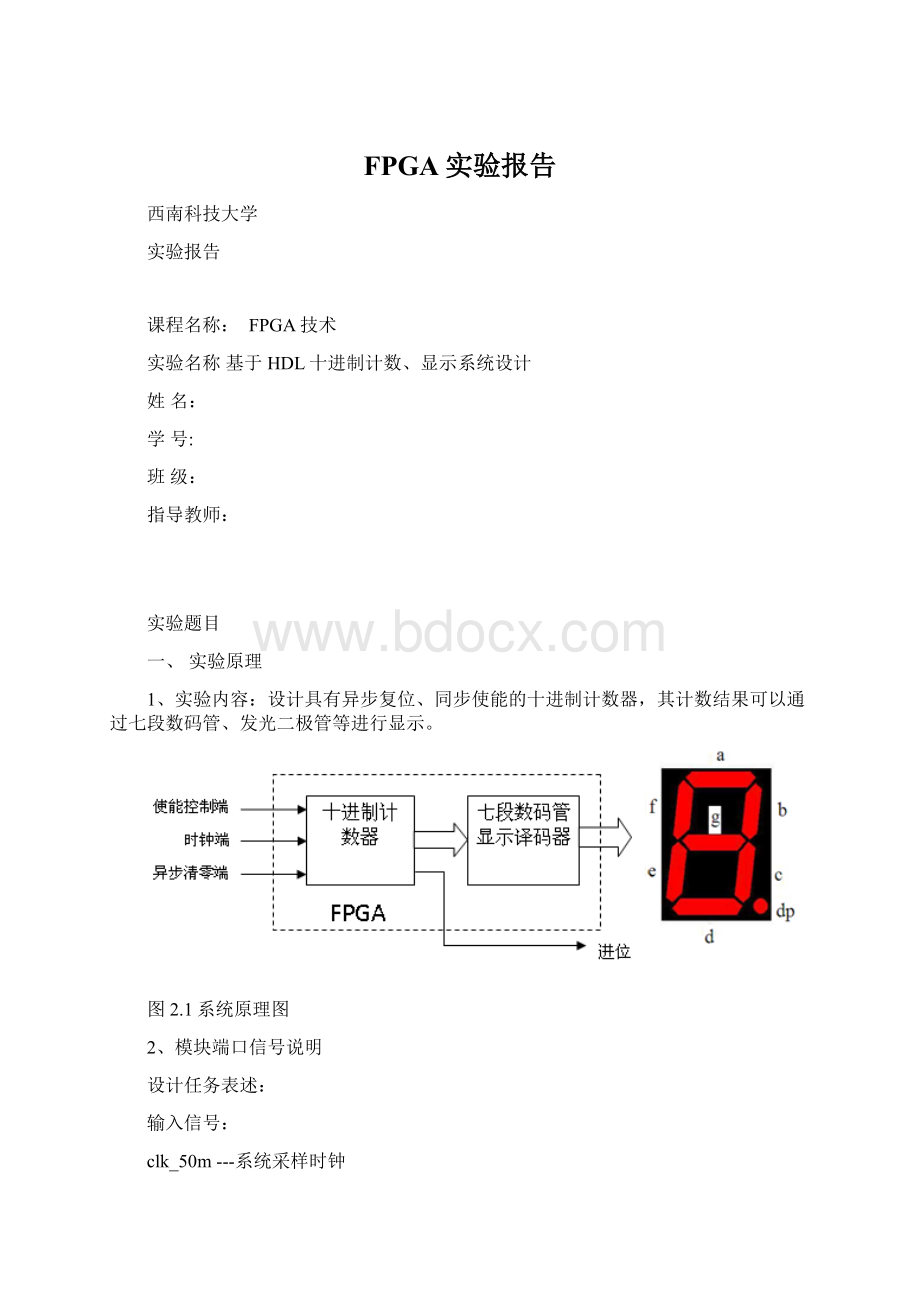

clr---------异步清零信号,当clr=1,输出复位为0,当clr=0,正常计数

ena---------使能控制信号,当ena=1,电路正常累加计数,否则电路不工作

输出信号:

q[6:

0]---------驱动数码管,显示计数值的个位

COM---------共阳级数码管公共端(接地,电路板原理图)

3、以自顶向下的设计思路进行模块划分

整个系统主要设计的模块是:

十进制计数模块和数码管驱动模块,由于实验板的按键为实现硬件防抖,则需要将按键输入的时钟clk,先通过消抖模块消抖后,再输出至后续使用。

图2.2系统模块划分和引脚连线图

由以上分析可知本设计总共包括3个模块:

1)十进制计数器(cnt10.v)模块。

2)驱动七段数码管的模块(led.v)。

3)由于实验板上按键需要进行消抖,所以需要一个消抖模块(debounce_module),待计数的时钟clk输入至计数器前,先通过消抖模块。

1)十进制计数器模块(cnt10.v)实验原理

输入:

CLK-------待计数的时钟

CLR---------异步清零信号,当CLR=1,输出复位为0,当CLR=0,正常计数

ENA---------使能控制信号,当ENA=1,电路正常累加计数,否则电路不工作

输出:

SUM[3:

0]----------计数值的个位。

即,在CLK上升沿检测到SUM=9时,SUM将被置0,开始新一轮的计数。

COUT------------计数值的十位进位,即:

只有在时钟CLK上升沿检测到SUM=9时,COUT将被置1,其余情况下COUT=0。

2)数码管显示驱动模块(led.v)实验原理

输入:

sum[3:

0]-------待显示的数值。

out[6:

0]----------驱动数码管的七位数值(注意下表中out的对应位)。

表2-1共阳极数码管驱动模块输入与输出关系表

注:

这是一个组合逻辑电路,可以考虑用always,或者assign语句设计。

3)消抖模块设计原理

(1)按键抖动产生的原因:

通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。

因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现象而作的措施就是按键消抖。

图2.3按键抖动波形图

(2)消抖模块原理框图简介

图2.4消抖模块框图

电平检查模块:

检测输入的按键是否被按下或者释放,并分别将H2L_Sig,L2H_Sig拉高,

并随后拉低,给出按键的操作信息。

延时模块:

对输入的信号变化时刻进行计时并观察信号的变换情况,对输出端口进行恰

当地赋值。

二、实验步骤

(1)新建一个工程,为工程命名、指定存储路径和目标芯片等。

(在E盘或者DATA盘的根目录下,以自己的学号为文件名建立工程)。

建议工程名、路径名中不要使用中文,file->

NewProject。

(2)选择Top-level的类型是HDL。

(3)做好器件、EDA工具的正确选择,才能使得正常完成锁定引脚、下载的操作。

本次实验中仍采用ISE自带的综合和仿真工具。

图2.5器件和EDA工具选择界面

(4)建立新VerilogHDL模块编辑窗口,分别按照十进制计数器(cnt10.v),数码管驱动模块(led.v)的目标要求进行设计,各模块在综合后,采用波形的方式编辑测试激励波形,对相关模块进行功能仿真,实现模块的验证、修正。

在编辑测试激励文件时,应考虑测试的完备性。

1)、十进制计数器(cnt10.v)程序代码如下:

modulecnt10(CLK,CLR,ENA,COUT,SUM);

inputCLK,CLR,ENA;

output[3:

0]SUM;

outputCOUT;

reg[3:

regCOU;

always@(posedgeCLKorposedgeCLR)begin

if(CLR)

SUM<

=4'

b0000;

elseif(ENA&

&

SUM==4'

d10)

SUM<

4'

=SUM+1'

b1;

end

COUT<

=1'

b0;

else

Endmodule

2)、数码管驱动模块(led.v)的程序代码:

moduleled(IN,OUT);

input[3:

0]IN;

output[6:

0]OUT;

reg[6:

always@(IN)

begin

case(IN)

b0000:

OUT<

=7'

b1000000;

b0001:

b1111001;

b0010:

b0100100;

b0011:

b0110000;

b0100:

b0011001;

b0101:

b0010010;

b0110:

b0000010;

b0111:

b1111000;

b1000:

b0000000;

b1001:

b0010000;

b1010:

b0001000;

b1011:

b0000011;

b1100:

b1000110;

b1101:

b0100001;

b1110:

b0000110;

b1111:

b0001110;

endcase

end

endmodule

(5)用VerilogHDL将cnt10.v和led.v组合为一个模块,完成综合、功能仿真,分形,修正设计。

1)、顶层模块程序代码(cnt10led.v):

`timescale1ns/1ps

modulecnt10led(CLK_50M,CLK,CLR,ENA,COUT,DATA_OUT);

inputCLK_50M,CLK,CLR,ENA;

output[6:

0]DATA_OUT;

wirePin_Out;

wire[3:

0]DATA_IN;

//regCOUT;

debounce_moduleu0(CLK_50M,CLR,CLK,Pin_Out);

cnt10u1(Pin_Out,CLR,ENA,COUT,DATA_IN);

ledu2(DATA_IN,DATA_OUT);

由于本次设计的时钟周期可以较长,系统对时序没有要求,可以省略个子模块的时序仿真。

(6)拷贝消抖模块代码:

debounce_module.v,delay_module.v,detect_module.v,组合完成消抖模块。

1)、detect_module.v程序代码如下:

moduledetect_module(CLK,RSTn,Pin_In,H2L_Sig,L2H_Sig);

inputCLK;

inputRSTn;

inputPin_In;

outputH2L_Sig;

outputL2H_Sig;

parameterT100US=16'

d1999;

reg[10:

0]Count1;

regisEn;

always@(posedgeCLKorposedgeRSTn)

if(RSTn)

Count1<

=11'

d0;

isEn<

=1'

elseif(Count1==T100US)

else

=Count1+1'

regH2L_F1;

regH2L_F2;

regL2H_F1;

regL2H_F2;

if(RSTn)

begin

H2L_F1<

H2L_F2<

L2H_F1<

L2H_F2<

else

=Pin_In;

=H2L_F1;

=L2H_F1;

assignH2L_Sig=isEn?

(H2L_F2&

!

H2L_F1):

1'

assignL2H_Sig=isEn?

(!

L2H_F2&

L2H_F1):

Endmodule;

2)、delay_module.v程序代码如下:

moduledelay_module(CLK,RSTn,H2L_Sig,L2H_Sig,Pin_Out);

inputH2L_Sig;

inputL2H_Sig;

outputPin_Out;

parameterT1MS=25'

d19_999;

reg[15:

regisCount;

regrPin_Out;

reg[1:

0]i;

=16'

elseif(isCount&

Count1==T1MS)

elseif(isCount)

elseif(!

isCount)

reg[3:

0]Count_MS;

Count_MS<

=4'

elseif(isCount&

=Count_MS+1'

Count_MS<

isCount<

rPin_Out<

i<

=2'

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls