含异步清规和同步使能的加法计数器.docx

含异步清规和同步使能的加法计数器.docx

- 文档编号:30542978

- 上传时间:2023-08-16

- 格式:DOCX

- 页数:19

- 大小:37.99KB

含异步清规和同步使能的加法计数器.docx

《含异步清规和同步使能的加法计数器.docx》由会员分享,可在线阅读,更多相关《含异步清规和同步使能的加法计数器.docx(19页珍藏版)》请在冰豆网上搜索。

含异步清规和同步使能的加法计数器

实验三含异步清零和同步使能的加法计数器

一、实验目的

1、了解二进制计数器的工作原理。

2、进一步熟悉QUARTUSII软件的使用方法和VHDL输入。

3、时钟在编程过程中的作用。

二、实验原理

二进制计数器中应用最多、功能最全的计数器之一,含异步清零和同步使能的加法计数器的具体工作过程如下:

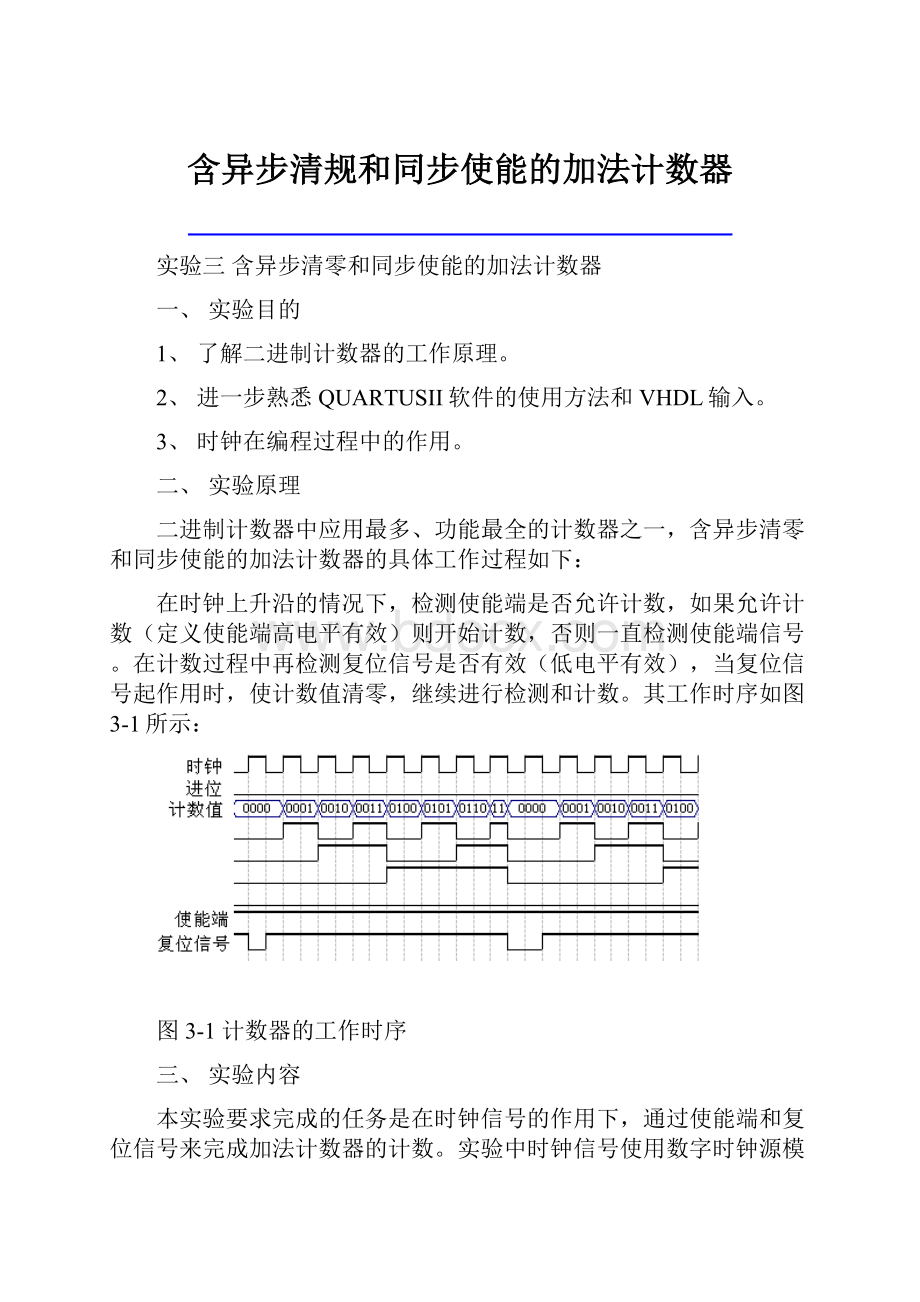

在时钟上升沿的情况下,检测使能端是否允许计数,如果允许计数(定义使能端高电平有效)则开始计数,否则一直检测使能端信号。

在计数过程中再检测复位信号是否有效(低电平有效),当复位信号起作用时,使计数值清零,继续进行检测和计数。

其工作时序如图3-1所示:

图3-1计数器的工作时序

三、实验内容

本实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。

实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用复位开关S1表示复位信号,用LED模块的LED1~LED11来表示计数的二进制结果。

实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。

通过输入不同的值模拟计数器的工作时序,观察计数的结果。

实验箱中的拨动开关、与FPGA的接口电路,LED灯与FPGA的接口电路以及拨动开关、LED与FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

数字时钟信号模块的电路原理如图3-2所示,表3-1是其时钟输出与FPGA的管脚连接表。

图3-2数字时钟信号模块电路原理

信号名称

对应FPGA管脚名

说明

DIGITAL-CLK

A14

数字时钟信号送至FPGA的A14

表3-1数字时钟输出与FPGA的管脚连接表

按键开关模块的电路原理如图3-3所示,表3-2是按键开关的输出与FPGA的管脚连接表。

图3-3按键开关模块电路原理

信号名称

FPGAI/O名称

核心板接口管脚号

功能说明

S[0]

Pin_AF5

JP1_91

‘S1’Switch

S[1]

Pin_AH6

JP1_93

‘S2’Switch

S[2]

Pin_AH7

JP1_95

‘S3’Switch

S[3]

Pin_AH8

JP1_97

‘S4’Switch

S[4]

Pin_AG10

JP1_99

‘S5’Switch

S[5]

Pin_AG11

JP1_101

‘S6’Switch

S[6]

Pin_AH14

JP1_90

‘S7’Switch

S[7]

Pin_AG7

JP1_92

‘S8’Switch

S[8]

Pin_AG8

JP1_94

‘S9’Switch

S[9]

Pin_AF9

JP1_96

‘S10’Switch

S[10]

Pin_AH10

JP1_98

‘S11’Switch

S[11]

Pin_AH11

JP1_100

‘S12’Switch

表3-2按键开关与FPGA的管脚连接表

四、实验步骤

1、打开QUARTUSII软件,新建一个工程。

2、建完工程之后,再新建一个VHDLFile,打开VHDL编辑器对话框。

3、按照实验原理和自己的想法,在VHDL编辑窗口编写VHDL程序,用户可参照光盘中提供的示例程序。

4、编写完VHDL程序后,保存起来。

方法同实验一。

5、对自己编写的VHDL程序进行编译并仿真,对程序的错误进行修改。

6、编译仿真无误后,依照拨动开关、LED与FPGA的管脚连接表(表1-1、表1-2)或参照附录进行管脚分配。

表3-3是示例程序的管脚分配表。

分配完成后,再进行全编译一次,以使管脚分配生效。

端口名

使用模块信号

对应FPGA管脚

说明

CLK

数字信号源

Pin_A14

时钟为1HZ

EN

拨动开关K1

Pin_AH12

使能信号

RET

按键开关S1

Pin_AF5

复位信号

CQ0

LED灯LED1

Pin_AE8

计数输出

CQ1

LED灯LED2

Pin_J22

CQ2

LED灯LED3

Pin_M24

CQ3

LED灯LED4

Pin_L24

CQ4

LED灯LED5

Pin_L23

CQ5

LED灯LED6

Pin_H23

CQ6

LED灯LED7

Pin_H24

CQ7

LED灯LED8

Pin_F24

CQ8

LED灯LED9

Pin_E24

CQ9

LED灯LED10

Pin_F22

CQ10

LED灯LED11

Pin_E22

COUT

LED灯LED12

Pin_F21

COUT为进位信号

表3-3端口管脚分配表

7、用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。

观察实验结果是否与自己的编程思想一致。

五、实验现象与结果

以设计的参考示例为例,当设计文件加载到目标器件后,将数字信号源的时钟选择为1HZ,使拨动开关K1置为高电平(使拨动开关向上),四位LED会按照实验原理中依次被点亮,当加法器加到9时,LED12(进位信号)被点亮。

当复位键(按键开关的S1键)按下后,计数被清零。

如果拨动开关K1置为低电平(拨动开关向下)则加法器不工作。

六、实验报告

1、绘出仿真波形,并作说明。

2、写出在VHDL编程过程中需要说明的规则。

3、将实验原理、设计过程、编译仿真波形和分析结果、硬件测试结果记录下来。

4、改变时钟频率,看实验现象会有什么改变,试解释这一现象。

附表一:

核心板上资源模块与FPGA的管脚连接表

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

核心板模块

FLASH(AM29LV065D)

A0

AF27

A17

T25

A1

AE28

A18

AB27

A2

AE27

A19

V26

A3

AD28

A20

U25

A4

AD27

A21

Y25

A5

AC28

A22

R27

A6

AC27

D0

AC26

A7

AB28

D1

AB25

A8

W28

D2

AB26

A9

W27

D3

AA25

A10

U26

D4

W25

A11

V28

D5

Y26

A12

V27

D6

V25

A13

U28

D7

W26

A14

U27

WE#

AA26

A15

T26

OE#

AC25

A16

R28

CS#

AD26

核心板模块

SRAM(IDT74V416)

A0

AE27

A7

W27

A1

AD28

A8

U26

A2

AD27

A9

V28

A3

AC28

A10

V27

A4

AC27

A11

U28

A5

AB28

A12

U27

A6

W28

A13

T26

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

核心板模块

SRAM(IDT74V416)

A14

R28

D18

N26

A15

T25

D19

P27

A16

AB27

D20

P28

A17

V26

D21

T22

D0

AC26

D22

T21

D1

AB25

D23

R24

D2

AB26

D24

L28

D3

AA25

D25

L27

D4

W25

D26

K28

D5

Y26

D27

K27

D6

V25

D28

H26

D7

W26

D29

G28

D8

AA22

D30

G27

D9

AA24

D31

F28

D10

Y24

BE0

R25

D11

Y23

BE1

AB23

D12

V24

BE2

E28

D13

V23

BE3

F27

D14

U24

OE#

R26

D15

U23

WE#

AB24

D16

M27

CS#

AC24

D17

M28

------

------

核心板模块

串行接口

PC-TXD

D3

PC-RXD

B15

核心板模块

自定义按键

BT1

Y27

BT3

J28

BT2

Y28

BT4

J27

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

核心板模块

七段码LED

A

AF4

E

AF7

B

AE5

F

AD5

C

AE6

G

AF6

D

AF8

DP

AE7

核心板模块

自定义LED(LED1-LED4)

LED1

AF10

LED3

AB9

LED2

AE10

LED4

AE9

核心板模块

NANDFLASH

NF-D0

V4

NF-CLE

T4

NF-D1

W3

NF-ALE

R5

NF-D2

U4

NF-R/B

J1

NF-D3

V3

NF-WE

U3

NF-D4

R4

NF-RE

M3

NF-D5

R3

NF-CE

M4

NF-D6

N4

------

------

NF-D7

N3

------

------

核心板模块

复位按键、时钟

RESET

A15

50MHZ

J2

核心板模块

USB2.0接口

USB-DB0

A26

USB-DB8

A18

USB-DB1

B25

USB-DB9

B17

USB-DB2

A25

USB-DB10

C16

USB-DB3

C24

USB-DB11

A17

USB-DB4

B23

USB-DB12

G25

USB-DB5

A23

USB-DB13

E27

USB-DB6

B22

USB-DB14

D28

USB-DB7

A22

USB-DB15

D27

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

核心板模块

USB2.0接口

USB-FLAGA

B21

USB-CS

B18

USB-FLAGB

A21

USB-OE

C27

USB-FLAGC

C20

USB-WE

B26

USB-ADR0

B19

USB-IFCLK

G26

USB-ADR1

A19

------

------

核心板模块

DDRIISDRAM

DRAM-DQ[0]

AE25

DRAM-ADDR[0]

AC21

DRAM-DQ[1]

AE21

DRAM-ADDR[1]

AB16

DRAM-DQ[2]

AG26

DRAM-ADDR[2]

AC15

DRAM-DQ[3]

AD18

DRAM-ADDR[3]

AF16

DRAM-DQ[4]

AF20

DRAM-ADDR[4]

AD21

DRAM-DQ[5]

AH25

DRAM-ADDR[5]

AE15

DRAM-DQ[6]

AF22

DRAM-ADDR[6]

AD15

DRAM-DQ[7]

AE24

DRAM-ADDR[7]

AE16

DRAM-DQ[8]

AH22

DRAM-ADDR[8]

AC17

DRAM-DQ[9]

AG21

DRAM-ADDR[9]

AF21

DRAM-DQ[10]

AF24

DRAM-ADDR[10]

AE17

DRAM-DQ[11]

AD17

DRAM-ADDR[11]

AE20

DRAM-DQ[12]

AE19

DRAM-ADDR[12]

AF15

DRAM-DQ[13]

AH23

DRAM_BA[0]

AH17

DRAM-DQ[14]

AH21

DRAM_BA[1]

AF17

DRAM-DQ[15]

AG22

DRAM_DM[0]

AF25

DRAM_nCLK

AE23

DRAM_DM[1]

AH19

DRAM_nCAS

AH26

DRAM_DQS[0]

AF26

DRAM_nRAS

AE22

DRAM_DQS[1]

AE18

DRAM_WE

AH18

DRAM_CKE

AG18

DRAM_nCS

AG23

DRAM_CLK

AF23

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

核心板模块

SD卡模块

SD-CS

D4

SD-WP

D6

SD-CLK

C5

SD-DI

D5

SD-CD

C7

SD-DO

C6

核心板模块

扩展接口(EXT-PORT)

1-2

5V(VCC)

23

AG6

3-4

GND

24

AF5

5-6

3.3V

25

AG7

7

AA3

26

AH6

8

W1

27

AG8

9

AB1

28

AH7

10

AB2

29

AF9

11

AC1

30

AH8

12

AC2

31

AH10

13

AD1

32

AG10

14

AD2

33

AH11

15

AE1

34

AG11

16

AE2

35

AH12

17

AF3

36

AF12

18

AF2

37

AF14

19

AH3

38

AG12

20

AG3

39

AG14(CLK15)

21

AH4

40

AH14(CLK14)

22

AG4

------

------

附表二:

系统板上资源模块与FPGA的管脚连接表

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

EDA/SOPC开发平台

16位色彩色液晶显示模块

D0

B11

D11

F3

D1

A10

D12

F5

D2

B10

D13

E3

D3

B8

D14

B12

D4

A8

D15

A12

D5

C8

A0

H4

D6

A7

A1

G5

D7

A11

A2

J3

D8

C12

CS

K4

D9

G3

RD

J4

D10

G4

WR

K3

EDA/SOPC开发平台

7843触摸屏控制模块

DCLK

H13

芯片信号DOUT

E4

CS

G6

PENIRQ

L3

芯片信号DIN

L4

EDA/SOPC开发平台

12位LED灯显示模块

LED1

AE8

LED7

H24

LED2

J22

LED8

F24

LED3

M24

LED9

E24

LED4

L24

LED10

F22

LED5

L23

LED11

E22

LED6

H23

LED12

F21

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

AEEDA/SOPC开发平台

八位七段数码管显示模块

A

G16

G

G12

B

G17

DP

M21

C

F18

SEL0

C22

D

G18

SEL1

D22

E

G15

SEL2

G9

F

G14

EDA/SOPC开发平台

16*16点阵显示模块

R0

C17

R10

D20

R1

D15

R11

D19

R2

D14

R12

C19

R3

D13

R13

D18

R4

D12

R14

C18

R5

D10

R15

D17

R6

C10

C0

L5

R7

C9

C1

H6

R8

D21

C2

H7

R9

C21

C3

H5

EDA/SOPC开发平台

12位拨动开关

K1

AH12

K7

AF12

K2

AF14

K8

AG12

K3

AA8

K9

AA10

K4

AB8

K10

U8

K5

AE4

K11

AE3

K6

AC5

K12

AD4

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

EDA/SOPC开发平台

12位按键开关模块

S1

AF5

S7

AH14

S2

AH6

S8

AG7

S3

AH7

S9

AG8

S4

AH8

S10

AF9

S5

AG10

S11

AH10

S6

AG11

S12

AH11

EDA/SOPC开发平台

4*4钜阵键盘

C0

AD11

R0

AE13

C1

AD12

R1

AE12

C2

AF13

R2

AF11

C3

AE14

R3

AE11

EDA/SOPC开发平台

COM串行接口

RXD

AG14

TXD

AA3

EDA/SOPC开发平台

PS2键盘接口

CLOCK

P25

DATA

P26

EDA/SOPC开发平台M

PS2鼠标接口

CLOCK

M25

DATA

N25

EDA/SOPC开发平台

USB&USBHOST接口

D0

L25

A0

M26

D1

L26

WR

D25

D2

K25

RD

E26

D3

K26

CS

E25

D4

J26

INT

B14

D5

J25

RESET

C15

D6

F25

USBH_CS

D26

D7

F26

USBH_INT

C25

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

EDA/SOPC开发平台

网络接口模块

NET_INT

C26

NET_SCK

C23

NET-SO

D24

NET_CS

D16

NET_SI

D23

NET_RST

C15

EDA/SOPC开发平台

音频CODEC接口模块

AUDIO_SDIN

D7

AUDIN_DIN

D11

AUDIO_SCLK

D8

AUDIO_DOUT

C14

AUDIO_CS

D9

AUDIO_LRC

C13

AUDIO_BCLK

C11

EDA/SOPC开发平台

SD卡接口模块

CS

D4

DO

C6

CLK

C5

WP

D6

DI

D5

CD

C7

EDA/SOPC开发平台

视频编码模块(ADV7171)

YIN0

E18

RESET

AD3

YIN1

E17

IICSDA

E8

YIN2

W1

IICSCL

F8

YIN3

AB1

VD-PCLK

F12

YIN4

AB2

VD-HS1

E14

YIN5

AC1

VD-VS1

E15

YIN6

AC2

VD-BLANK

F17

YIN7

AD1

EDA/SOPC开发平台

视频解码模块(TVP5150)

YOUT0

AF2

YOUT4

AG4

YOUT1

AH3

YOUT5

AG6

YOUT2

AG3

YOUT6

Y10

YOUT3

AH4

YOUT7

AB7

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

EDA/SOPC开发平台

视频解码模块(TVP5150)

IICSDA

E8

VD_VBLK

AD2

IICSCL

F8

VD-FID

AF3

VD-VS

AE2

VD-PCLK

AC3

VD-HS

AE1

VD_RESET

AD3

EDA/SOPC开发平台

VGA显示模块

R

E18

HS

E14

G

E17

VS

E15

B

W1

EDA/SOPC开发平台

红外通信接口模块

IRDA_TXD

E5

IRDA_RXD

E7

EDA/SOPC开发平台

并行ADC模块

D0

K1

D6

P2

D1

K2

D7

P1

D2

L1

D8

R2

D3

L2

D9

Y2

D4

M1

CH

G2

D5

M2

CLK

H3

EDA/SOPC开发平台

并行DAC模块

D0

AA4

D7

V1

D1

Y3

D8

V2

D2

U6

D9

U1

D3

U5

CH

AC4

D4

T8

CLK

U2

D5

R6

WR

AB4

D6

W2

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

EDA/SOPC开发平台

串行ADC模块

SCLK

R1

CS#

T3

DOUT

Y1

EDA/SOPC开发平台

串行DAC模块

SCLK

E19

CS#

E21

DIN

F19

EDA/SOPC开发平台

RTC实时时钟

RTC_RST

E12

RTC_IO

E11

RTC_CLK

F10

EDA/SOPC开发平台

数字温度传感器模块

DS18B20

E10

EDA/SOPC开发平台

IICEEPROM

IICSDA

E8

IICSCL

F8

EDA/SOPC开发平台

步进电机

STEP_A

M5

STEP_C

U7

STEP_B

T7

STEP_D

Y4

EDA/SOPC开发平台

直流电机

MT_PWM

AB5

MT_SPEED

AB3

EDA/SOPC开发平台

可调数字时钟模块CLK

CLK

A14

24MHz~1Hz,共10个时钟可选

模拟信号源

接AD的内部输入端口

EDA/SOPC开发平台

FPGA外部输入/输出端口

FPGA_INPUT

D5

FPGA_OUTPUT

C5

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

EDA/SOPC开发平台

固定子板扩展接口JP4

1

SPR喇叭输出

29-32

VCC

2

NC

33-35

GND

3-8

GND

36

+12V

9

NC

37-38

GND

10

D8

39

NC

11

D7

40

F15

12

D9

41

F14

13

C11

42

G13

14

D11

43

H25

15

C14

44

F11

16

C13

45

AC11

17

NC

46

AB11

18

D4

47

AD10

19

D5

48

AD8

20

C5

49

AC8

21

C6

50

AD7

22

D6

51

AC7

23

C7

52

AB6

24

NC

53

AB13

25

+12V

54

N21

26

NC

55

NC

27-28

GND

56-60

GND

信号名称

FPGAIO接脚

信号名称

FPGAIO接脚

EDA/SOPC开发平台

自定义扩展接口EXPAND

1

G1

19

E15

2

F2

20

E12

3

F1

21

E11

4

E1

22

F10

5

D2

23

E10

6

D1

24

F12

7

C2

25

AD1

8

B3

26

AC2

9

A3

27

AC1

10

C4

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 异步 清规 同步 加法 计数器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《贝的故事》教案4.docx

《贝的故事》教案4.docx